APB协议

在APB2协议中,定义了set up stage和access stage;

定义两个stage其实就相当于定义两个时钟周期。因为APB的slave通常来说对应peripheral的registers,访问这些slave registers(control,status,write/read data)两个clock cycle就够了。对于status register而言是软件轮询的方式(每次访问同样是两个clock cycle)

下图是一个APB2的读操作的例子, 因为PWRITE=0. Set up stage在T2时刻(因为PSEL=1, PENABLE=0),access stage在T3时刻(因为PSEL=1,PENABLE=1),读数据是在T3时刻返回的。

图: APB2的读时序

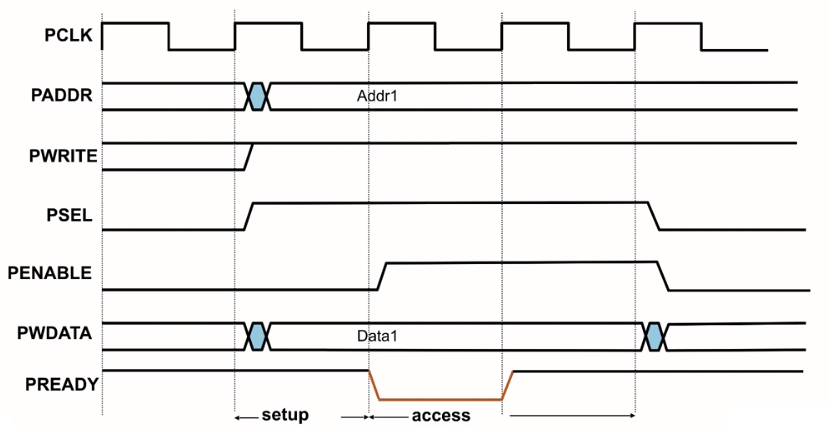

图:APB3的写时序

可以看到PREADY信号中的access是被延长了的,在PREADY为低电平的收,外设没有准备好被写数据,直到PREADY为高的时候,才能够写数据,相应的PSEL和PWDATA都被延长了。

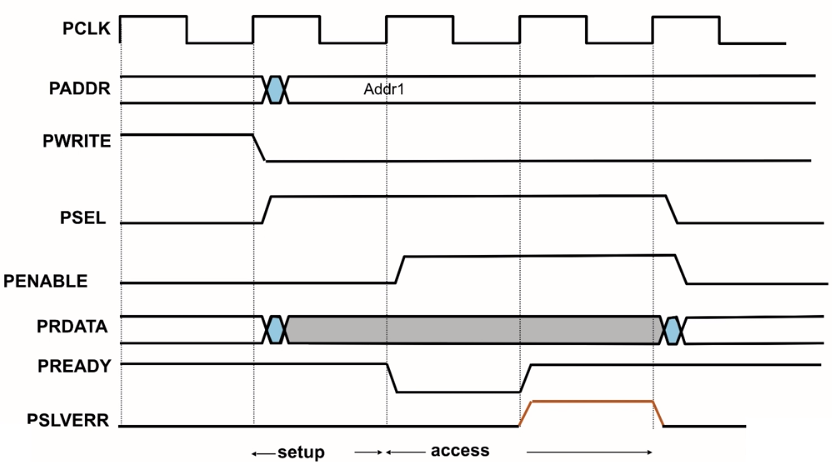

图:APB3的读时序

APB3是有error信号的,在access的最后一个阶段给出,如果有eeror的话,PREADY也PSLVERR都必须为1。对master而言,可以在这几个信号都为1的时候,去采集PSLVERR信号。

APB3相较于APB2多了PREADY和PSLVERR两个信号。上文提到APB2,系统通常是通过软件的方式去轮询Peripheral的status register(两个clock cycle),APB3加了硬件的解决方法,Slave通过PREADY信号直接来告诉master现在Slave已经READY了,可以接受读写操作,如果此时不READY,那么master就要wait到它Ready,这样就不需要软件时刻去轮询status register了。对于PSLVERR而言,加入了Slave反馈给master error response功能。

APB4比APB3多了什么信号PPROT和PSTRB信号。随着架构的不断发展以及对系统安全性的重视,在新的系统中通常会有security的要求,那么APB4也需要演进,PPROT信号主要就是为了表示当前的这个访问/transaction是secure的还是non-secure的,从而和整个系统的security保持一致性。PSTRB的信号的加入,能够使APB对某个byte进行读写操作。因为即使传输的是32位的信号,但是可能只有部分byte是有效的,用PSTRB的每一个bit来代表每个32位中的4个byte哪些是有效的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号