编译和仿真选项:-cm

功能

选项允许用户在 编译(compile)和仿真(simulate)阶段 指定需要收集的覆盖率类型。支持的覆盖率类型包括:

- line:行覆盖率(检查代码行是否被执行)

- cond:条件覆盖率(检查条件语句的所有分支)

- branch:分支覆盖率(类似 cond,但更针对 if-else 结构)

- fsm:状态机覆盖率(分析状态机的状态跳转)

- tgl:信号翻转覆盖率(检查信号位的 0→1 和 1→0 翻转)

- path:路径覆盖率(检查代码中的路径组合)

- assert:断言覆盖率(针对 SystemVerilog Assertions)

- 可通过 + 组合多种覆盖率类型,例如 -cm line+cond+fsm。

使用方法

编译阶段

在编译设计文件和测试平台时,通过 -cm 指定要收集的覆盖率类型:

vcs -cm line+cond+fsm -sverilog design.sv testbench.sv

这里 -cm line+cond+fsm 表示启用行、条件和状态机覆盖率。;可结合其他编译选项(如 -sverilog 支持 SystemVerilog)。

仿真阶段

-cm_dir选项

在运行仿真时,需再次使用 -cm 启用覆盖率收集,并可通过 -cm_dir 指定覆盖率数据存储目录:

./simv -cm line+cond+fsm -cm_dir ./coverage_data

覆盖率数据会默认生成在 simv.cm 目录,或通过 -cm_dir 自定义路径。

-cm_name选项

当对同一个设计进行多次仿真,且希望分别保存和分析每次仿真的覆盖率数据时,-cm_name选项就非常有用。例如,在不同的测试场景或配置下运行仿真,通过为每次运行指定不同的-cm_name,可以将相应的覆盖率信息存储在不同的数据库中,避免混淆。

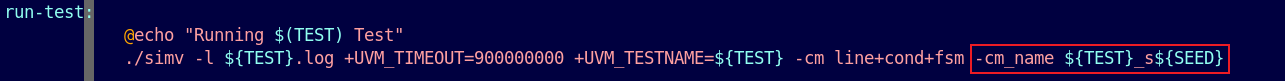

当使用如下的仿真指令时:

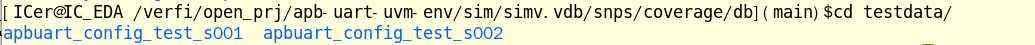

分别指定SEED为001、002后,得到的覆盖率目录为:

可以看到testdata目录下根据仿真的种子号,生成了两个文件夹,分别存放单次仿真的覆盖率结果。

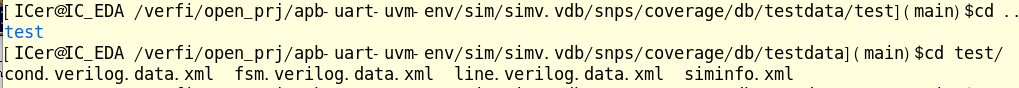

而当不使用-cm_name选项时,testdata中的文件为:

此时testdata下只有test一个文件,test中存放的就是最近一次仿真的覆盖率结果。

由此可见,如果不使用-cm_name参数的话,每次执行仿真,除非你修改-cm_dir后的参数,否则test文件会被覆盖,上一次的覆盖率结果就会丢失

-cm_test选项

豆包介绍如下:

-cm_test 参数用于指定覆盖率收集时所关联的测试用例名称。在硬件验证中,通常会执行多个不同的测试用例来对设计进行全面验证,借助 -cm_test ,就能为每个测试用例分别收集和统计覆盖率信息,这样可以清晰地了解每个测试用例对设计的覆盖情况,进而更有针对性地优化测试用例。

PS:本人还没用过。

生成覆盖率报告

使用 Synopsys 的 urg 工具生成 HTML 格式的覆盖率报告:

urg -dir ./coverage_data -report report_dir

生成的报告位于 report_dir 目录,可通过浏览器查看index.html。

疑问

假如编译时和仿真时使用的-cm项不同,以哪个为准?

浙公网安备 33010602011771号

浙公网安备 33010602011771号