调试寄存器 原理与使用:DR0-DR7

下面介绍的知识性信息来自intel IA-32手册(可以在intel的开发手册或者官方网站查到),提示和补充来自学习调试器实现时的总结。

DRx对应任意的一个调试寄存器。LENn对应任意一个长度。Ln对应任意一个局部置位,DR0-DR7可以直接被读写操作(MOV 指令之类的,DRx可以是源操作数也可以是目的操作数)。但是,DRx的访问是需要一定权限的。比如你用MOV操作的话,你需要在实地址模式,系统管理模式(smm)或者在保护模式(CPL设0).如果权限不够,将会在访问DRx的时候尝产生#GP(general-protection)异常。

DRx可以干些什么?

- 设置发生断点的地址(线性地址)

- 设置断点的长度(1,2,4个字节,但是执行断点只能是1)

- 设置在调试异常产生的地址执行的操作

- 设置断点是否可用

- 在调试异常产生时,调试条件是否是可用

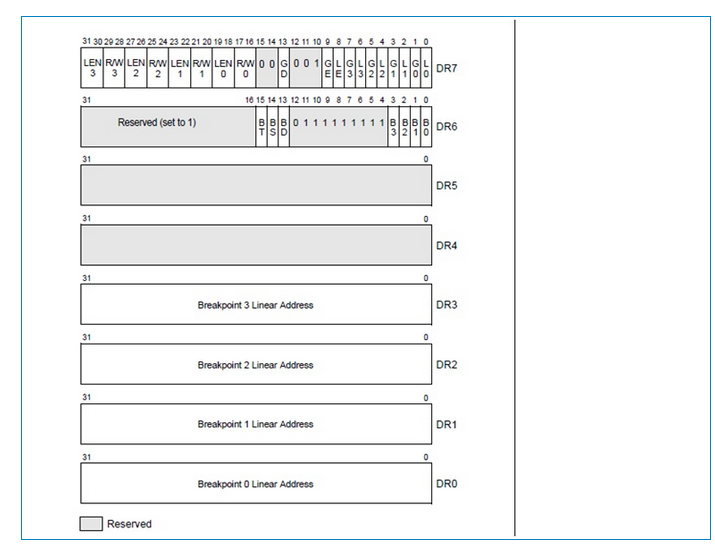

我们来看看调试寄存器的一些细节信息。下图很重要,后面的介绍都是针对这个图说的。

-

调试寄存器 DR0-DR3

这四个寄存器是用来设置 断点地址的。断点的比对在物理地址转换前(异常产生时,还没有将线性地址转换成物理地址)。由于只有0-3四个保存地址的寄存器,所以,硬件断点,在物理上最多只能有4个。 - 调试寄存器DR4-DR5

这两个调试寄存器有CR4的DE标记控制。如果DE置位,那么对这两个寄存器的访问会导致#UD异常。如果DE置0,那么他们就被化名为DR6-DR7(你一定会问原来的DR6-DR7怎么办?这个…… 我也不知道。如果你搞明白了,一定记得告诉我) - 调试寄存器DR7(控制寄存器)

DR7是调试控制寄存器。控制方式嘛!继续看:

1. L0-L3(由第0,2,4,6位控制):对应DR0-DR3,设置断点作用范围,如果被置位,那么将只对当前任务有效。每次异常后,Lx都被清零。

2. G0-G3(由第1,3,5,7位控制):对应DR0-DR3,如果置位,那么所有的任务都有效。每次异常后不会被清零。以确保对所有任务有效。但是,不知道为什么,我在测试时:

设置Gn后,不能返回调试异常给调试器(如果你知道为什么,记得告诉我)

3. LE,GE(由第8,9位控制):这个在P6以下系列CPU上不被支持,在升级版的系列里面:如果被置位,那么cpu将会追踪精确的数据断点。LE是局部的,GE是全局的。(到底什么算精确的,我也不清楚,但是,我知道如果设置了这两个,cpu的速度会降低。我在测试中,都没有置位。)

4. GD(由第13位控制):如果置位,追踪下一条指令是否会访问调试寄存器。如果是,产生异常。在下面的DR6里面,你会知道他还和另外一个标志位有点关系。

5. R/W0-R/W3:(由第16,17,20,21,24,25,28,29位控制):这个东西的处理有两种情况。

如果CR4的DE被置位,那么,他们按照下面的规则处理问题:

00:执行断点

01:数据写入断点

10:I/0读写断点

11:读写断点,读取指令不算

如果DE置0,那么问题会这样处理:

00:执行断点

01:数据写入断点

10:未定义

11:数据读写断点,读取指令不算

6. LEN0-LEN3:(由第18.19.22.23.26.27.30位控制):指定内存操作的大小。

00:1字节(执行断点只能是1字节长)

01:2字节

10:未定义或者是8字节(和cpu的系列有关系)

11:4字节 - 调试寄存器DR6(调试状态寄存器)

这个寄存器主要是在调试异常产生后,报告产生调试异常的相关信息

1.B0-B3(DR0-DR3):DRx指定的断点在满足DR7指定的条件下,产生异常。那么Bx就置位。但是,有时,即使Ln和Gn置0,也可能产生Bx被置位。这种现象可能这样出现(提示:在p6系列处理器,REP MOVS在不断循环中产生的调试异常需要执行完了才能准确返回给调试进程):DR0的L0,G0都置0(DR0就是一个不能产生异常的断点了),然后在DR0指定的地址是一个REP指令的循环,这样,DR0就可能在这个循环之后的REP指令产生的调试异常中将B0置位

2.BD:BD需要DR7的GD置位,才有效。BD是在下一条指令要访问到某一个调试寄存器的时候,被置位的。

3.BS:单步执行模式时,被置位。单步执行是最高权限的调试异常。

4.BT:在任务切换的时候,被置位。但是必须在被切换去的任务的TSS段里面的T标记被置位的情况下才有效。在控制权被切换过去后,在执行指令前,返回调试异常。但是,需要注意,如果调试程序是一个任务,那么T标记的设置肯定就冲突了。然后,导致了死循环(BT的这些信息都是按照官方资料翻译而来,由于没有实际的操作,肯定会有理解上的出入。如果要深入的话,建议看官方资料).有些调试异常会将B0-B3清零。但是其他的DR6的位是不能被产生异常的进程清零的。每次调试异常返回后,调试进程都会先将DR6清零,再按照情况设置。以免产生不必要的错误。

对齐问题和64位处理器

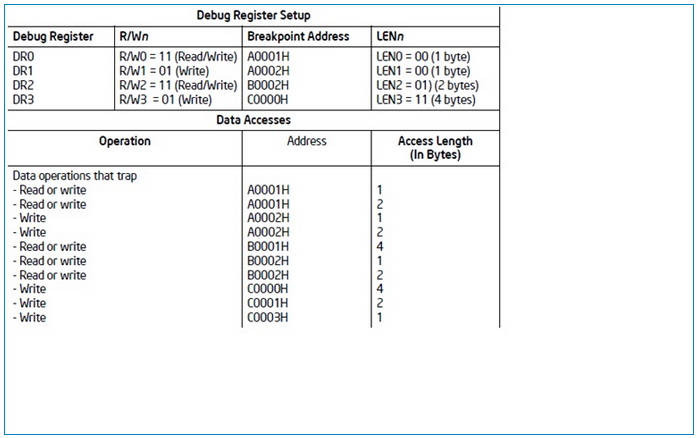

对齐问题

这个问题是来源于LENn的设置,如果设置4字节,那么必须4字节对齐。例如:我们下4字节的断点,那么DRx需要是A0000/A0004/A0008这样的地址上。I/O地址是零扩展的(这个……也许意味着必须完全对齐)。因为,intel在比对地址时:用LENn的值去覆盖DRx里面保存的地址的低位。你可以想到,不对齐会有什么后果了吧。注意:执行断点只能是1字节。

再用图片解释下(当然,图片来自intel官方资料):

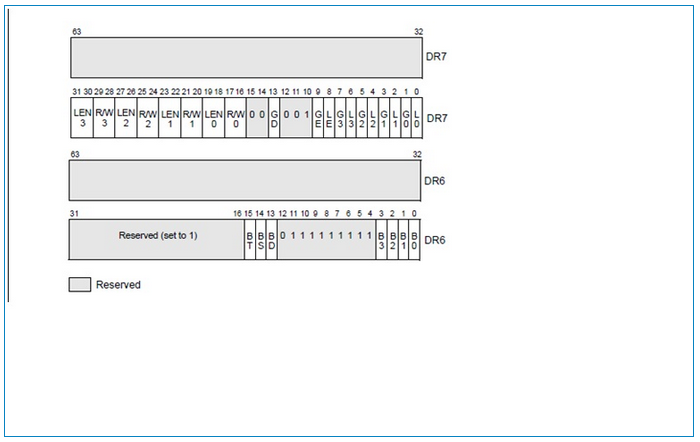

在64位处理器下

调试寄存器当然也是64位的。在操作过程中,写入,前面32位被置零。读取:只返回后32位。MOV DRx操作,前32位被忽略。DR6-DR7的高32位被保留。置零。如果置位,会产生#GP异常。8字节的读写断点完全被支持。最后,还是给个图片(64位处理器的布局):

最后需要提醒一个小问题:数据写入断点设置后。是在原数据被修改后,才产生调试异常。所以,返回异常时,原有数据已经被修改。如果想保留原有数据,需要自己提前保存对应地址的数据。

转自:https://blog.csdn.net/whatday/article/details/8621410

浙公网安备 33010602011771号

浙公网安备 33010602011771号