sv实验1

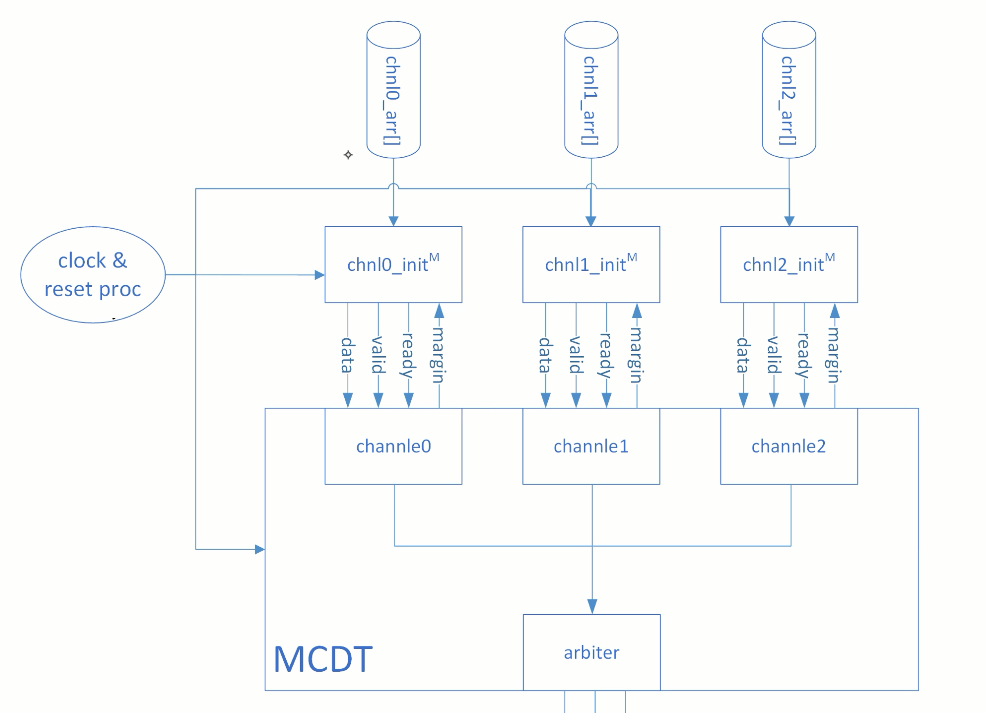

实验框架

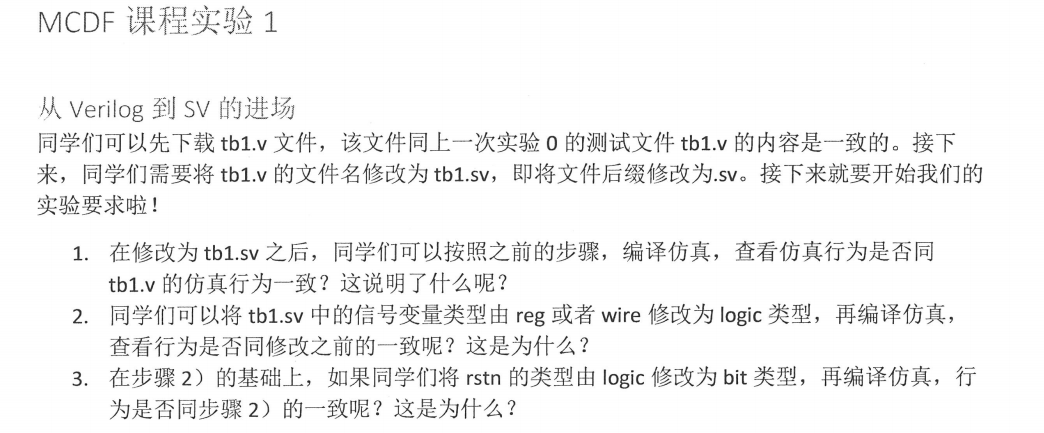

1.从Verilog到sv

1.1-1.2

一致。sv继承于v,所以v的代码可以在sv环境运行;sv并未严格区分reg和wire类型

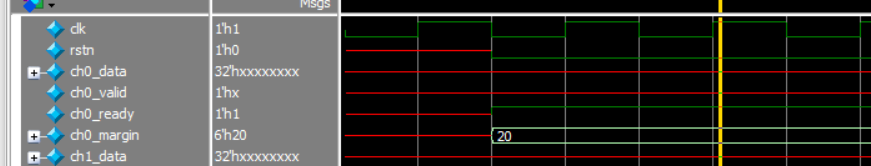

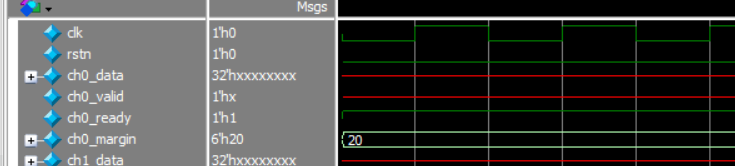

1.3

修改前

修改后

logic类型默认处置为x,而bit类型默认初值为0;

2.方法和函数

2.1-2.5

task clk_gen(input int peroid); int N; N=peroid*0.5; clk <= 0; forever begin #N clk<= !clk; end endtask initial begin // generate clk clk_gen(20); end task rstn_gen(); #10 rstn <= 0; repeat(10) @(posedge clk); rstn <= 1; endtask initial begin // trigger rstn rstn_gen(); end

1.不能,因为没有给clk;2.恢复正常;

3.initial中的task是顺序执行的,而时钟与复位信号要不间断执行,所以不能在一个task里面;

4.可以。5.`timescale 1ns/1ps,1ns指的是时间单位,1ps指的是时间精度,单位改变,周期必定改变

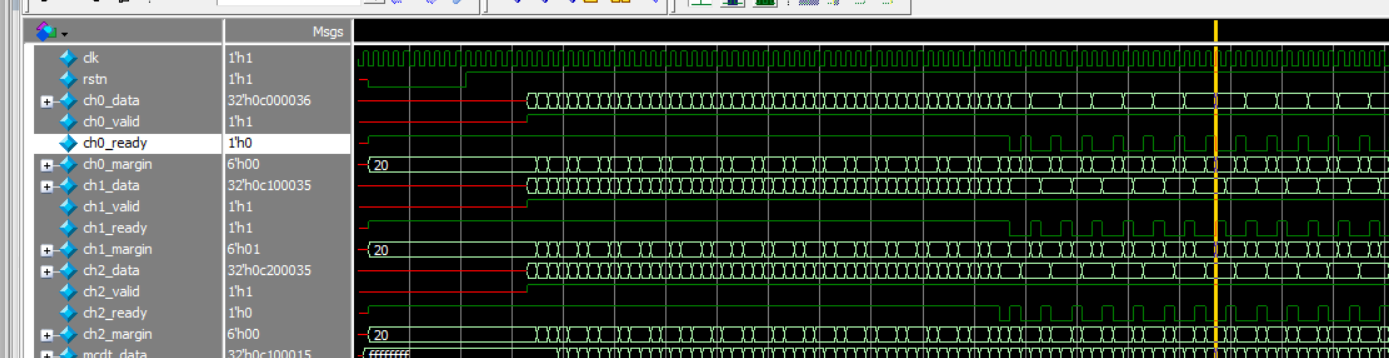

3.数组的使用

logic [31:0] chnl0_arr[]; logic [31:0] chnl1_arr[]; logic [31:0] chnl2_arr[]; initial begin chnl0_arr=new[100]; chnl1_arr=new[100]; chnl2_arr=new[100]; foreach(chnl0_arr[i]) begin chnl0_arr[i] = 'h00C0_00000 + i; chnl1_arr[i] = 'h00C1_00000 + i; chnl2_arr[i] = 'h00C2_00000 + i; end end initial begin @(posedge rstn); repeat(5) @(posedge clk); foreach(chnl0_arr[i]) chnl_write(0,chnl0_arr[i]); foreach(chnl1_arr[i]) chnl_write(1,chnl1_arr[i]); foreach(chnl2_arr[i]) chnl_write(2,chnl2_arr[i]); end

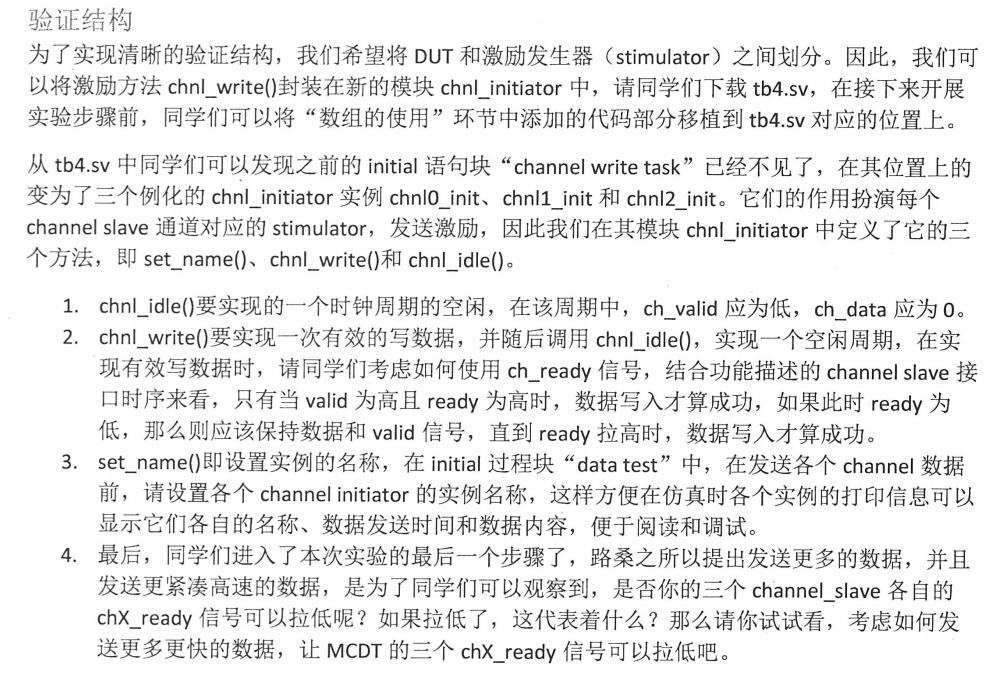

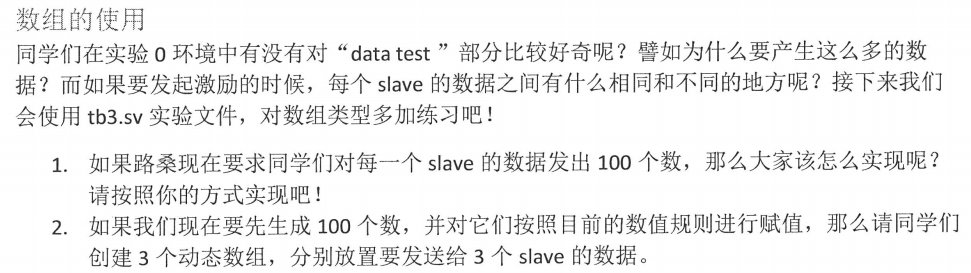

4.验证结构

tb4与tb3最大的不同是把dut和激励发生器单独划分,所以用一个单独的模块initiator来控制数据发送和空闲周期,而数据产生仍交给tb模块完成。同时将三个通道的数据发送分别由三个initial实现三通道并行发送数据。

`timescale 1ns/1ps module chnl_initiator( input clk, input rstn, output logic [31:0] ch_data, output logic ch_valid, input ch_ready, input [ 5:0] ch_margin ); string name; function void set_name(string s); name = s; endfunction task chnl_write(input logic[31:0] data); @(posedge clk); ch_valid <= 1; ch_data <= data; @(negedge clk); wait(ch_ready === 'b1); $display("%t channel initial [%s] sent data %x", $time, name, data); endtask task chnl_idle(); @(posedge clk); ch_valid <= 0; ch_data <= 0; endtask endmodule module tb4; ... ... initial begin @(posedge rstn); repeat(5) @(posedge clk); chnl0_init.set_name("chnl0_init"); foreach(chnl0_arr[i]) chnl0_init.chnl_write(chnl0_arr[i]); chnl0_init.chnl_idle(); end initial begin @(posedge rstn); repeat(5) @(posedge clk); chnl1_init.set_name("chnl1_init"); foreach(chnl1_arr[i]) chnl1_init.chnl_write(chnl1_arr[i]); chnl1_init.chnl_idle(); end initial begin @(posedge rstn); repeat(5) @(posedge clk); chnl2_init.set_name("chnl2_init"); foreach(chnl2_arr[i]) chnl2_init.chnl_write(chnl2_arr[i]); chnl2_init.chnl_idle(); end chnl_initiator chnl0_init( .clk (clk), .rstn (rstn), .ch_data (ch0_data), .ch_valid (ch0_valid), .ch_ready (ch0_ready), .ch_margin(ch0_margin) ); chnl_initiator chnl1_init( .clk (clk), .rstn (rstn), .ch_data (ch1_data), .ch_valid (ch1_valid), .ch_ready (ch1_ready), .ch_margin(ch1_margin) ); chnl_initiator chnl2_init( .clk (clk), .rstn (rstn), .ch_data (ch2_data), .ch_valid (ch2_valid), .ch_ready (ch2_ready), .ch_margin(ch2_margin) ); endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号