如果“西贝”也做FPGA构建

拿现成的半成品再加工,既省时间又保证了口味稳定。就是最近西贝莜面村因为应用预制菜被骂上热搜,大家都知道,餐饮行业现在一个热词就是“预制菜”,很多流程不再从头做,而

其实 FPGA 开发也有点类似,十多年前可能还有很多人从零开始写HDL,也就导致FPGA“难”学的困境,现在谁还从零撸 Verilog/VHDL 啊?更多人早就学会用 IP 核 来“现成加料”,效率直接起飞。

为什么要用 IP 核?

假如用一句话来总结:

别再重复造轮子,把精力放在真正的创新上。

IP 核就像厨房里的预制菜包,别人已经帮你把复杂的工序做好了,你只需要“开袋即用”。优势很明显:

省时间:常见功能不用自己从 RTL 开始写。

省精力:协议栈、DSP 模块这种复杂度极高的东西,使用现成的 IP 核就行。

稳定性高:经过验证的 IP 核 bug 少,可靠性比自己现写强。

可扩展:很多 IP 核支持参数化配置,可以根据需求生成不同规格版本。

常用的几类 IP 核

通讯类

AXI 总线接口:Xilinx/AMD 提供 AXI4、AXI-Lite、AXI-Stream 等。

Ethernet MAC:千兆/万兆以太网,直接接网口,免去自己写协议栈的噩梦。

PCIe 核:协助多 lane、高速传输,移植起来非常省心。

存储与接口类

DDR 控制器:MIG(Memory Interface Generator),几乎必用。

SPI/I2C/UART:嵌入式开发常见接口,IP 核现成可拖拽。

高速串行接口(SerDes):用来跑高速数据传输。

算法类

FFT、FIR、IIR:做信号处理的常用加速器。

DSP Slice 封装 IP:乘加、矩阵运算打包成模块。

图像处理模块:边缘检测、缩放、滤波都有现成 IP。

开源 IP 库推荐

LiteX:基于 Python 的 FPGA SoC 生成框架,自带 UART、Ethernet、DDR 控制器等。

https://github.com/enjoy-digital/litex

OpenCores:老牌开源 IP 仓库,从 CPU 内核到通信接口应有尽有。

https://opencores.org/

VexRiscv:开源 RISC-V CPU 内核,高度可配置,HLS/RTL 计划都能用。

https://github.com/SpinalHDL/VexRiscv

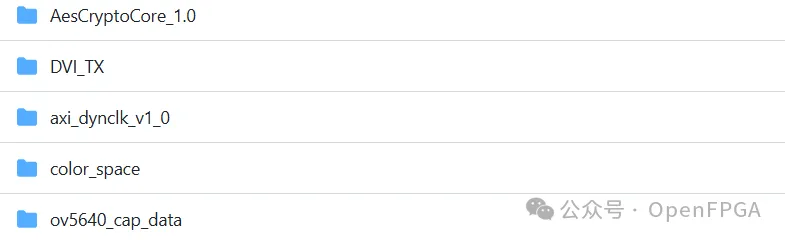

FPGA_Library:该库包括诸多IP,包括图像处理、数字信号处理、接口等。

https://github.com/suisuisi/FPGA_Library

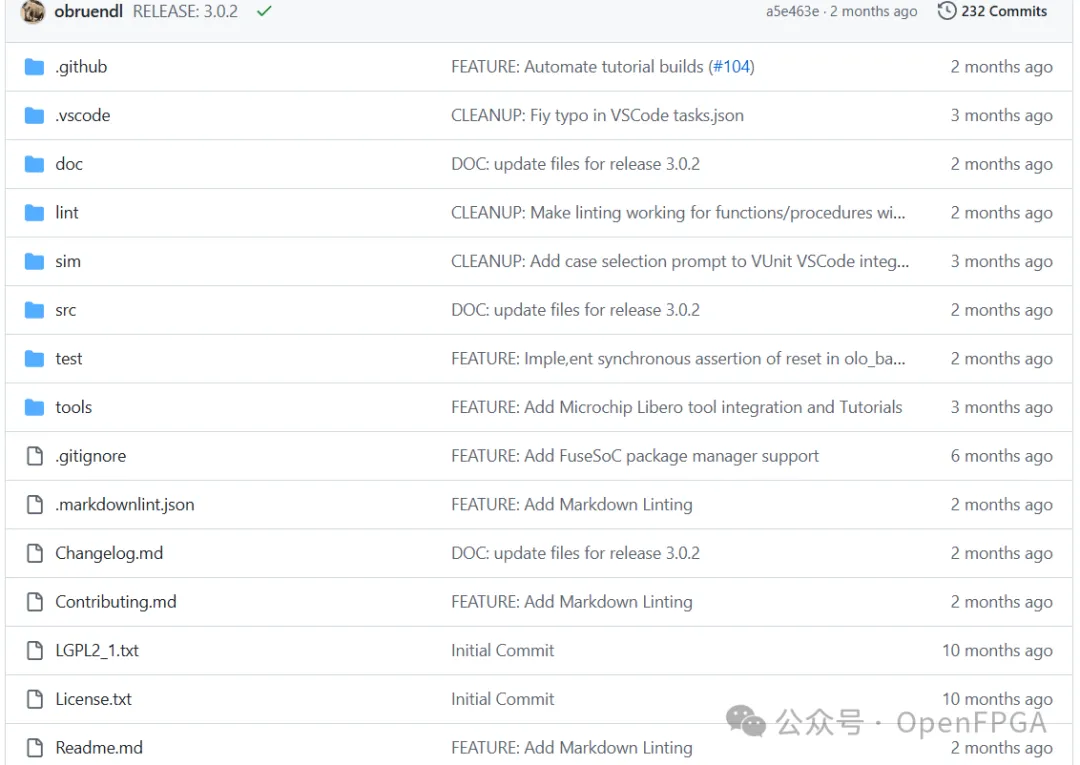

Open Logic:这个开源 VHDL 库给出了各种专注于 IP 外设创建的 IP 核。它给出了用于CDC、内存、FIFO、仲裁器、时分复用和其他功能(如 PRBS、延迟和桶形移位器)的模块。对于 AXI 支持,Open Logic 包括 AXI 主设备、从设备和流水线。它还给予用于 UART、SPI、I2C 等的接口 IP,使其成为 AXI 端点的宝贵资源。

https://github.com/open-logic/open-logic

HDL 模块:该库提供一系列 AXI IP,包括interconnects 和 crossbars,以及 FIFO 等基本基础设施。为了帮助仿真,HDL 模块还包括总线功能模型和通用组件,例如环形缓冲区、LFSR、数学函数和正弦发生器。凭借阅读文档可以很好地了解它。

https://hdl-modules.com/index.html

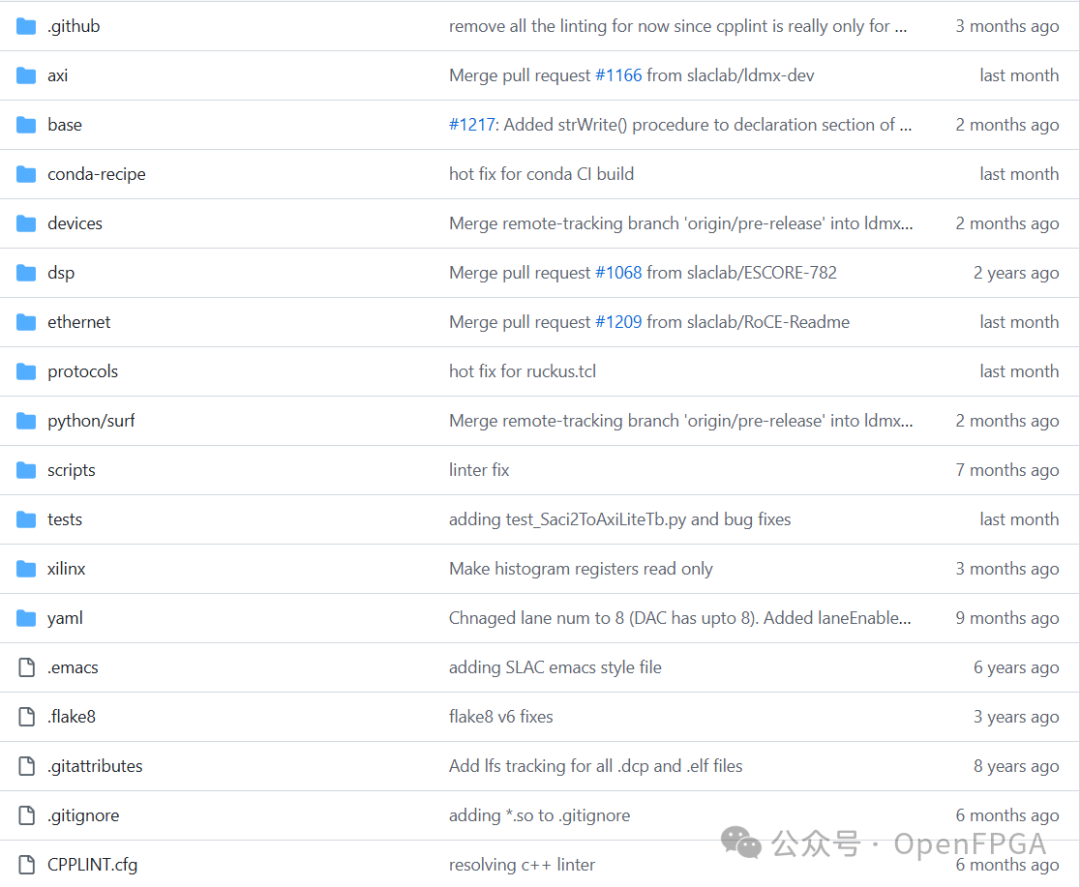

SURF(SLAC 终极 RTL 框架):SURF 提供 AXI、以太网和设备库。设备库特别有用,带有 ADC 和 DAC 等外围设备的驱动程序。SURF 采用 CocoTB 和 GHDL 进行验证,使流程变得容易。

https://github.com/slaclab/surf

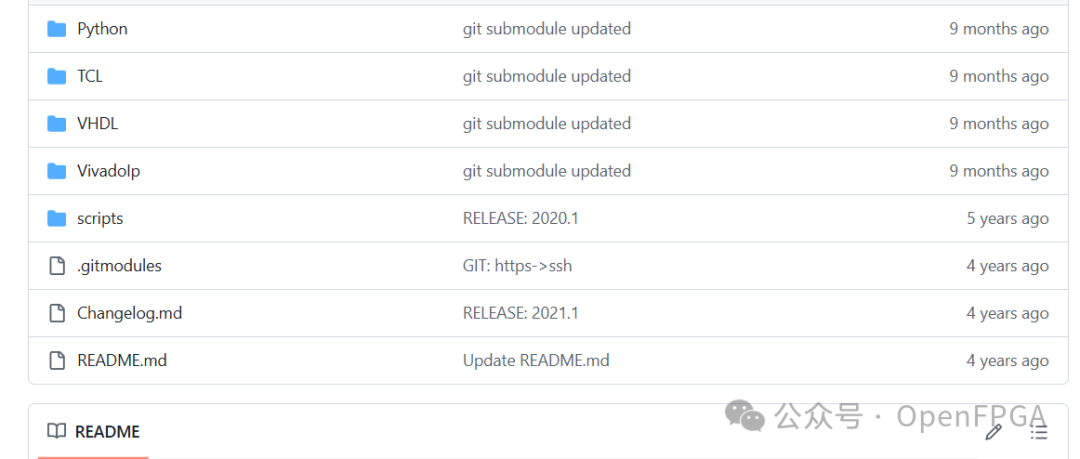

PSI Lib:由 Paul Scherrer 研究所编写,该库提供内存、FIFO、跨时钟域、时分复用、AXI 接口和其他常见模块的 IP 模块。

https://github.com/paulscherrerinstitute/psi_fpga_all

PoC Lib(Pile of Cores):由Technical University of Dresden大学提供,PoC 专注于内存、FIFO 和 I/O 控制器。它利用了 CocoTB、OSVVM、UVVM 和 VUnit 进行验证。

https://github.com/VLSI-EDA/PoC

构建流程的“预制化”

就像餐饮业里预制菜不是为了偷工减料,而是为了 标准化 + 提效率。

:就是FPGA 里的 IP 编写,本质上也

基础功能用成熟 IP 核,保证稳定;

关键差异化功能自己写 RTL,保证独特性;

通过 Block Design 把模块拼装起来,调 AXI 接口就能跑。

这样一来,任务周期会缩短很多,团队也能更快迭代。

小结

未来 FPGA 创建的趋势很明确:

低层重复工作交给 IP 核;

差异化逻辑自己设计;

平台级设计靠拼装 + 调优。

所以说,如果把 FPGA 项目比作做一桌大餐,IP 核就是那些“半成品”,能让你快速上菜;真正决定味道的,还是最后那几道核心的“招牌菜”。

浙公网安备 33010602011771号

浙公网安备 33010602011771号