《数字IC入门》白栎杨阅读笔记第二章 - 教程

写在前面:

- 阅读本章之前,建议提前阅读《1.11节 关于本书描述方法的约定》

- 第一章已阅读完毕。第二章持续阅读中....

第2章 基于Verilog的数字IC设计办法

2.1 数字器件与Verilog语法的关系

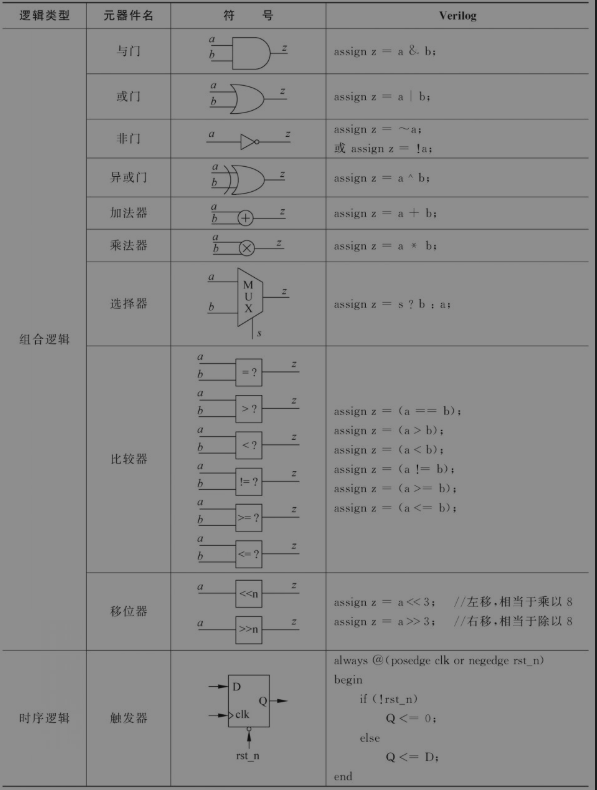

- 10种简单元器件,即与门、或门、非门、异或门、加法器、乘法器、选择器、比较器、移位器、触发器。

- 基本元器件中不包括除法,原因是除法的实现不同于乘法,它受到被除数、除数、商的数值范围的限制,有时需要用到迭代等复杂方法实现,还有分母为0等异常情况需要报告,所以并不属于Verilog中常用的直接运算方式。

- 组合逻辑

- 组合逻辑如果输入含有毛刺,输出就有毛刺。

- 组合逻辑,输出端是无法寄存信息的,必须随输入的变化而立即发生变化。

- 时序

- 时序逻辑能够消除毛刺

- 触发器也可称为寄存器(Register,reg)。之所以叫寄存器是因为若是没有时钟驱动,则Q端会保持原有状态不变,也就寄存了上一次触发时的D端信息

- 触发器图形中的圆圈表示0电平有效,即rst_n等于0时,寄存器处于复位状态。

2.2 可综合的Verilog设计语法

- 能变成电路的Verilog表达叫作可综合

- 在设计电路时,只能使用可综合的语法表述

- 而在仿真时,由于只在计算机上运行,不流片,可使用不能综合的高级语法,以增加语言表达的灵活度和复杂度。

- 可综合语法中,常用的电路表述只有两种,一种assign,另一种是always

- always块不仅可以用来表示时序逻辑,也可以用来表示组合逻辑

- 时序always@(posedge clk or negedge rst_n)

- @括号中的列表叫敏感列表,意思是always块输出的Q对列表中的信号保持敏感,假设敏感信号动,则Q也会动。

- 将clk or rst_n两个沿写在敏感列表中,意思是最终的输出Q对两个沿敏感,而不是对电平敏感

- 用非阻塞赋值

- 组合always@(*)

- *在这里表示省略描述。综合器在看到这种省略描述后,会自动在always块中寻找与输出z相关的输入信号,自动填入敏感列表中。

- 阻塞赋值

- 时序always@(posedge clk or negedge rst_n)

2.3 对寄存器的深度解读

- 对于同样的功能需求,双沿触发必须的时钟慢,但要求时钟是50%占空比,而单沿触发,对时钟的要求快一倍,但对时钟形状的要求降低很多

- 复位信号

- rst_n,以0电平作为复位电平,1电平解复位。

- 原因是,数字电路的复位信号是模拟电路给的,通常,模拟电路将其命名为POR(Power On Reset),即上电复位信号。芯片刚通电时,电压小,逐渐上升到要求的电压,例如1.8V,POR本质上是一个电压上升的标志,模拟电路放一个比较器,将输入电压与0.9V比较,电压小于0.9V,POR为0,电压大于0.9V,POR为1。

- 因此复位信号上电时总是先0后1,数字寄存器需要在复位信号为0的阶段保持复位态,不能运行,因为此时芯片电压不足,不能保证正常运行,而复位信号变成1,说明上电完毕,电压充足,寄存器解除复位进行正常运行是安全的。

- negedge rst_n

- negedge rst_n本身表示复位信号表现出下降沿时,即从1变为0时,才会触发Q的动作。但这样的话,在芯片刚上电时,复位信号一直为0,随着芯片上电完成,复位信号逐渐从0变为1。整个过程没有下降沿,是否意味着Q端在芯片上电后不处于复位状态,而是处于不定态?

- 但实际复位信号对寄存器的作用不是利用信号沿来驱动的,而是通过电平来驱动,它更像组合逻辑而非时序逻辑。

- 只要rst_n为0,即使没有下降沿,寄存器都处在复位态

2.4 阻塞与非阻塞赋值的区别

- 非阻塞赋值的意思是该句表达不会阻塞后续表达的执行

- 阻塞赋值,意思是如果前一句不执行,后一句就无法执行(或者说用的是前一时刻的值)

- 阻塞赋值在Verilog中真正体现阻塞,是在仿真使用的不可综合语法中(第3章)

2.5 组合逻辑的表达方式

- 比较简单的逻辑适合使用assign方式,较为复杂的逻辑应使用always块

2.6 组合逻辑中的选择器

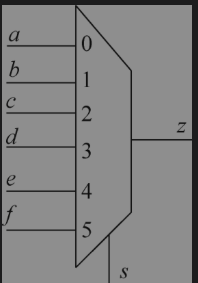

- 多选1选择器

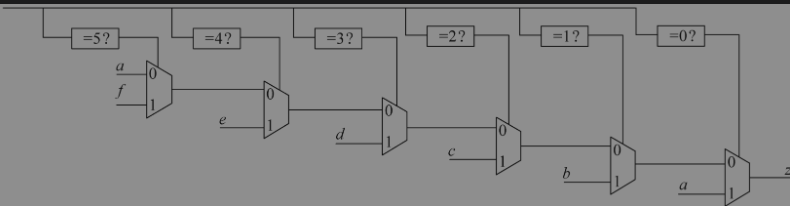

- 用if实现有优先级,综合电路如下图所示

- 组合逻辑中的if和else if,最后必须跟一句else,使整体逻辑完整。若没有else,则该电路会综合出一个锁存器(Latch)。(尽量避免出现锁存器)

- 组合逻辑中的if和else if,最后必须跟一句else,使整体逻辑完整。若没有else,则该电路会综合出一个锁存器(Latch)。(尽量避免出现锁存器)

- 用case实现每个选择都是并列的,综合电路如下图所示

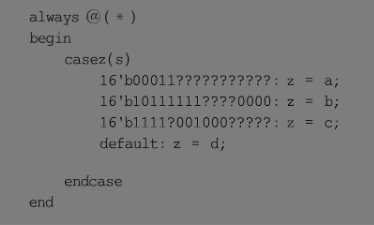

- case变体,casez,问号表示0或1都匹配,

- 用if实现有优先级,综合电路如下图所示

2'bx0:未知值 (Unknown),x 表示未知状态(可能是0或1,但不确定)(信号状态不确定)

2'bz0:高阻态 (High-Impedance),该值表示高位是高阻态(z),低位是逻辑0(0)(无驱动)

case将0/1/x/z时为4中不同状态进行比对,

casez将z当做don't care,

casex将x/z均视为don't care进行比对。

浙公网安备 33010602011771号

浙公网安备 33010602011771号