工作中使用到CC2500模块,2.4GHz频率的阻抗为80j74欧姆,现在要将其封装为模块,用于2470MHz信号的接收。

ADS仿真计算:

差分输出为80+j74Ω。输入端阻抗Zs = 50Ω+j0Ω。

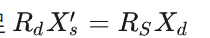

以P1为分界,分为P1左侧和P1右侧,当左右的阻抗共轭时最大功率传输。由于输入阻抗为50欧姆,现在我们令P1端口的实数部分为50Ω。P1端口往右看Z's的阻抗值经以下公式计算

Z's = 50+j46.25;为实现最大信号传输,P1端口左边的部分阻抗Z''s阻抗为Z''s = 50-j46.25Ω;

根绝Smith圆图计算,匹配一个3nH左右的电感实现-46.25jΩ的阻抗变换。也可根据

也可根据

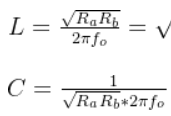

计算所需要的容值和感值。

P1端口往右边看时一个单端转差分的LC电路。L2、L3、C4、C5组成。实现50Ω+j46.25Ω到80j*74Ω的阻抗变化。L和C的计算公式如下,需注意Za(Z's)与Zb(Z'L负载阻抗)相乘需要实部与实部相乘加上虚部与虚部相乘。

计算得到LC对应的值。

仿真结果如下:

插损在3.01左右,相位差在1°左右。

想学习理论的小伙伴可以看后面几个链接

参考文献:

https://blog.csdn.net/rzchong1988/article/details/121414283

https://zhuanlan.zhihu.com/p/657193575

https://blog.csdn.net/xxy13690028757/article/details/148766271

浙公网安备 33010602011771号

浙公网安备 33010602011771号