11-15-DDR布线演示

- mil精度—2mil,mm精度—4mil

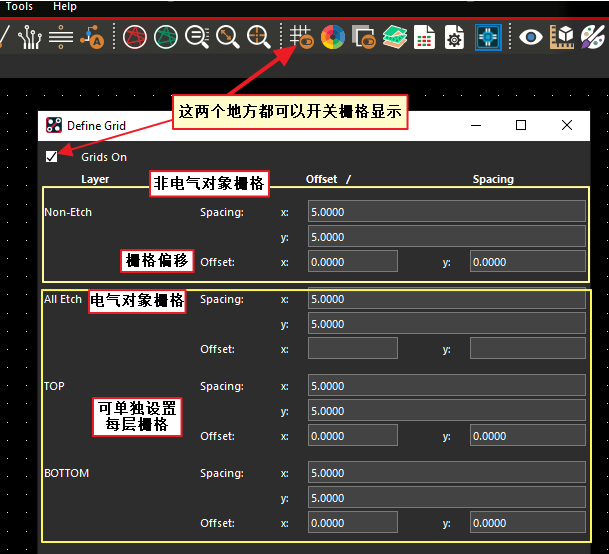

- 栅格设置:

![]()

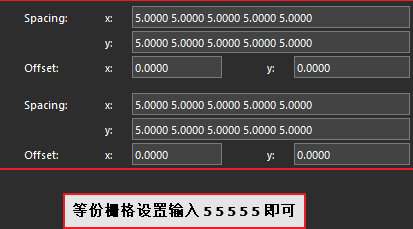

- 等份栅格:

- 方便拉线

- Allegro可以设置等份栅格:如 5 5 5 5 5 把一个25栅格分成5个等份。界面上会间隔4个栅格后显示一个大一点的栅格。

- 走线模式:

- 模式介绍:

- 走线到焊盘处拐线:

- 走线连接模式下,右键,取消enhanced pad entry

- Enhance pad Entry(增强焊盘进入约束功能)

- 多根线一起拉线:

- 选择好过孔,拉线,右键切换单根走(single trance mode)

- t型 - 单片ddr中间的过孔左右均匀排放,旁边的电源与地过孔向外拉(出线到T点拐角空间),DDR左排连接T左边点孔

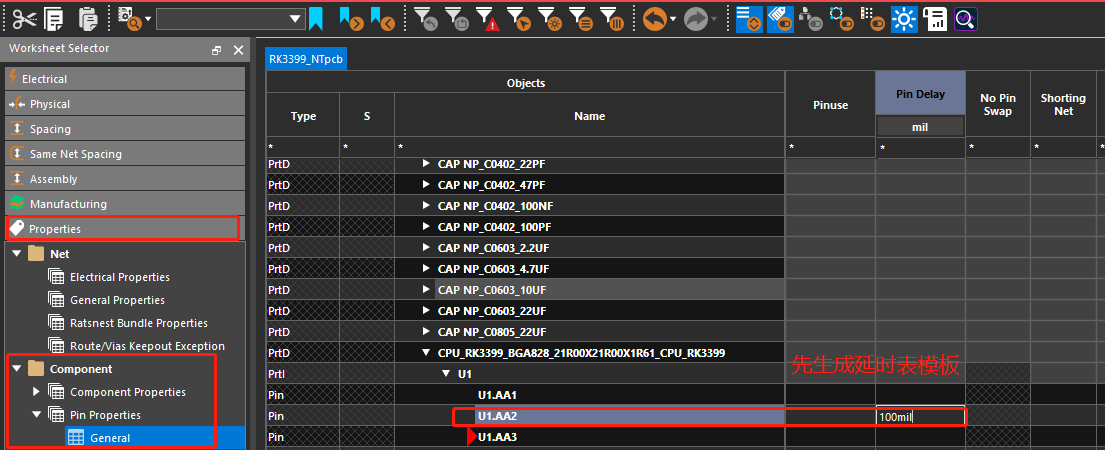

- 芯片RK3399内部等长:

- 假如RK3399内部误差大(上升到mm),DDR3 - DDR4内部需要做等长

- 一般通用DDR内部做好了等长,只要做RK3399即可

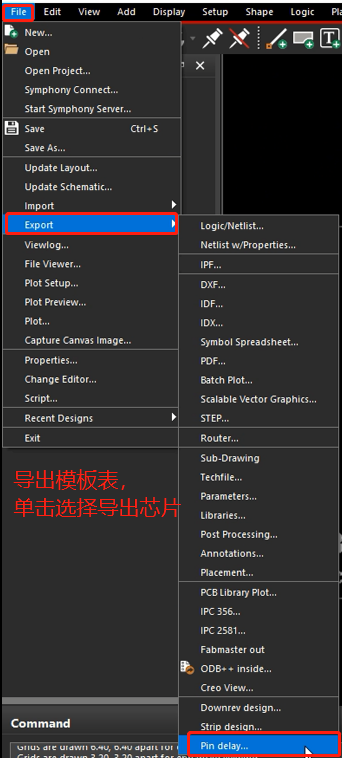

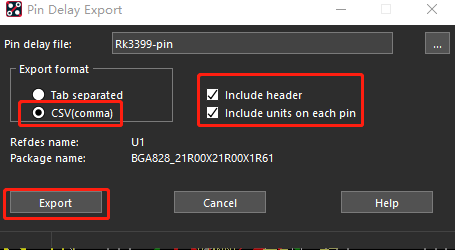

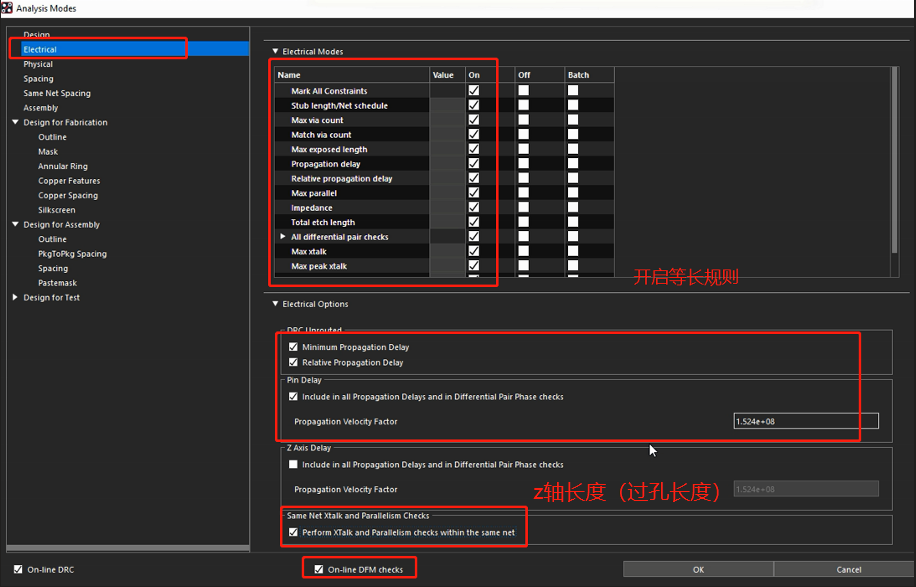

- 生成延时模板:

- 模板文件csv在PCB根目录

- 模板管脚名字与长度mil(官方是网络名字与长度mm)

![]()

![]()

![]()

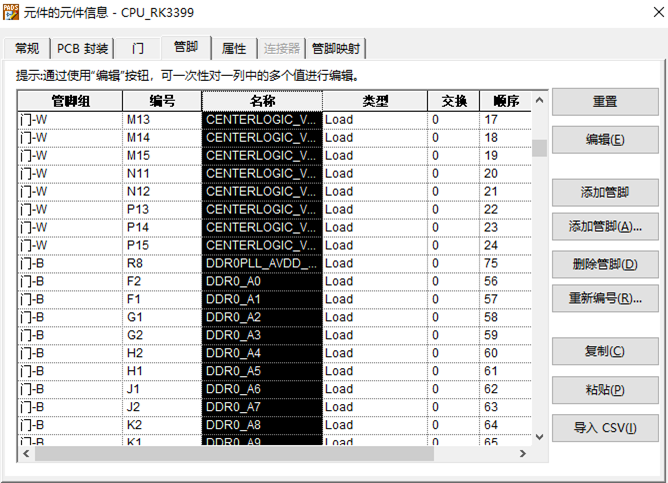

- 利用logic的编辑封装,复制管脚名字来快速改动模板

![]()

- excel粘贴选择为数值,然后保存

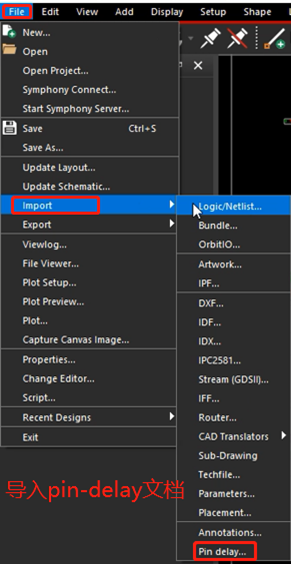

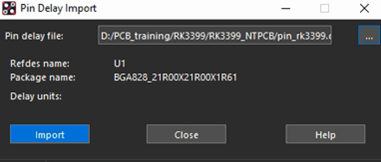

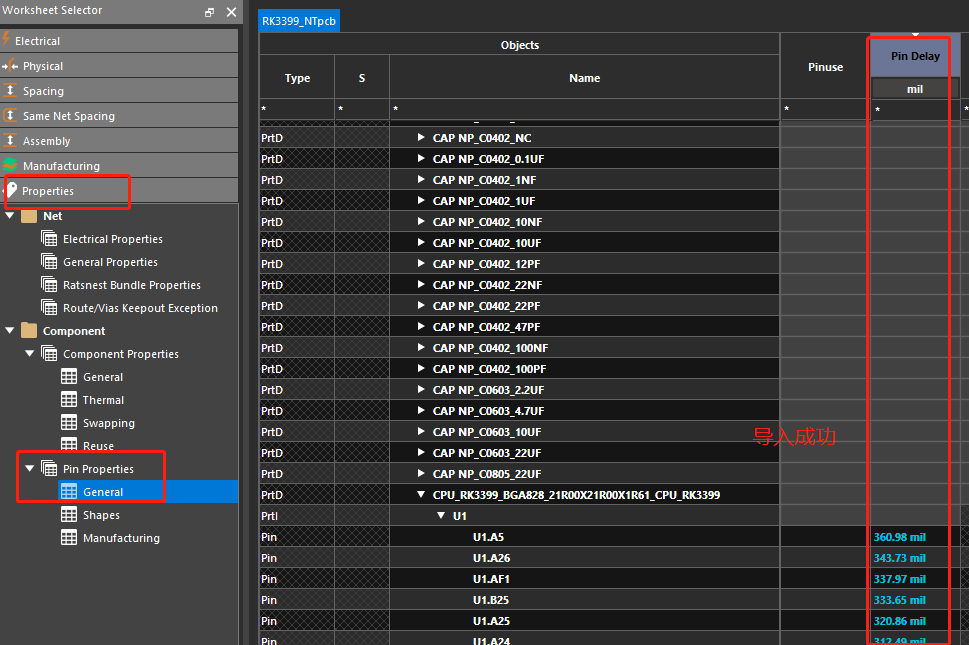

- allegro导入pin-delay表格

![]()

![]()

![]()

![]()

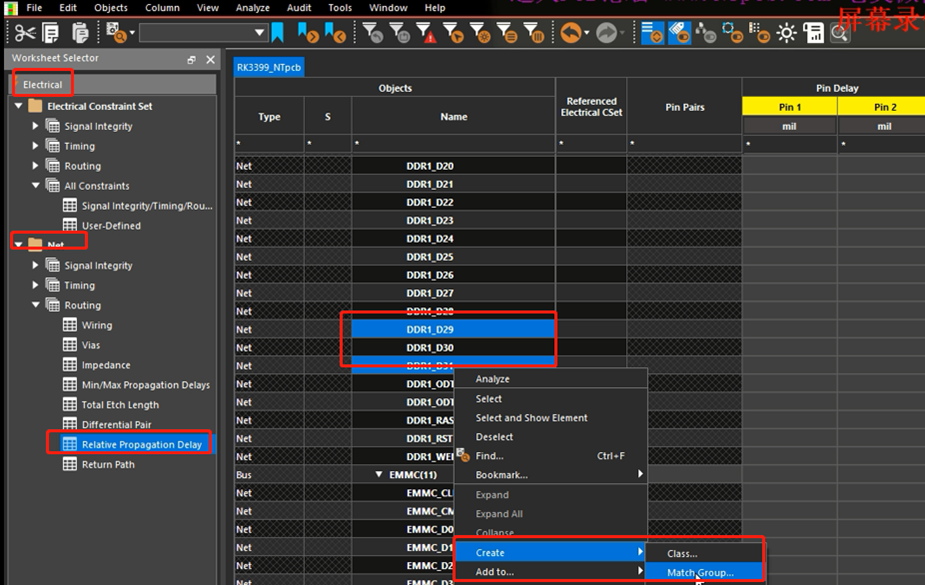

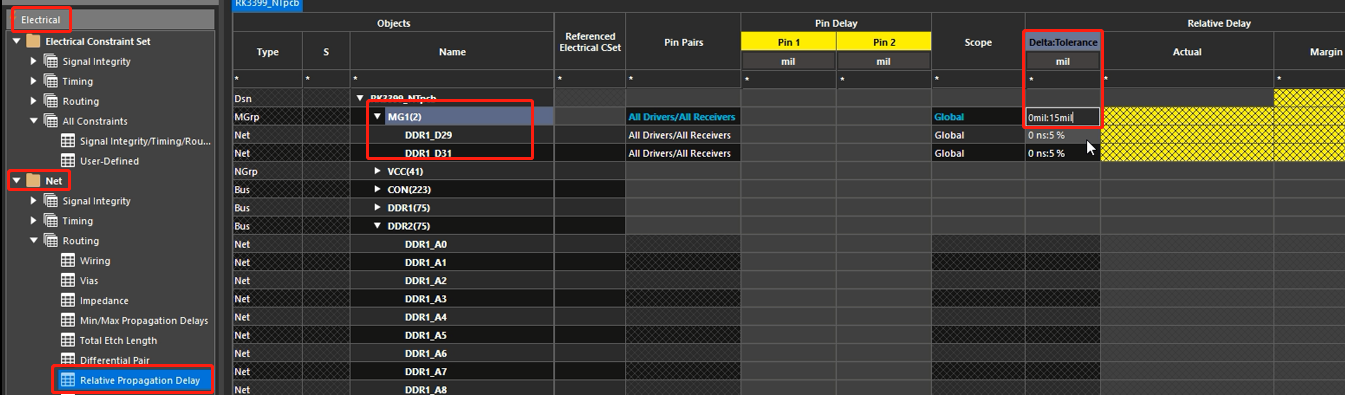

- 利用相对延时传播做等长填写0mil:15mil,右键分析等长

![]()

- 规则菜单栏显示:

- 显示所有菜单栏:View - show all columns

- 查看网络走线长度:

- 选中网络右键-show element

- DDR划分不同组:

- 原理图选好网络,allegro使用BUS_name分组,然后分配好飞线与过孔的颜色

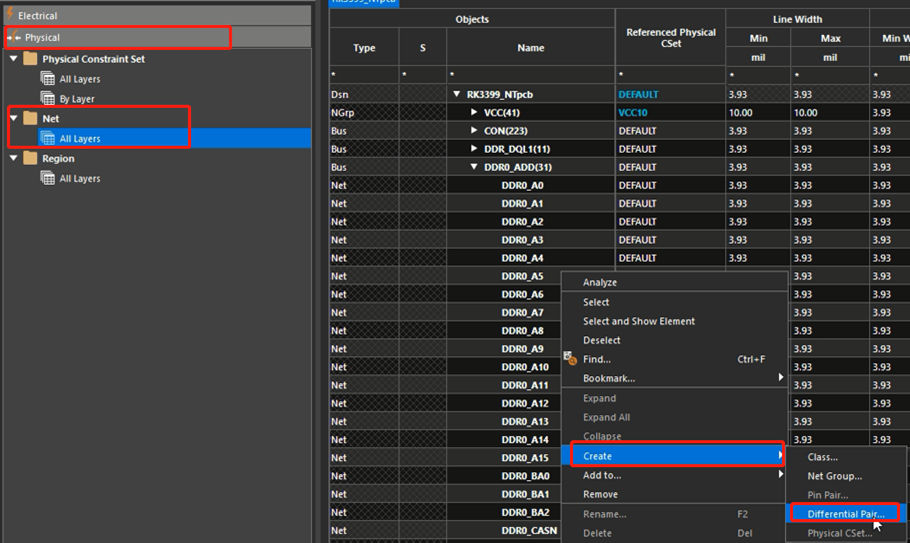

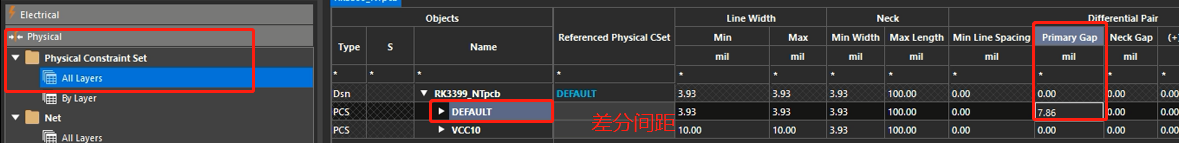

- 设置差分规则:

![]()

- allegro拉线:

- S命令:分步拉动走线,才能拉出固定走线

- DDR阻抗:

- 顶层50欧,3.93 - 53

浙公网安备 33010602011771号

浙公网安备 33010602011771号