FPGA/EDA实验箱-竞赛普及版(ALTERA)

型号:XQEP4CE-TEB V6.1

1、产品概述

FPGA/EDA实验箱是一款FPGA教学实验系统,由FPGA开发板、显示屏、下载器、应用模块及相关实验配件组成;

FPGA开发板采用底板+核心板的设计架构,核心板板采用是六层PCB设计,采用大容量管脚更多的BGA封装,F484封装,使整个核心板的性能和稳定性有了很大的提供,并同时为用户提供大量的有效I/O。

开发板的SDRAM,FLASH,SRAM都采用独立I/O控制,提供了更加方面灵活的设计途径,同时能够稳定高速运行NIOS系统在100M频率以上,是做系统评估的最佳选择。

FPGA/EDA实验箱满足《EDA技术与应用》、《FPGA原理与应用技术》、《SOPC技术应用》的基础教学而设计开发,该系统基于ALTERA的Cyclone® IV EP4CE30F23C8N处理器,实现了多模块的应用实验。它是集学习、应用编程、开发研究于一体多功能创新平台。

2、产品特点

- FPGA基于Cyclone® IV EP4CE30F23C8N处理器,100W门级FPGA;

- 开发板的SDRAM,FLASH,SRAM都采用独立I/O控制,便于功能模块的扩展。

- FPGA高速运行NIOS系统在100M频率以上,能够提供稳定可靠的性能。

- 底板资源8位拨码开关、14个琴键开关、8位7段数码管、4X4矩阵键盘、7寸触摸屏、VGA接口、摄像头接口、LVDS接口、音频DAC、10bit DA、8bit AD、步进电机、直流电机、PS2键盘鼠标、USB2.0、网口、SD/TF、USB串口、蜂鸣器、红外接收器、温度传感器、独立IO接口等;

- 根据实际课程教学要求提供Verilog语言的实验例程,实验指导手册包括实验目的、原理、步骤及源码解析等;适用于计信、通信、测控、电子等教学。

3、硬件资源

开发板资源

|

序号 |

外设 |

说明 |

|

|

1 |

FPGA处理器 |

不低于Cyclone® IV EP4CE30F23C8N处理器,100W门级FPGA,Speed Grade 8,Logic Elements 28848,Memory Bits 608256,Embedded Multipliers 132,Global Clocks 20,I/O 533,PLLs 4。 |

|

|

2 |

串行FLASH |

标配EPCS64(64Mbit)。 |

|

|

3 |

SRAM |

一片256K×16Bit SRAM (4Mbit),独立地址数据总线,高速静态SRAM 10ns读写。 |

|

|

4 |

SDRAM |

一片16M×16Bit SDRAM ,最高143MHz读写速度 256Mb,超大容量,预留扩展I/O,可以直接扩展到32M X 16bit SDRAM (64M byte), 独立I/O控制。 |

|

|

5 |

并行FLASH |

16M byte(128Mbit)大容量,,独立I/O控制。 |

|

|

6 |

内存EEPROM |

512*8bit的EEPROM,支持IIC接口。 |

|

|

7 |

时钟 |

共3个,其中2个源时钟50M,20M方便用户使用和分频处理,用户可以自行更换其他频率,另外提供一个标准正方5x5(mm)晶振插座,方便用户实验,用户可以根据具体要求更换不同频率晶振。 |

|

|

8 |

实时时钟 |

DS1302时钟芯片。 |

|

|

9 |

LED |

共12个,核心板4个,底板8个。 |

|

|

10 |

数码管 |

8个七段数码管显示,采用独立I/O控制。 |

|

|

11 |

琴键开关 |

共14个,其中核心板独立I/O的4个琴键开关、底板8个高低电平拨码开关,平时拉高。一个4X4标准矩阵键盘及其接口。 |

|

|

12 |

系统主复位按键 |

带上拉,也可以做为用户按键输入。 |

|

|

13 |

蜂鸣器 |

5V长声,通过驱动电路驱动,设置有跳线,可断开或接通蜂鸣器。 |

|

|

14 |

红外接收模块 |

1个标准红外接收模块。 |

|

|

15 |

Display |

液晶屏接口 |

一个标准液晶接口,NIOS IP核直接支持。独立I/0,也可以做用户I/O |

|

VGA |

一个8色视频VGA输出接口。 |

||

|

16 |

SD/TF插槽 |

1个,支持SPI以及SD 1-bit两种读取模式。 |

|

|

17 |

USB 2.0口 |

1个CH376芯片,支持USB 2.0标准的USB主/从控制器。 |

|

|

18 |

PS/2接口 |

1个,支持PS/2鼠标和键盘的连接。 |

|

|

19 |

以太网接口 |

1个以太网口。 |

|

|

20 |

RS232口 |

2个标准RS232接口。 |

|

|

21 |

步进电机接口 |

一个标准步进电机及其接口。 |

|

|

22 |

直流电机接口 |

一个标准PWM直流电机接口。 |

|

|

23 |

继电器 |

一个标准继电器。 |

|

|

24 |

JTAG端口 |

1x JTAG调试接口。 |

|

|

25 |

AS端口 |

EPCS串行FLASH编程烧写。 |

|

|

26 |

扩展I/O口 |

提供4个40PIN扩展接口。其中2组用于板对板连接,其余2组做为用户I/O端口,进行拓展实验。 |

|

|

27 |

电源 |

5V,3.3V/3A,独立引出方便用户使用和测试 |

|

|

FPGA下载器 |

支持ALTERA FPGA/CPLD/SOC QUARTUS II和Nios II 支持SingalTap Ⅱ在线分析 支持AS/JTAG下载模式 |

软件参数

|

配套的开发软件 |

1、Quartus II 11.0sp1 2、NIOS II IDE 11.0sp1 3、ModelSim 10.0c SE |

4、配套教学资源

(1) 提供芯片数据手册、底板原理图;

(2) 提供Verilog实验例程。

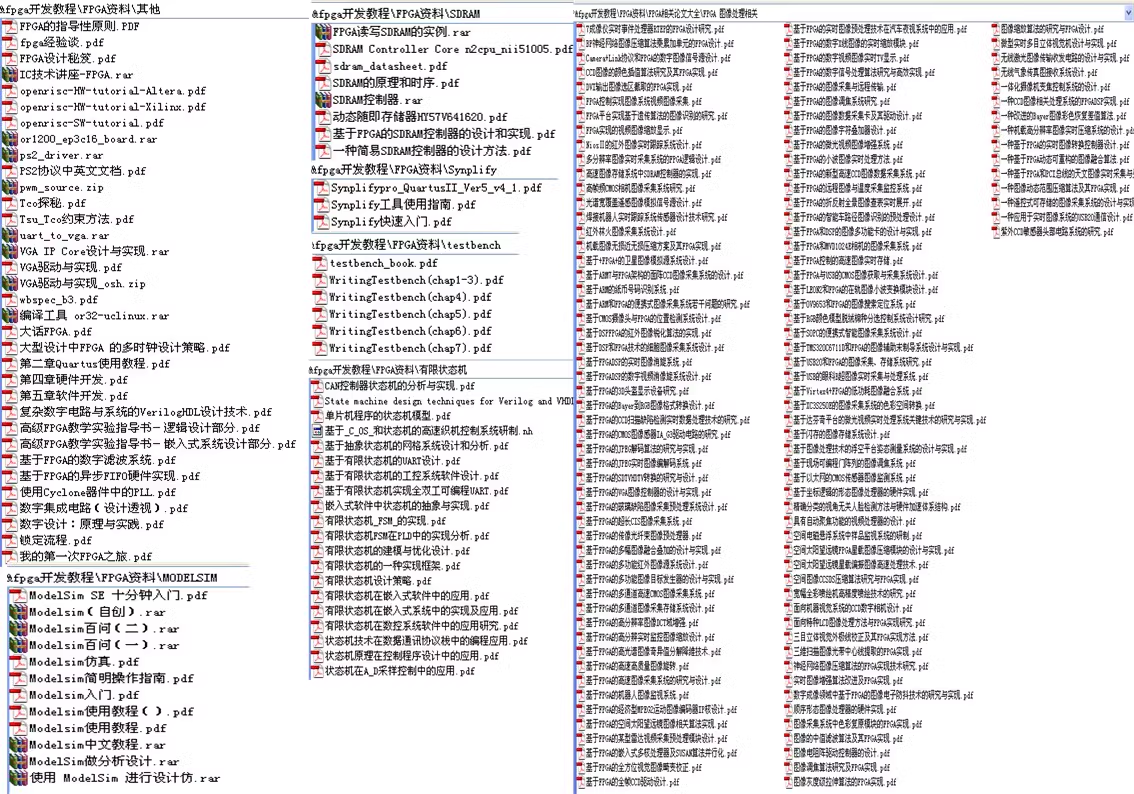

(3) 提供完整的实验代码,以及适合教学的《教学实验指导手册》等说明文档:

5、配套实验

|

|

EDA基础实验 1 FPGA实验环境搭建 2 LED实验 3 按键控制实验 4 三人表决器 4 38译码器 5 比较器 6 多路选择器 7 HEX转BCD码 8 数码管显示实验 9 加法器数码管显示 10 数码管电子钟 11 4x4矩阵键盘实验 12 蜂鸣器实验 13 ROM读写实验 14 数据存储实验 15 数字时钟综合实验 16 红外遥控实验 17 USB功能实验 18 以太网通讯实验 19 RS232串口收发实验 20 PWM驱动直流电机 21 步进电机控制实验 22 18B20温度计实验 23 AD采集电压 24 DA输出电压 25 AD/DA虚拟示波器实验 26 SignalTap逻辑分析仪 27 PS2键盘控制实验 28 并串转换实验 29 I/O扩展实验 30 音乐播放实验 31 SD卡读取图片 32 VGA显示实验 33 摄像头采集图像 34 图像处理实验 35 图像显示实验

SOPC (NIOS II)实验 1 hello实验 2 LED流水灯实验 3 中断实验 4 串口通信实验 5 RTC控制实验 6 IIC EEPROM读写实验 7 SPI实验 8 网络通信实验 9 系统时钟实验 10 定时器实验 11 PS2键盘实验 12 DMA实验 13 SDRAM读写实验 14 串行FLASH读写实验 15 12864液晶显示实验 16 PWM实验 17 LCD1602显示实验 18 USB通信实验 19 U盘读写实验 20 SD卡读写控制实验 21 AVALON IP核实验 22 数码管显示实验 23 LCD显示实验 24 NIOS固化到串行FLASH 25 NIOS固化到并行FLASH实验 26 系统全检测实验 |

浙公网安备 33010602011771号

浙公网安备 33010602011771号