01_数字电路基础

1. 门电路

数字逻辑电路的发展:分立器件电路 ===》集成电路(Integrated Circuits,IC)===》片上系统(System on Chip,SOC)

根据集成度的高低,可将数字集成电路划分为: 小规模集成电路(Small Scale Integration,SSI)

中规模集成电路(Medium Scale Integration,MSI)

大规模集成电路(Large Scale Integration,LSI)

超大规模集成电路(Very Large Scale Integration,VLSI)

甚大规模集成电路(Ultra Large Scale Integration,ULSI)

根据逻辑功能的特点,可将数字集成电路分为:通用型和专用型。

1)中、小规模数字集成电路:它们的逻辑功能比较简单,而且是固定不变的,属于标准化的通用集成电路。由于它们的这些逻辑功能在组成复杂数字系统时经常要用到,所以这些器件有很强的通用性。

2)专用集成电路(ASIC):为某种专门用途而设计的集成电路。它不仅能够减小电路的体积、重量、功耗,而且会使电路的可靠性大为提高。然而,在用量不大的情况下,设计和制造这样的专用集成电路不仅成本高,而且设计、制造的周期也太长。

3)可编程逻辑器件(PLD):作为一种通用型器件生产,但它的逻辑功能是由用户通过对器件编程来设定的。而且,有些PLD的集成度很高,足以满足设计一般数字系统的需要。

2. 组合逻辑电路和时序逻辑电路

数字电路分为两大类:组合逻辑电路(Combinational Logic Circuit,组合电路)和时序逻辑电路(Sequential Logic Circuit,时序电路),其逻辑功能和电路结构上的特点分别为:

- 组合电路:任意时刻的输出仅仅取决于该时刻的输入,而与电路过去的状态无关。因此,组合逻辑电路中只包含门电路,而没有存储(记忆)单元。

- 时序电路:

2.1 组合逻辑电路中的竞争-冒险:

1. 概念

竞争:将门电路两个输入信号同时向相反的逻辑电平跳变(一个从1变为0,另一个从0变为1)的现象称为竞争。

竞争-冒险:由于竞争而在电路输出端可能产生尖峰脉冲的现象称为竞争-冒险。

竞争-冒险是组合逻辑电路工作状态转换过程中经常会出现的一种现象。如果负载是一些对尖峰脉冲敏感的电路(例如触发器),则必须采取措施防止由于竞争而产生的尖峰脉冲。如果负载电路对尖峰脉冲不敏感(例如光电显示器件),就不必考虑这个问题了。

2. 检查竞争-冒险现象的方法

(1)在输入变量每次只有一个改变状态的简单情况下,可以通过逻辑函数式判断组合逻辑电路中是否存在竞争-冒险现象。

如果输出端门电路的两个输入信号 A 和 A’ 是输入变量 A 经过两个不同的传输途径而来的,那么当输入变量 A 的状态发生突变时,输出端便有可能产生尖峰脉冲。因此,只要输出端的逻辑函数在一定条件下能化简成 Y=A+A' 或 Y=AA' ,则可判定存在竞争-冒险现象。

(2)计算机辅助分析:

通过在计算机上运行数字电路的模拟程序,能够迅速查出电路是否会存在竞争-冒险现象,但得到的模拟结果有时和实际电路的工作状态会有出入。目前已经有这类成熟的程序可供选用。

(3)实验:

用实验来检查电路的输出端是否有因为竞争-冒险现象而产生的尖峰脉冲,这时加到输入端的信号波形应该包含输入变量所有可能发生的状态变化。

3. 消除竞争-冒险现象的方法

(1)接入滤波电容:

在输出端并接一个很小的滤波电容,把尖峰脉冲的幅度削弱至门电路的阈值电压以下。该方法简单易行,但输出电压的波形随之变坏。因此,只适用于对输出波形的前、后沿无严格要求的场合。

(2)引入选通脉冲:

在电路中引入一个选通脉冲 p,p 的高电平出现在电路到达稳定状态以后。

(3)修改逻辑设计:

增加冗余项,但适用范围有限。

3. 半导体存储电路

3.1 概述

通常将只能存储一位数据的电路叫做 “存储单元” ,将用于存储一组数据的存储电路叫做 “寄存器(Register)” ,将用于存储大量数据的存储电路叫做 “存储器(Memory)” 。

(1)存储单元

存储单元分为 “静态存储单元” 和 “动态存储单元” 。

静态存储单元由门电路连接而成,只要不切断供电电源,静态存储单元的状态会一直保持下去。目前使用的静态存储单元有锁存器和触发器两类,它们的根本区别在于,锁存器的置 1 和置 0 操作通过直接输入置 1 和置 0 信号即可完成,而触发器的置 1 和置 0操作除了需要输入置 1 和置 0 的信号以外,还必须在时钟信号到来时才能完成。

动态存储单元则是利用电容的电荷存储效应来存储数据的。由于电容的充放电需要一定的时间,因而它的工作速度低于静态存储单元。而且,电容上存储的电荷会随着时间的推移而逐渐泄漏,必须定期进行“刷新”(即将原来的数据重新写入),才能保证数据不会丢失。虽然如此,由于动态存储单元的电路结构十分简单,所以仍然被广泛用于大容量的存储器当中。

(2)寄存器

寄存器由一组具有公共时钟信号输入端的触发器组成。由于每个触发器的输入端和输出端都直接被引出,可以直接和周围电路连接,快速地进行数据交换。由 n 个触发器组成的寄存器可以存储一组 n 位的二值数据。

(3)存储器

由于存储器中存储单元的数量非常大,而集成电路引出端的数目是很有限的,不可能将每个存储单元的输入端和输出端都引出,所以采用了寻址读/写的工作方式:只有被选中地址中的一个(或一组)存储单元才能与输入、输出电路接通,进行读/写操作,而输入、输出电路是公用的。因此,存储器的基本结构形式为:存储矩阵 + 读/写控制电路。

根据工作方式的不同,可将存储器分为 “随机存储器(Random Access Memory,RAM)” 和 “只读存储器(Read-Only Memory,ROM)”。

- RAM:可随时从中快速地读出或写入数据。根据采用的存储单元不同,分为 “静态随机存储器(SRAM)” 和 “动态随机存储器(DRAM)”。

- ROM:只能从中读出数据,包括 “掩模ROM”、“可编程ROM(PROM)”、“可擦除的可编程ROM(EPROM)” 及 “电信号擦除的EPROM(E2PROM)”。

掩模ROM:存储的数据在制作芯片时已经确定,无法更改。

PROM:数据可由用户根据自己的需要写入,但一经写入后就不能再修改了。

EPROM:数据不但可以由用户自己写入,而且能够擦除重写,具有更大的使用灵活性。早期采用紫外线照射擦除,费时费力,成本高。

E2PROM:使用电信号进行擦除。目前在 U 盘和各种便携式移动设备中广泛使用的 “ 闪存(Flash Memory)”就是一种 E2PROM。

3.2 触发器

1. “逻辑功能” 和 “触发方式” 是触发器的两个最重要的特性。

- 逻辑功能是指稳态下触发器的次态和现态与输入之间的逻辑关系。按照逻辑功能的不同特点, 通常将时钟控制的触发器分为 SR触发器、JK触发器、T触发器和 D触发器。

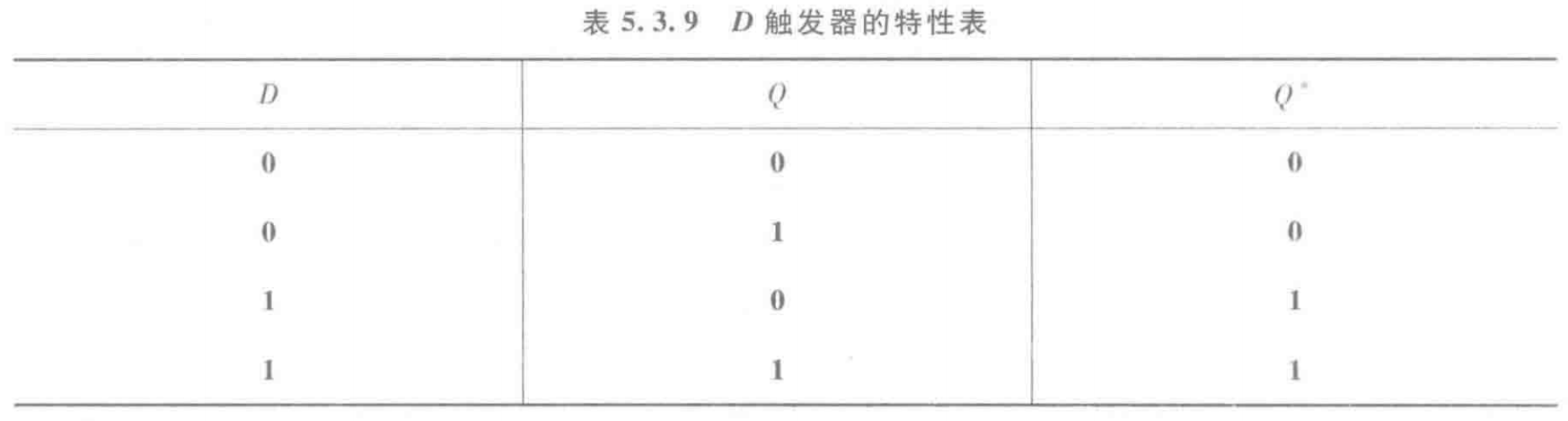

D触发器:凡在时钟信号作用下,逻辑功能符合表5.3.9特性表所规定的逻辑功能者,无论触发方式如何,均称为D触发器。

D触发器的特性方程为:Q* = D

- 触发方式指出了触发器在动态翻转过程中的动作特点,分为电平触发、边沿触发和脉冲触发。

边沿触发方式的动作特点:触发器的次态仅取决于时钟信号的上升沿或下降沿到达时输入的逻辑状态,而在这之前或之后,输入信号的变化对触发器输出的状态没有影响。这一特点有效提高了触发器的抗干扰能力,因而也提高了电路的工作可靠性。

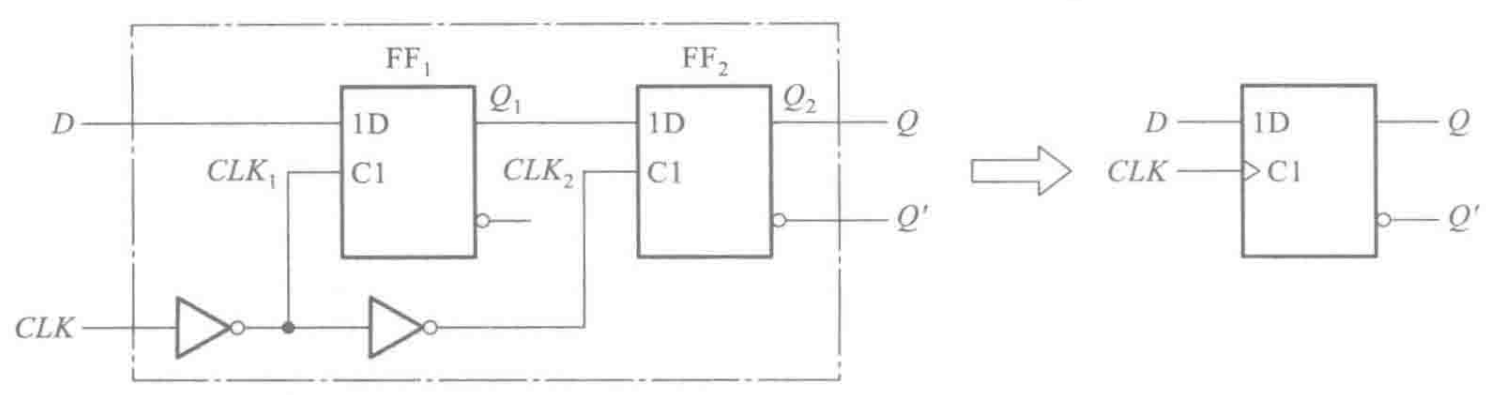

2. 边沿 D 触发器

如图所示为用两个电平触发 D 触发器组成边沿触发 D 触发器的原理性框图,图中的 FF1 和 FF2 是两个电平触发的 D 触发器(也称为 D 型锁存器)。

由图可见,当 CLK 处于低电平时,CLK1 为高电平,FF1 的输出 Q1 跟随输入端 D 的状态而变化,始终保持 Q1= D。与此同时,CLK2 为低电平,FF2 的输出 Q2 (也就是整个电路的最后输出 Q)保持原来的状态不变。当 CLK 由低电平跳变至高电平时,

浙公网安备 33010602011771号

浙公网安备 33010602011771号