DE0-Nano-SoC开发板诡异的电源电路方案设计分析

这些日子一直在设计自己的Cyclone V SoC开发板,由于我们这种散兵游勇,是断然没有厂家和代理技术支持的,因此只能找各种现成方案参考。其实Cyclone V SoC芯片的外围电路设计不难,无非就是DDR3、千兆以太网PHY、USB PHY、USB转串口。但是除了这些功能电路外,更重要的应该是电源电路了。以DE0-Nano-SoC为参考,一个板子上,总共涉及到了5V、9V、3.3V、1.1V、1.2V、1.5V、1.8V、2.5V、以及DDR的VTT和VREF这10种电压。吓死个人哦。一直都听说电源设计很重要,一看到这么多电源,瞬间有种怂了的感觉。不过,再怎么麻烦,该解决的问题还是要解决的。由于市面上Cyclone V SoC的板子真心不多,而DE0-Nano-SoC作为一个功能最简单的板子,就以他的电源方案作为参考了。

5V:这个好说,作为整板的供电输入,使用一个10W电源供电

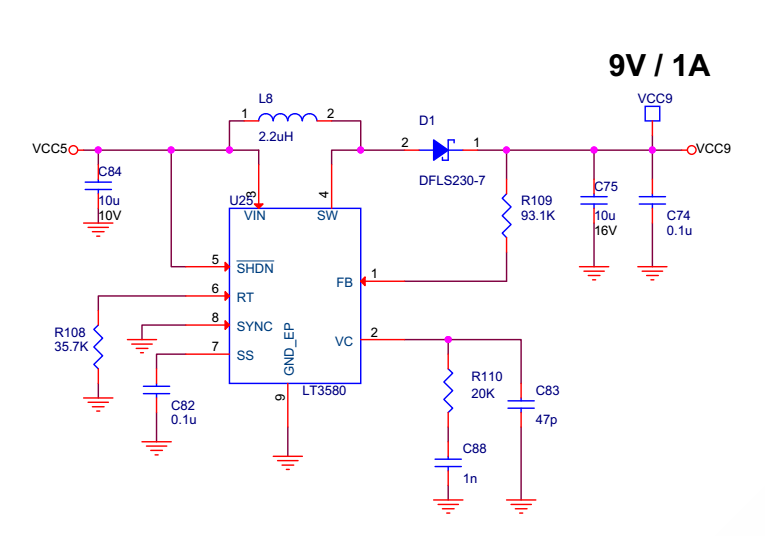

9V/1A:这个9V在这个板子上貌似是给LTC的DAC外接板用的,使用了一个Boost升压电路,与核心系统无关,暂时不考虑

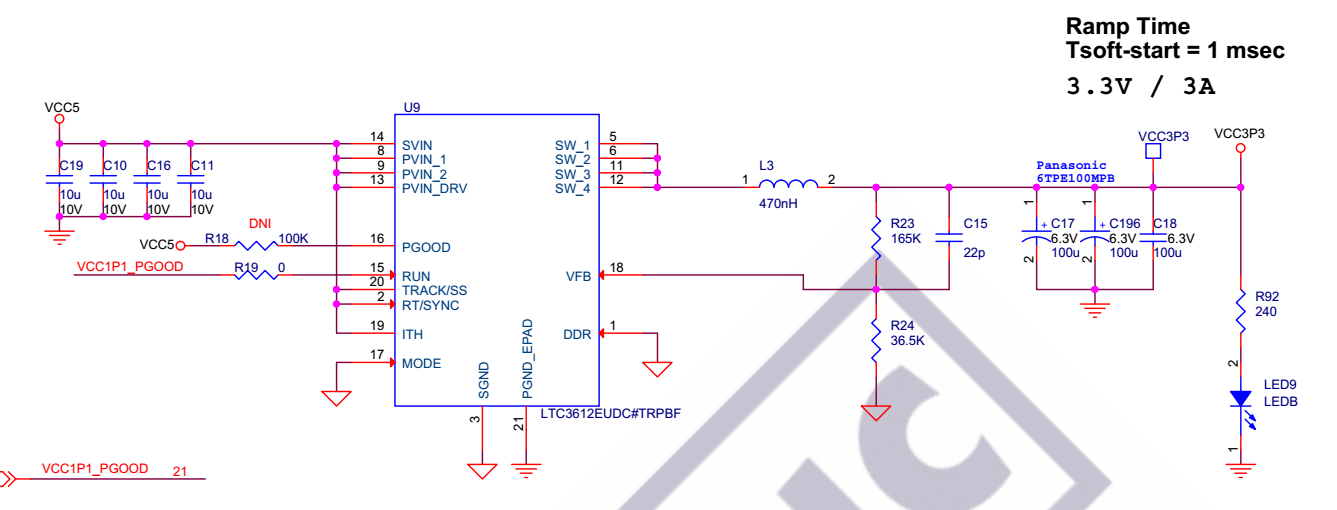

3.3V/3A:几乎板子上每个芯片都需要3.3V供电,而且有些排针接口还要对外供电,因此设计一个3A的输出没什么疑问。

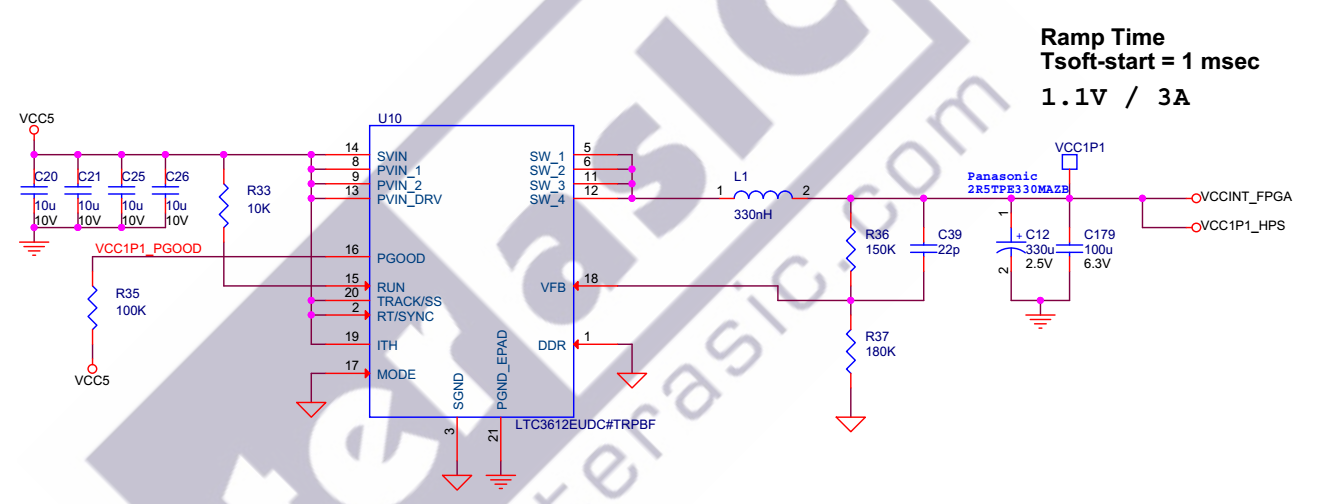

1.1V/3A:这个电源可以看到,在输出时分成了两个名字,一个叫VCCINT_FPGA,一个叫VCC1P1_HPS,既然是要给FPGA内核和HPS同时供电,设计3A的电流也无可厚非了。只是事实上应该还有压缩的空间,但是没必要了。

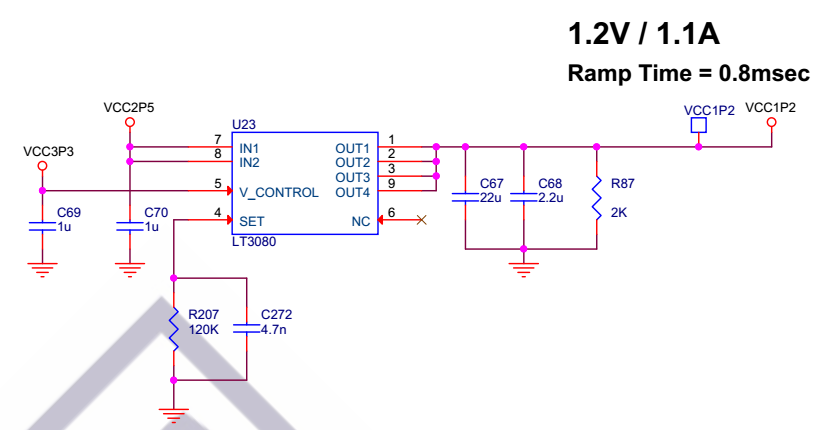

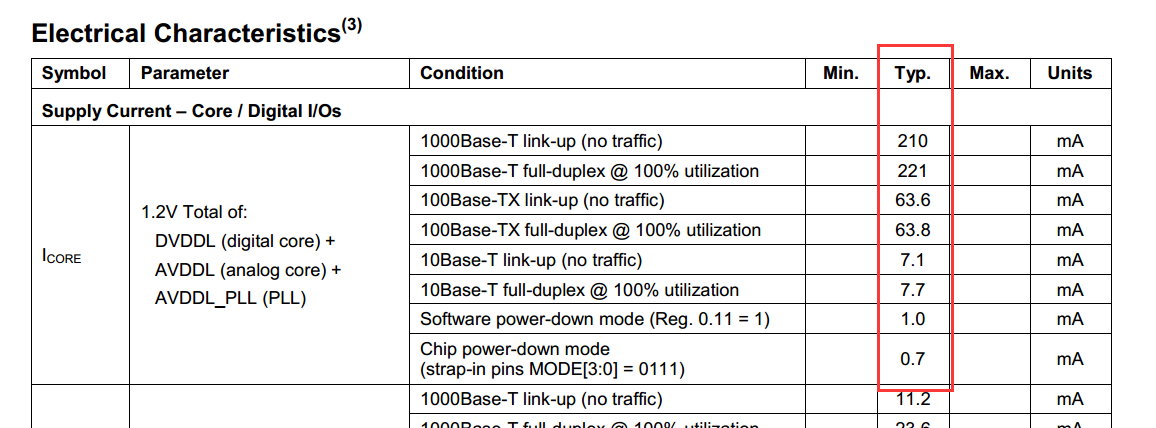

1.2V/1.1A:这个在原理图里面搜索了下,仅仅是给以太网PHY芯片做内核供电用的,而根据以太网芯片手册里面的描述,以太网的内核供电工作电流典型值如下表所示,可以看到,千兆全双工100%使用率下也才221mA,所以个人认为这个地方的1.2V/1.1A的电源设计太浪费了,而且一般的以太网PHY芯片都自带LDO控制脚,使用一个AO3415的MOS管就能自给自足了。因此这个1.2V/1.1A设计性价比不高。

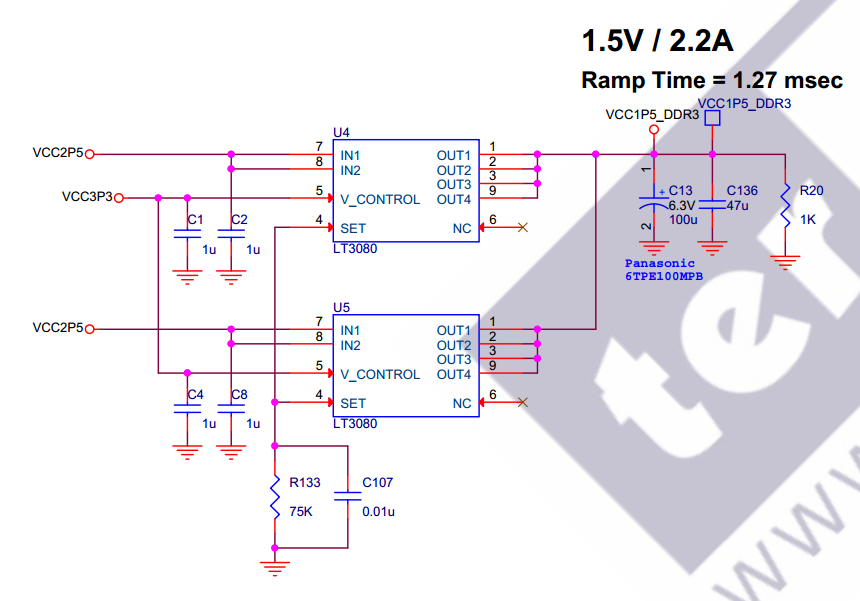

1.5V/2.2A:真有钱,用了2个1.1A的LDO并联得到2.2A输出。这个电源是给DDR3芯片供电用的,既然都达到2.2A的电流输出了,为啥不用DCDC,而要用两个LDO并联呢?难道DDR3不能用DCDC供电?还是这里只是单纯为了刷刷存在感?另外也想知道,2颗DDR3的功耗大概在多少,有必要用到2.2A的电流吗?

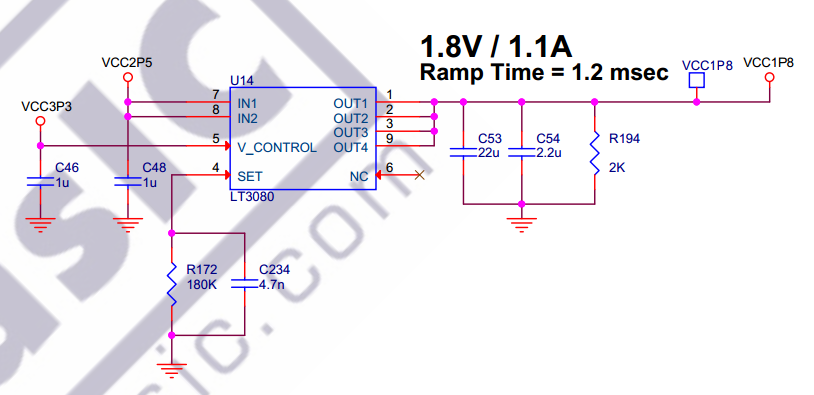

1.8V/1.1A:在原理图上查找了下,这个供电主要作用有两个,一个是给PLL芯片供电,输出多路时钟,供FPGA和HPS时钟,另一个是给板载的USB Blaster II下载器的核心芯片EPM570型CPLD做内核供电。因此实际也与Cyclone V SOC芯片无关。

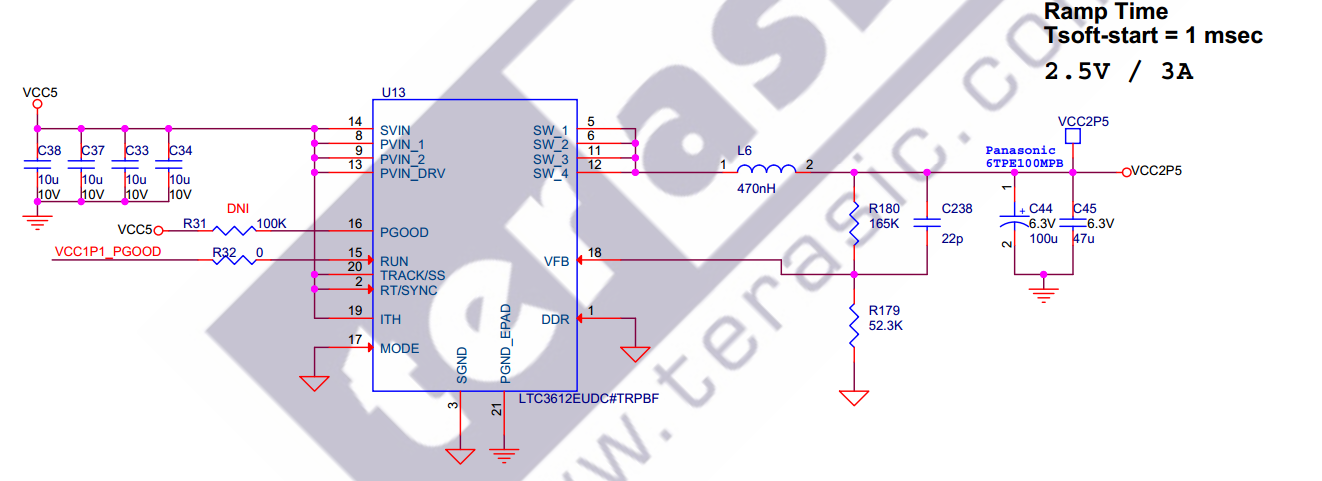

2.5V/3A:最后,就是把我深深迷惑到的2.5V/3A这个电源了。最开始一直在找这个2.5V究竟给哪个地方供电了,查了一圈,发现只是基本全部连接到SoC FPGA的管脚上了。心想,不至于吧。一个FPGA芯片,要一个2.5V/3A的电源干什么,内核也才3A啊。很早之前设计原理图时候就卡在这里了,一直想不通,甚至由此对Cyclone V SOC芯片的电源电路设计产生了畏惧,一直不敢去面对,直到今天再次翻出来看,才一拍大腿,恍然大悟:原来板子上的其他的1.2V/1.1A 、1.8V/1.1A 、1.5V/2.2A电源全是用的这个2.5V作为输入的。感情是为了降低电源耗散。所以这个2.5V/3A的电源设计出来主要不是给芯片用的,是给其他的LDO电源做输入的。初步计算了下:

浙公网安备 33010602011771号

浙公网安备 33010602011771号