01、LWIP协议

1、LWIP协议基础

LWIP协议是小型开源的TCP/IP协议栈。LWIP + MAC内核 + PHY芯片

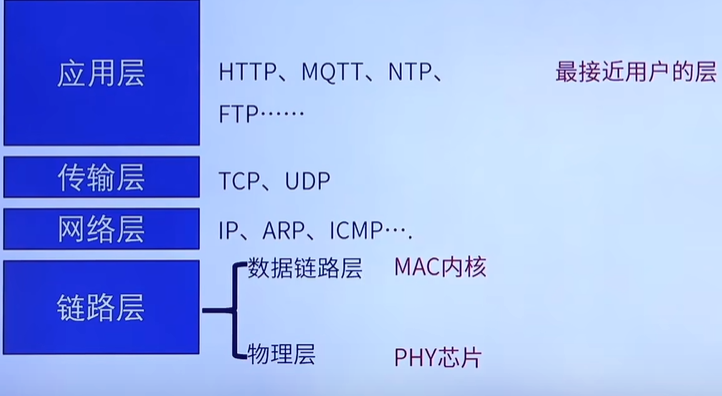

1.1、TCP/IP模型

物理层(PHY) :规定了传输信号所需要的物理电平、介质特征。

链路层( MAC):规定了数据帧能被网卡接收的条件,最常见的方式是利用网卡的 MAC 地址,发送方会在欲发送的数据帧的首部加上接收方网卡的 MAC 地址信息,接收方只有监听到属于自己的MAC 地址信息后,才会去接收并处理该数据。

网络层: 每台网络设备都应该有自己的网络地址,网络层规定了主机的网络地址该如何定义, 以及如何在网络地址和 MAC 地址之间进行映射,即 ARP 协议;

传输层: 网络层实现了数据包在主机之间的传递, 而一台主机内部可能运行着多个网络程序,传输层可以区分数据包是属于哪一个应用程序的, 可以说传输层实现了数据包端到端的传递。另外, 数据包在传输过程中可能会出现丢包、乱序和重复的现象,网络层并没有提供应对这些错误的机制, 而传输层可以解决这些问题,如 TCP 协议。

1.2、LwIP的特性

(1)支持 ARP 协议(以太网地址解析协议)。

(2)支持 ICMP 协议(控制报文协议),用于网络的调试与维护。

(3)支持 IGMP 协议(互联网组管理协议),可以实现多播数据的接收。

(4)支持 UDP 协议(用户数据报协议)。

(5)支持 TCP 协议(传输控制协议),包括阻塞控制、 RTT 估算、快速恢复和快速转发。

(6)支持 PPP 协议(点对点通信协议) ,支持 PPPoE。

(7)支持 DNS(域名解析)。

(8)支持 DHCP 协议,动态分配 IP 地址。

(9)支持 IP 协议,包括 IPv4、 IPv6 协议,支持 IP 分片与重装功能,多网络接口下的数据包转发。

(10)支持 SNMP 协议(简单网络管理协议)。

(11)支持 AUTOIP,自动 IP 地址配置。

(12)提供专门的内部回调接口(Raw API),用于提高应用程序性能。

(13)提供可选择的 Socket API、 NETCONN API (在多线程情况下使用) 。

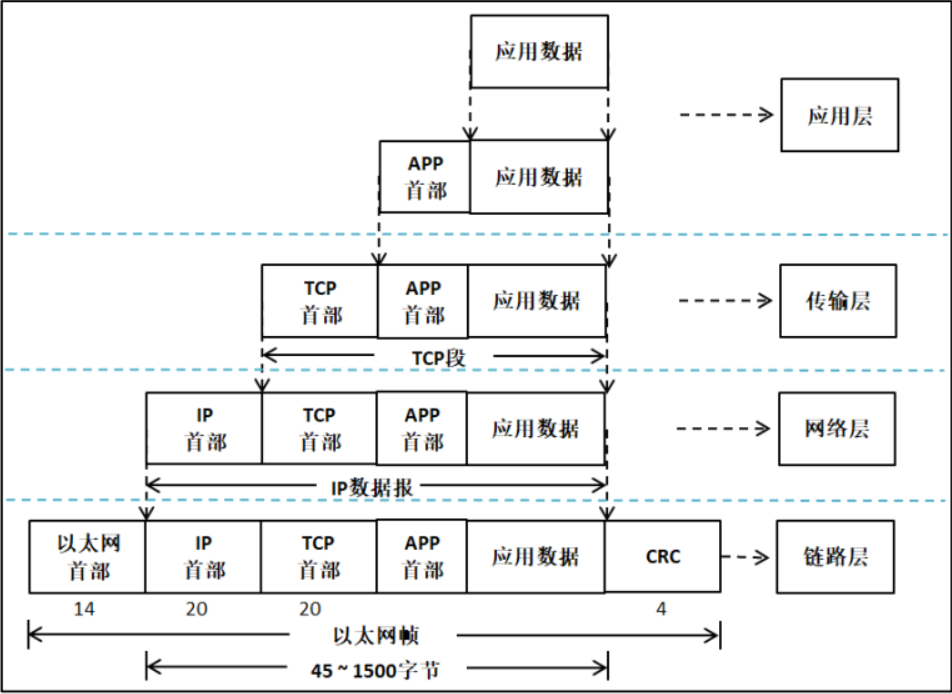

1.3、协议层报文间的封装与拆封

TCP协议数据包只能在传输层分包。

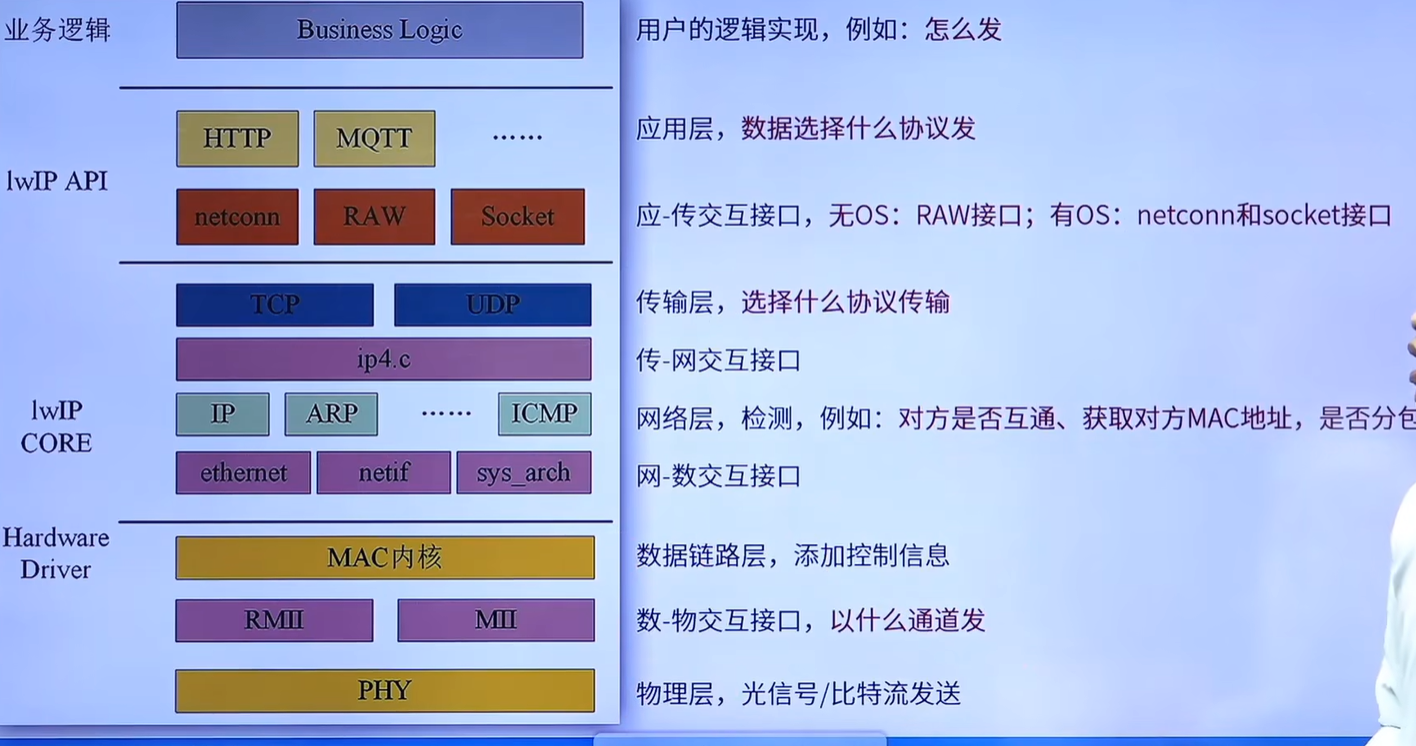

1.4、LWIP结构

enthernet:把网络层数据传递给MAC内核(数据链路层)。

netif:虚拟网卡

sys_arch: OS相关。

2、MAC简介

2.1、MAC内核特性**

1、传输速率:支持外部PHY接口实现10/100Mbit/s数据传输速率。

2、协议标准:符合IEEE802.3/3u的MII和RMII接口与快速以太网PHY通信。

3、工作模式:支持全双工和半双工。

4、站管理接口:支持通过MDIO接口配置和管理PHY设备。

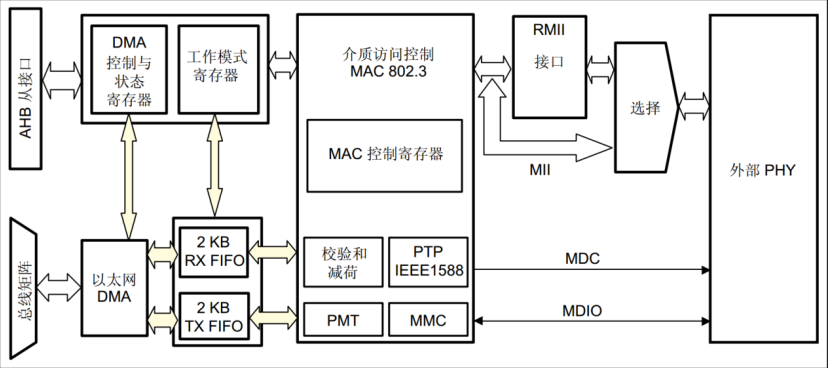

2.2、STM32的ETH框架

1、以太网数据包以DMA方式发送和接收。ETH 有专用的 DMA 控制器,它通过 AHB 主从接口与内核和存储器相连, AHB 主接口用于控制数据传输,而 AHB 从接口用于访问“控制与状态寄存器” (CSR)空间。在进行数据发送是,先将数据有存储器以 DMA 传输到发送 TX FIFO 进行缓冲,然后由 MAC 内核发送; 接收数据时, RX FIFO 先接收以太网数据帧,再由 DMA 传输至存储器。 以太网帧不超过1500kb。

2、MAC内核以太网帧发送时,给数据加上一些控制信息;以太网帧接收时,去掉控制信息。

3、PHY交互接口

(1)数据通道:介质接口。RMII/MII。

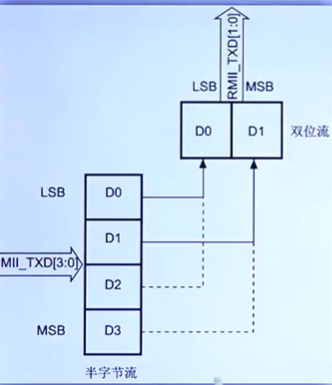

- 收发位宽

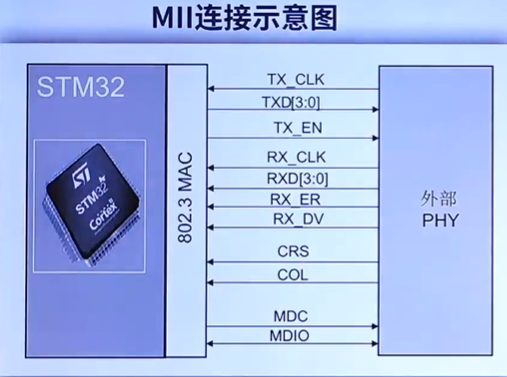

- MII:16个IO,时钟25MHZ,一个周期收发4位位宽。

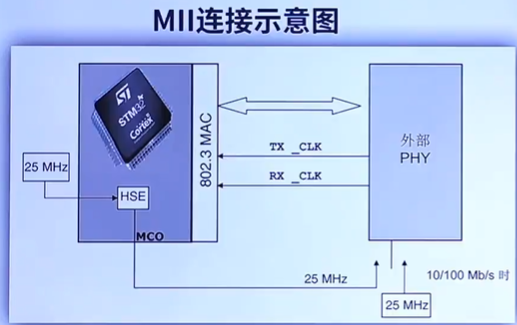

- MII介质接口的TX_CLK、RX_CLK由PHY芯片提供,它们会让MAC内核以这个时钟采集收发数据。

- RX_ER、RX_DV用来检测以太网帧是否有效性。CRS、COL在全双工模式下无效。

- MII时钟源有两个:MCO输出25MHZ、外部晶振输出25MHZ。

- MII接口中的TX_CLK、RX_CLK跟传输速率挂钩,10Mbit/s:2.5MHZ, 100Mbit/s:25MHZ。

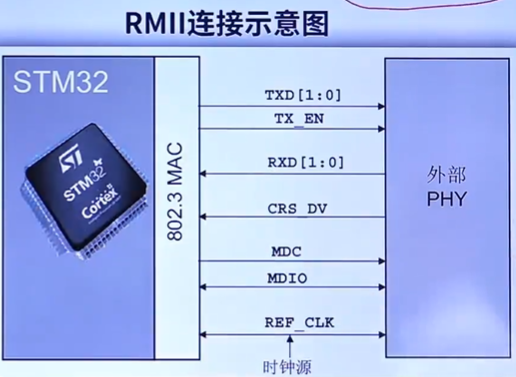

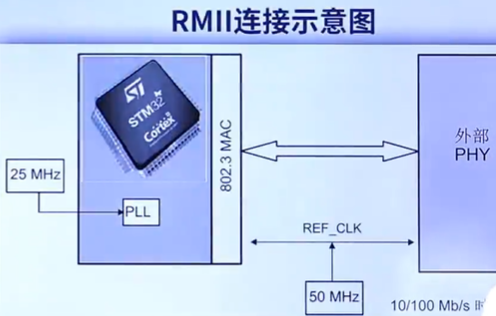

- RMII:9个IO,时钟50MHZ,一个周期收发2位位宽。

- RMII介质接口时钟REF_CLK。

- CRS_DV在全双工模式下无效。

- MII时钟源有两个:MCO经过倍频PLL输出50MHZ及外部晶振输出50MHZ(必须同时提供PHY和MAC)。

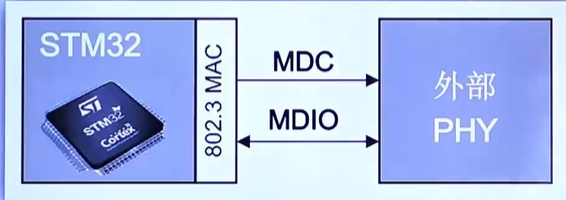

(2)管理通道:SMI站管理接口。

允许应用程序通过时钟线和数据线访问任意PHY寄存器,最多支持32个PHY访问。

- MDC:周期时钟引脚,最大频率2.5MHZ,由AHB时钟树分频得来。

- MDIC:数据输入输出比特流。

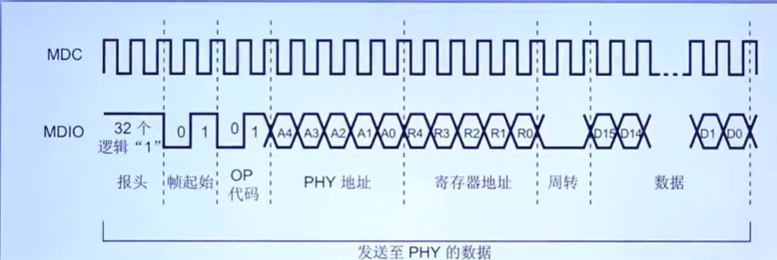

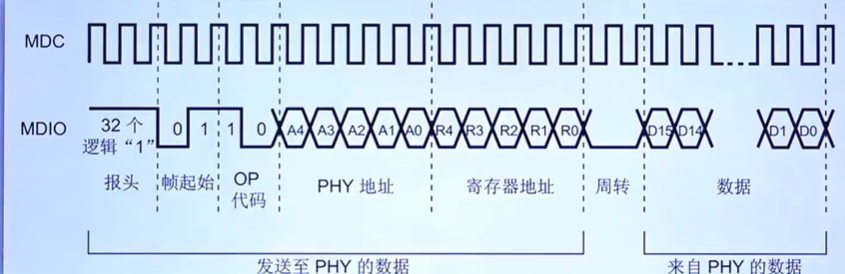

2.3、SMI帧格式

PADDR:PHY地址。

RADDR:寄存器地址。

数据位:16位,PHY寄存器16位。

MDIO时序和帧结构

- 写周期

- 读周期

浙公网安备 33010602011771号

浙公网安备 33010602011771号