基于FPGA设计10进制加法计数器

实验一,计数器的设计

环境:Quartus Prime 17.1 Standard Edition

FPGA型号为:Cylone 10 10CL55WF484C8

- 程序设计

`

--10进制加法计数器的VHDL程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT5 IS

PORT ( CLK,RST : IN STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0) );

END CNT5;

ARCHITECTURE DACC OF CNT5 IS

SIGNAL Q : STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

PROCESS(CLK,RST )

BEGIN

IF RST = '0' THEN Q<="0000";

ELSIF CLK'EVENT AND CLK = '1' THEN

IF Q<9 THEN Q<=Q+1; --计数小于9,继续累加

ELSE Q <=(OTHERS=>'0'); --否则计数回1

END IF;

END IF;

END PROCESS;

DOUT<=Q ;

END;

`

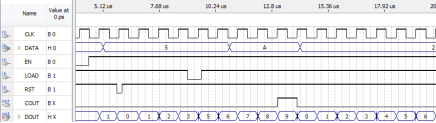

2.仿真结果

浙公网安备 33010602011771号

浙公网安备 33010602011771号