Verdi学习笔记

之前有一篇博客《VCS+DVE+Verdi+Makefile使用》里涉及了一些 Verdi 工具的用法,这里 Copy 过来,再丰富一下更多的 Verdi 的知识。Verdi 最开始由 Novas 公司设计,2008 年被台湾的 EDA 厂家 SpringSoft(源笙)收购,2012 年 Synopsys(新思)收购了 SpringSoft 公司,此后 Verdi 才正式属于 Synopsys。Verdi 之前的版本叫 Debussy,二者都是 19 世纪的古典音乐大师,可能老板是个音乐迷吧,取了个大师名。

Verdi 不是仿真器,只能查看波形,查看波形时必须引入 fsdb 文件(.fsdb/.vf),该文件可由 EDA 工具的仿真器来实现(如 Synopsys 的 VCS,Cadence 的 irun/xrun,Mentor 的 Questa),这个过程也称为 Dump 波形文件。一共有两种方式可以产生 fsdb 文件:

- Verilog系统函数

- TB内手写,大多用这种方法。

- Ucli/Tcl接口脚本

- 快捷但较复杂,不利于新手

1 Verdi配置信息

1.1 配置文件

Verdi 的 GUI 选项或窗口变动后,会自动同步到当前运行目录的 novas.rc 和 novas.conf 文件中:

- novas.rc 存储着各种 preferences 选项,诸如“font”、“color”等;

- novas.conf 存储着窗口布局信息,诸如“dock/undock”、“maximize/restore”、“display/hide”等;

1.2 配置优先级

但是下次新开 verdi 会丢失这些配置,得重新配置。这是因为 verdi 按某种优先级去检索配置信息,如下所示:

//================================================ 1、命令指定

-rcFile <filename>

-guiConf <filename>

//================================================ 2、系统环境

setenv NOVAS_RC <path>/novas.rc

setenv NOVAS_GUICONF <path>/novas.conf

//================================================ 3、运行目录

./novas.rc

./novas.conf

//================================================ 4、HOME目录

~/novas.rc

~/novas.conf

//================================================ 5、安装目录

<install_path>/etc/novas.rc命令指定不常用,推荐第二个方法。我们设置好各种配置信息后,将当前目录下的 novas.rc 和 novas.conf 文件复制到 $HOME 目录下(verdi 自己也会产生配置文件在 $HOME下),然后在自己 .cshrc_local 文件中指定环境变量,指向自己 $HOME 下的文件。这样不管什么目录打开 verdi,都是自己喜欢的配置。

1.3 常用配置

(1)信号左对齐

Waveform界面的波形信号名默认右对齐,可以这样修改:

Tools >>> Preferences >>> Waveform >>> View Options,将 Alignment 改成”Left“。

(2)字体大小

Verdi 默认字体较小,现在多是 2K/4K 屏,可以这样调大字体:

Tools >>> Preferences >>> General >>> Appearance,将 Font 改成 14,显示效果比较好。

(3)波形样式

Vivado 自带的 iSim 工具显示的高电平波形有一层淡淡的涂色,使得读者很容易区分高电平和低电平,Verdi 中可以这样实现。

Tools >>> Preferences >>> Waveform >>> Value System,将 Item=1 行,Stipple 选一个图案,Shape 选”Rectangle(with outline)。

(4)跳转信号

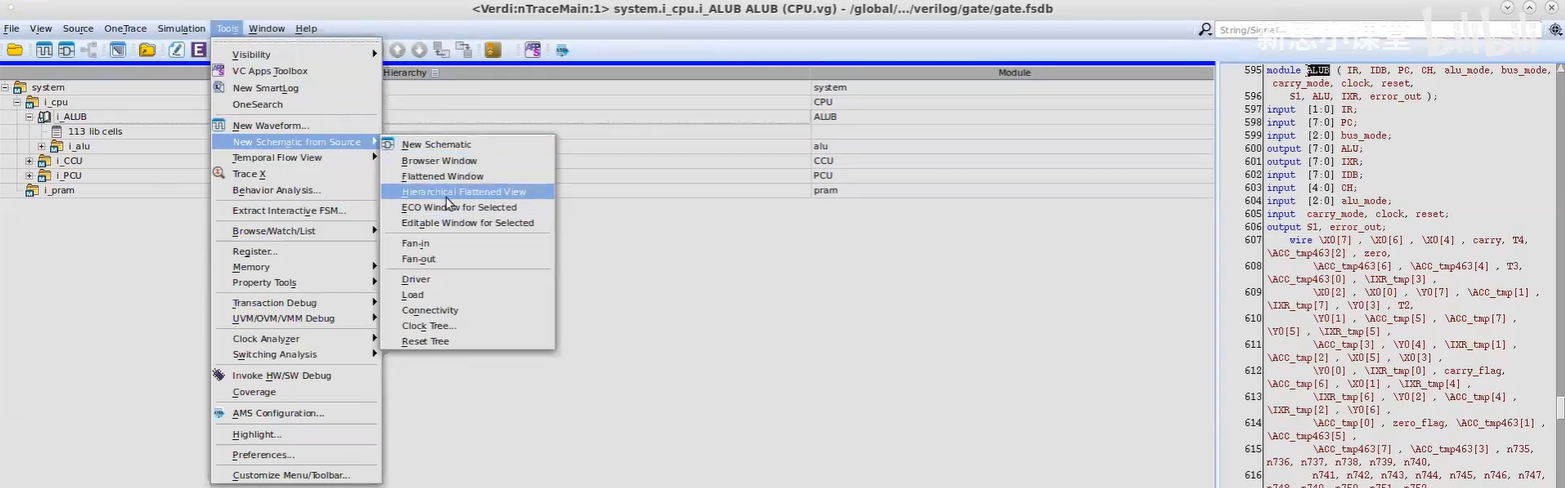

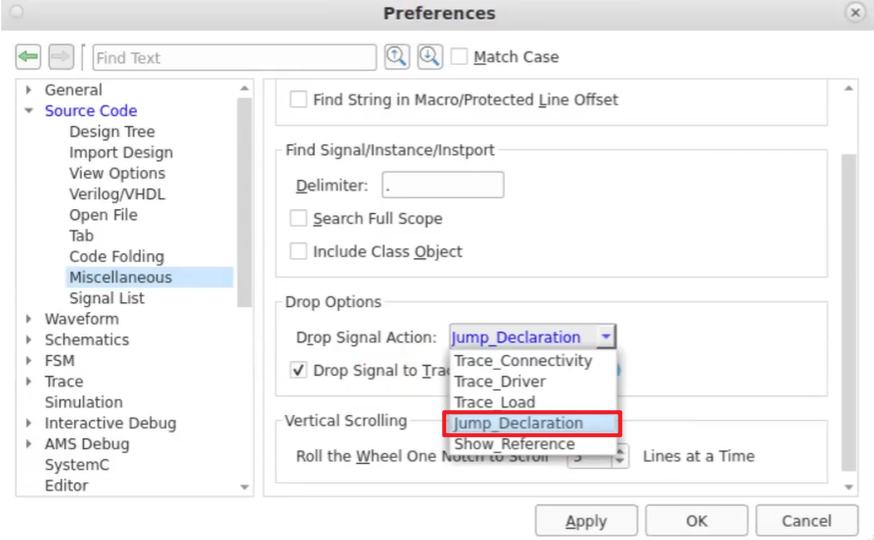

拖拽波形窗口的信号到代码窗口会自动跳转到Trace处,想实现跳转到该信号的”definition“处,需要这样设置:

Tools >>> Preferences >>> Source Code >>> Miscellaneous,将 Drop Signal Action 改成”Jump Declaration“。

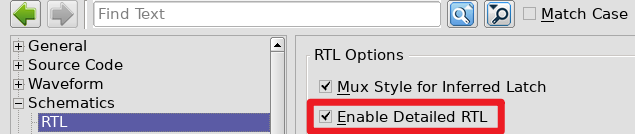

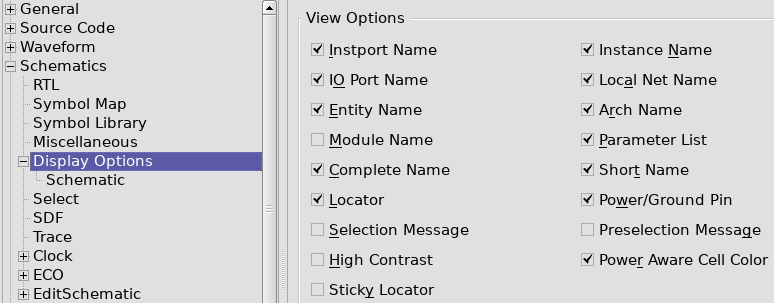

(5)nSchema

nSchema 窗口的 view 只能临时设置,建议到 Preference 处配置一下,即可永久生效:

- Tools >>> Preferences >>> Schematics >>> RTL,勾选”Enable Detailed RTL“;

- Tools >>> Preferences >>> Schematics >>> Display Options,根据自己喜好,勾选 View Options 下的方框;

2 Verdi使用流程

2.1 产生fsdb文件

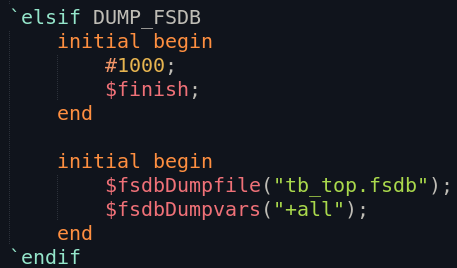

在 testbench 中添加 verdi 系统函数,即可在执行 VCS 仿真时产生fsdb文件。

更多 verdi 系统函数可以查看 verdi 官方手册,即下面这个:

2.2 打开verdi界面

(1)code only

verdi -f filelist.f -top tb_top &- -f:指定filelist文件;

- -top:指定top名;

(2)fsdb/ztdb/vf

verdi -ssf tb_top.fsdb -sswr signal.rc &- -ssf:指定fsdb/ztdb/vf文件;

- -sswr:指定波形存储文件;

一般指定了 fsdb 文件就不用指定 filelist 和 top 了,这个指令是最使用的,工作中我多是用这个命令打开 DV 的波形。

(3)-dbdir

有时候只指明 fsdb 文件,打开的 verdi 没有层次结构,或者缺些东西,那么需要指定 vcs 编译生成的库

verdi -ssf tb_top.fsdb -dbdir simv.daidir &- -ssf:指定fsdb/ztdb/vf文件;

- -dbdir:指定编译数据库;

3 Verdi命令和快捷键

3.1 Verdi常用命令

Verdi 的操作技巧比较多,可以翻阅手册《Verdi and Siloti Command Reference》。

|

选项 |

说明 |

|

-doc |

打开userGuide |

|

-sv |

支持systemverilog语法 |

|

+systemverilogext+.sv |

指定sv文件的后缀 |

|

-ssv |

取消-v指定的library为lib cell |

|

-ssy |

取消-y指定的library为lib cell |

|

-ssz |

忽略`celldefine的compiler指令 |

|

-top tb |

指定整个环境的top名称为tb |

|

-vc |

支持DirectC语法 |

|

-f |

指定文件列表 |

|

-ssf |

指定波形文件 |

|

-sswr |

指定signal.rc文件 |

|

-preTitle |

指定GUI界面名称 |

|

nologo |

关闭欢迎界面 |

|

& |

使Verdi后台运行,不占用terminal |

|

+define |

代码中没有指定Define,导致代码灰色,则可以打开verdi时指定 |

3.2 Verdi常用快捷键

Verdi 比较多快捷键,需要多多练习才能够掌握,下面是最常用的一些功能:

|

目标 |

快捷键 |

|

查看波形 |

Ctrl+W |

|

100%显示 |

f |

|

缩小波形 |

z |

|

放大波形 |

Z |

|

移动信号 |

中键选择位置+信号+M |

|

拷贝波形 |

Ctrl+P |

|

粘贴波形 |

中间选择位置+Ins |

|

删除信号 |

Del |

|

显示信号的绝对路径 |

h |

|

重仿真后刷新波形 |

L |

|

代码中出现当前时刻的值 |

x |

|

直接添加信号 |

g |

|

修改波形颜色 |

c或t |

|

保存波形信号列表 |

r |

更多知识可以查看一些博客总结:https://blog.csdn.net/immeatea_aun/article/details/80961258

4 Verdi常用技巧

4.1 fsdb相关

(1)单独打开fsdb

使用命令nWave xxx.fsdb &即可。再用快捷键 G 添加信号。

(2)切割fsdb文件

有时需要将 fsdb 文件提供给 AE 帮忙分析,但是 dump 下来的波形实在太大了,而且包含了很多不该透露的层次结构,这时就需要对 fsdb 文件进行切割,使用的命令是 “fsdbextract”。

fsdbextract source.fsdb -bt 10us -et 20us -s top/u_module1/u_module2/ -level 0 -o output.fsdb- source.fsdb:需要切割的fsdb文件名

- -bt:begin time

- -et:end time

- -s:层次结构

- -level 0:该结构及其所有子层级

- -o output.fsdb:切割后的fsdb文件名

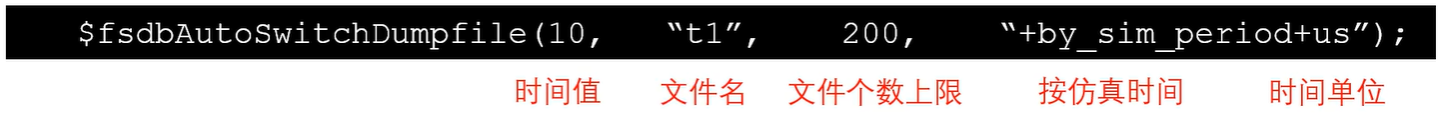

(3)仿真自动切割fsdb文件

按仿真时间自动切割:

按现实时间自动切割:

4.2 打开verdi快一点

(1)环境变量

lscpu查看系统支持的thread数量;- .cshrc_local中设置环境变量

setenv FFR_MT_THREAD_COUNT n,n为thread数量。 - source ~/.cshrc_local

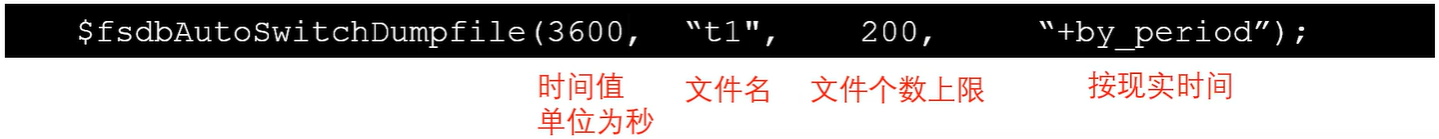

(2)preload

Verdi 根据一个预先写好的配置文件去 load 用户指定的范围:

verdi -perload Config_file -dbdir ./simv.daidir(3)smart_load

Verdi 初始只 load 顶层,根据 debug 操作自动 load 相应范围:

verdi -smart_load_kdb -dbdir ./simv.daidir4.3 代码显示

(1)显示信号值

打开波形后,光标停在某个时刻,按一下 x 键,代码会显示这个时刻的值,方便阅读理解。

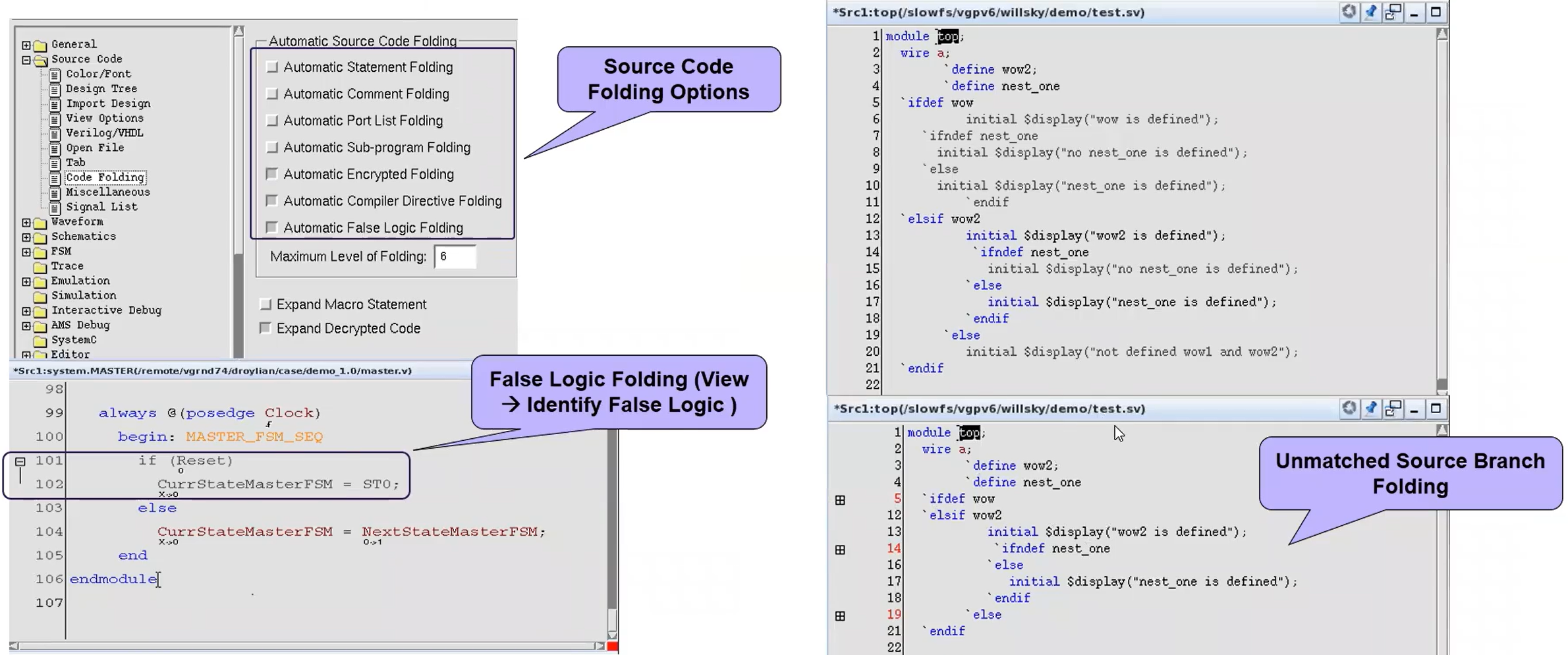

(2)折叠代码

折叠代码可以让代码更方便阅读,不看的部分折叠住,只需要选中行,然后点击键盘的“+”或“-”来展开和折叠代码,如 always 块等。设置如下:

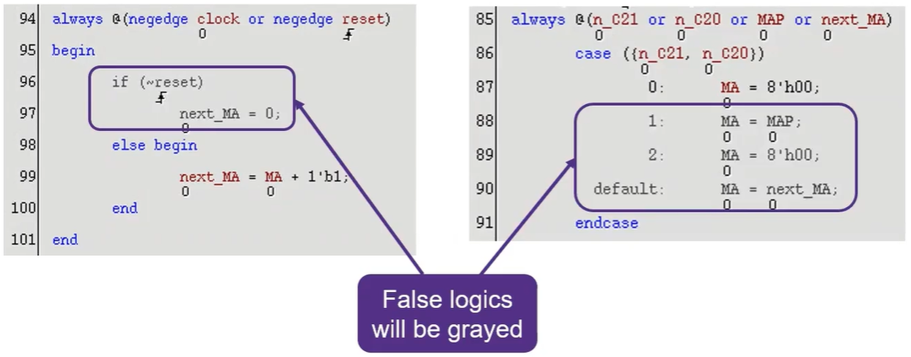

(3)假逻辑变灰

View >>> Identify False Logic,可以将不活动的逻辑代码变灰,方便代码阅读。

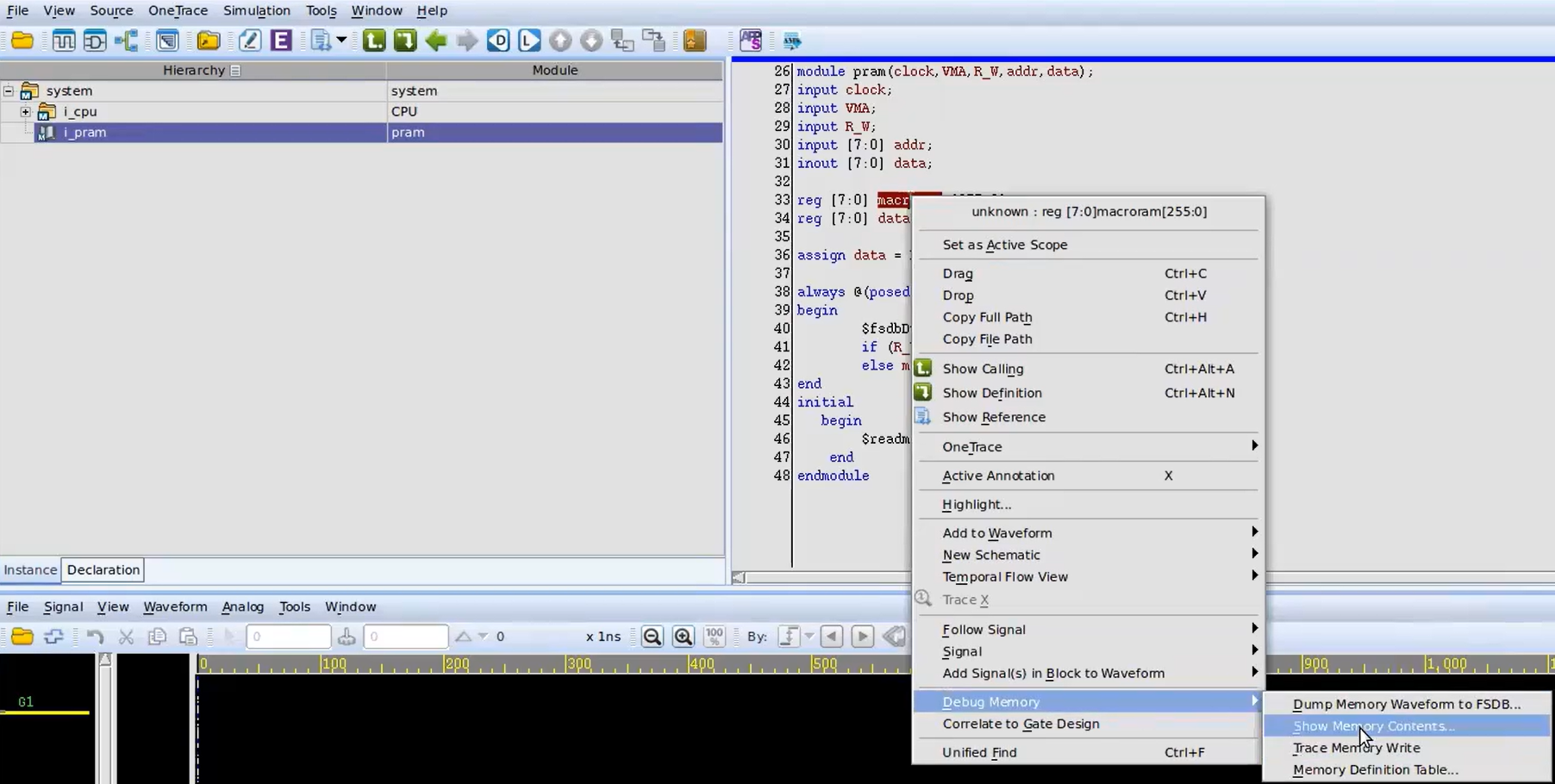

(4)显示mem值

4.4 波形显示

(1)波形变色

- 按一下 C 键,可以选择波形颜色;

- 按一下 T 键,可以切换波形颜色;

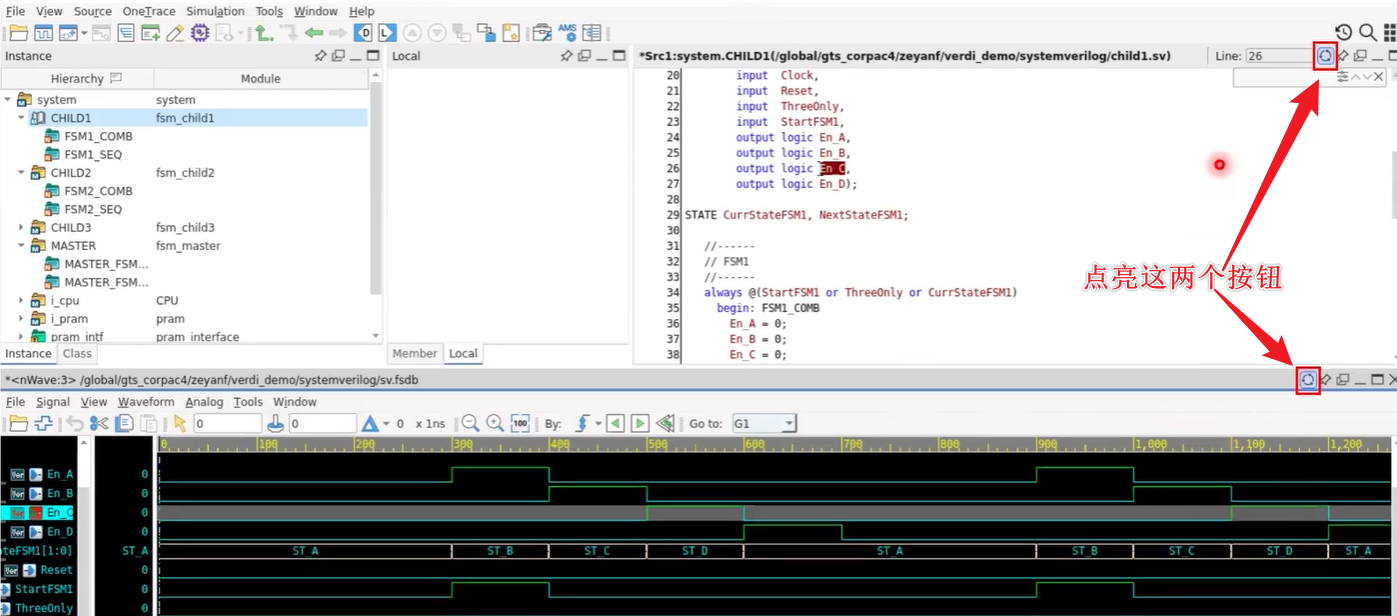

(2)状态机名称

打开波形后,拉好状态机信号,点击一下电路图的图标 ,波形上就自动显示状态机名称了。

,波形上就自动显示状态机名称了。

(3)边沿个数

选中信号,右键 Add/Remove >>> Add Counter Signal by >>> Any Change / Rising Edge / Failing Edge。

(4)时钟频率值

用鼠标左键将光标放在时钟上升沿起点,鼠标中间将另一个光标放在下一个时钟的上升沿,点击下面按钮即可显示时钟频率,这是最常用的办法了。

但是在变频 case 中,需要频繁这样操作很麻烦,那么可以用下面的方法将频率值打印出来。

- 选中时钟,点击 Analog >>> Capture Frequency。

- 选中新出现的波形,鼠标右键选择“Digital Waveform”

(5)带宽利用率

- 选中 rvalid 和 rready,点击 Logical Operation...,创建“&"的新信号。

- 选中新信号,用光标确定时间段,右键点击 Signal Event Report...

- 查看”Duty Cycle“,即是带宽利用率。

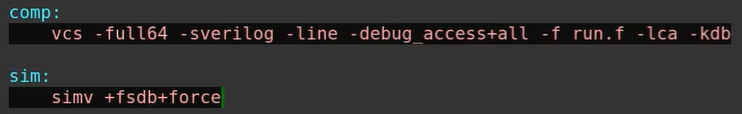

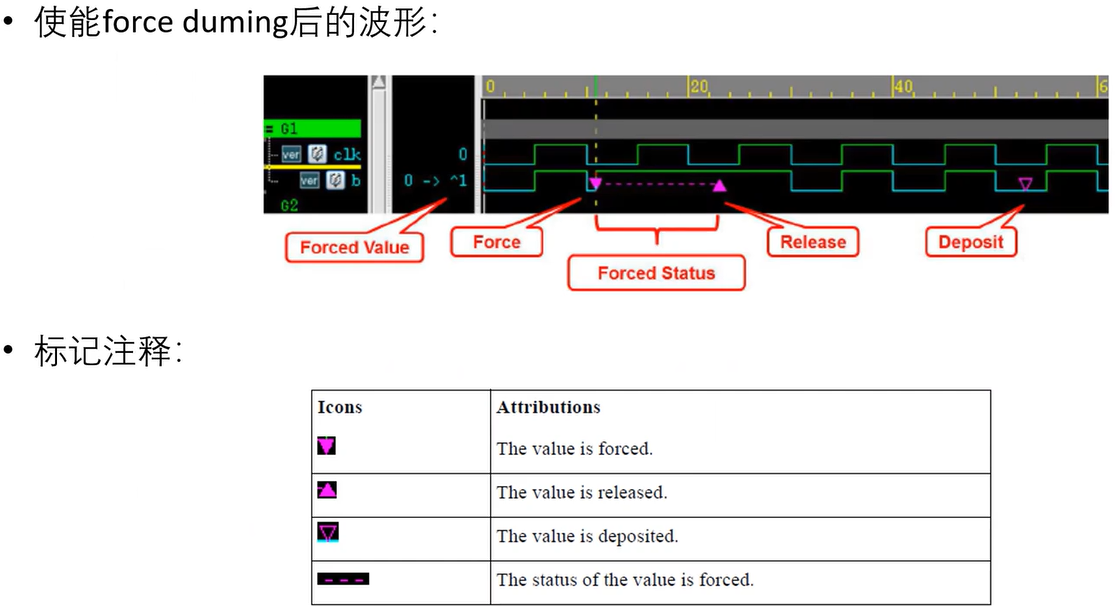

(6)force信息

- 步骤一

- 在 VCS 编译选项种加上”-debug_access+f“或者”-debug_access+all“

- 步骤二

- 在 simv 运行选项中加上”+fsdb+force“

- 或者,定义环境变量”setenv FSDB_FORCE 1“

4.5 Trace功能

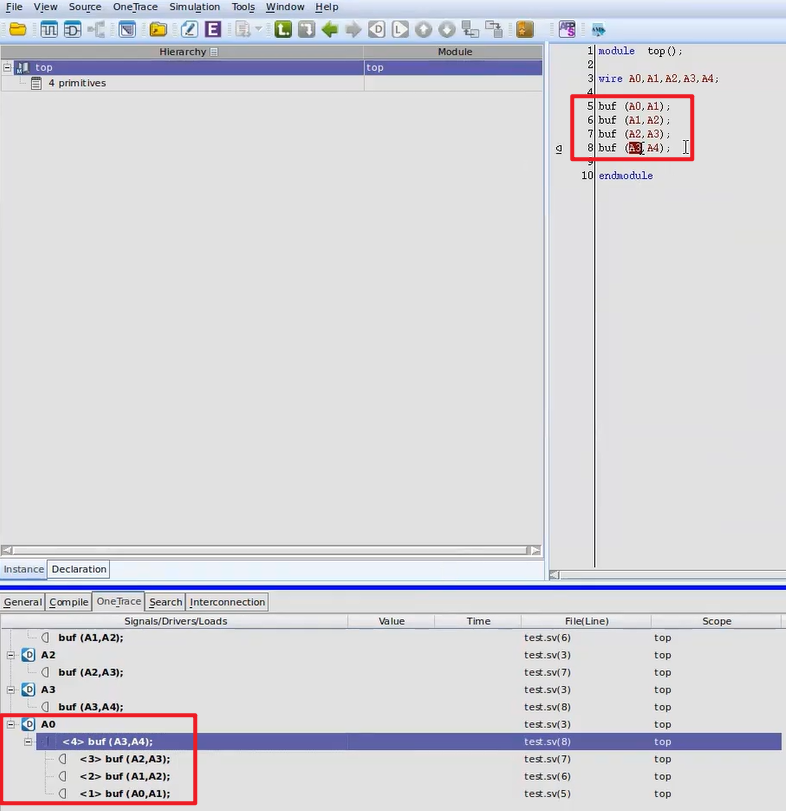

(1)OneTrace Chain_Driver

想 Trace A0,一个个 Trace 则会依次 A0 >>> A1 >>> A2 >>> A3 >>> A4,可以选中 A0,鼠标右键选择”OneTrace >>> Chain_Driver“,直接追到底。

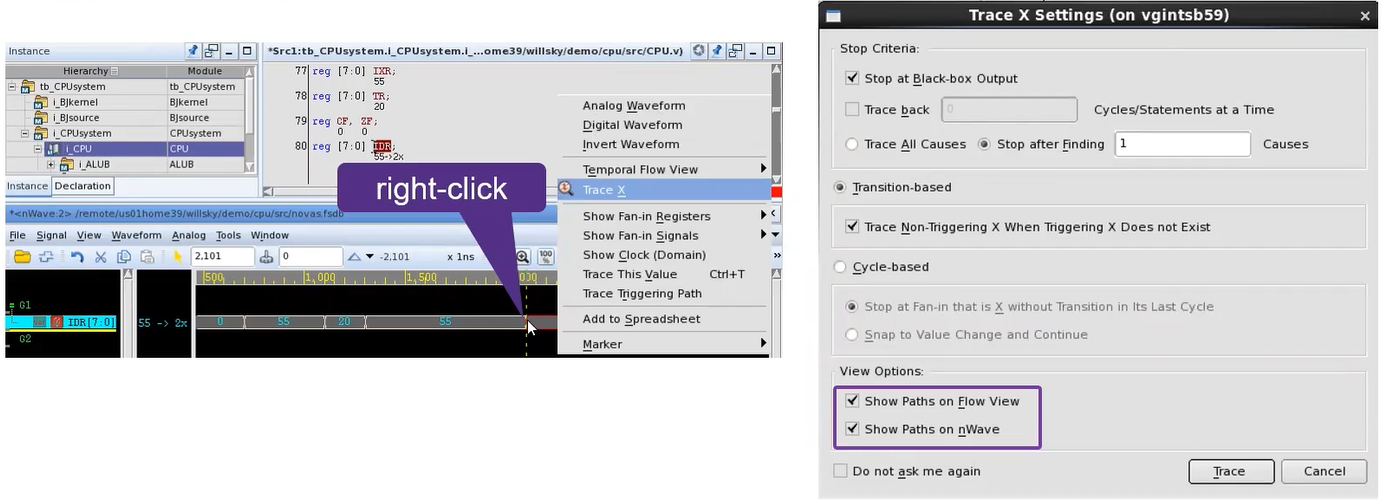

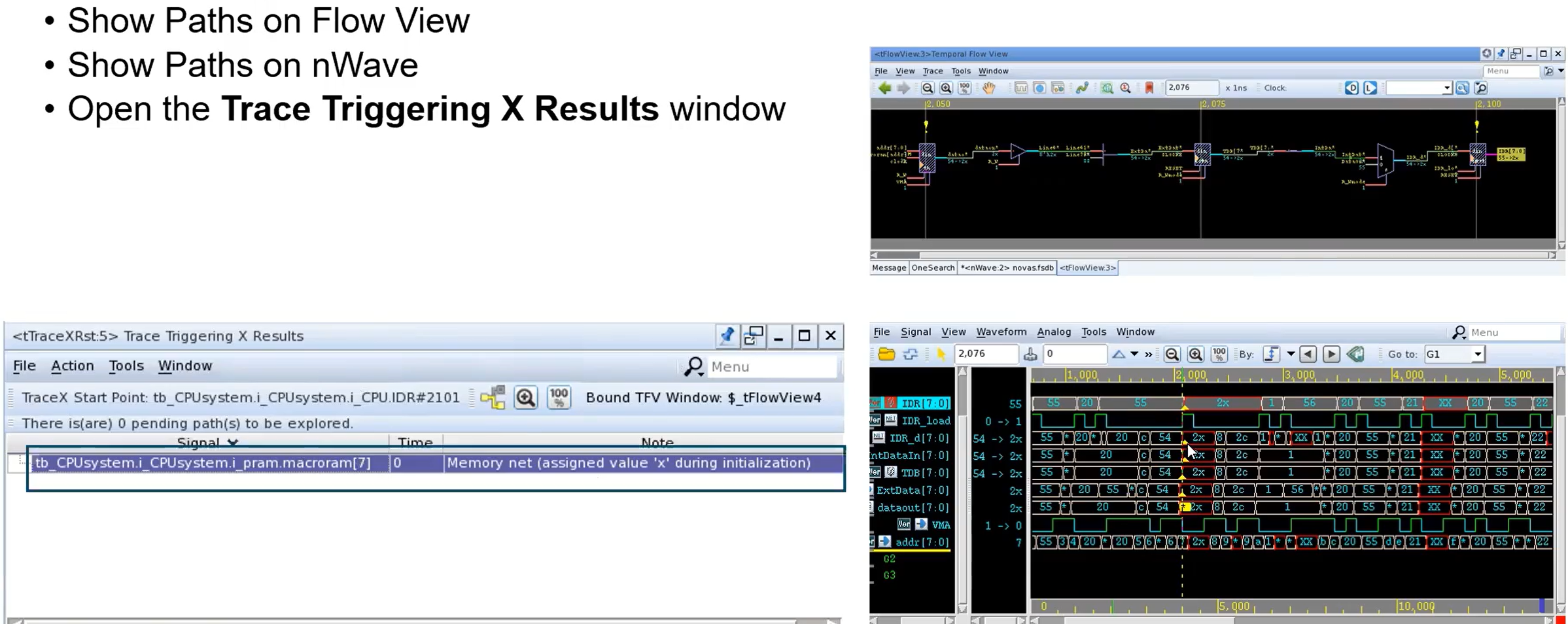

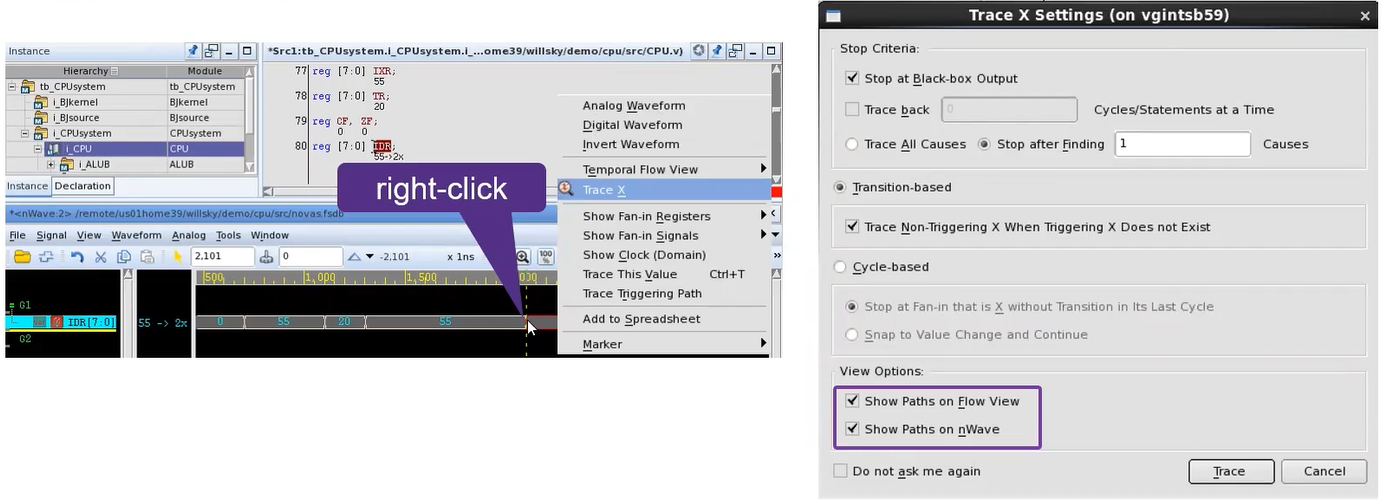

(2)Trace X

波形中出现 X 态,可以右键选择”Trace X“,如果不对劲看看设置有没有问题。

结果会在下面三个地方显示出来:

此外,x 态问题也可以用选项 xrca 来帮助定位,见下文。

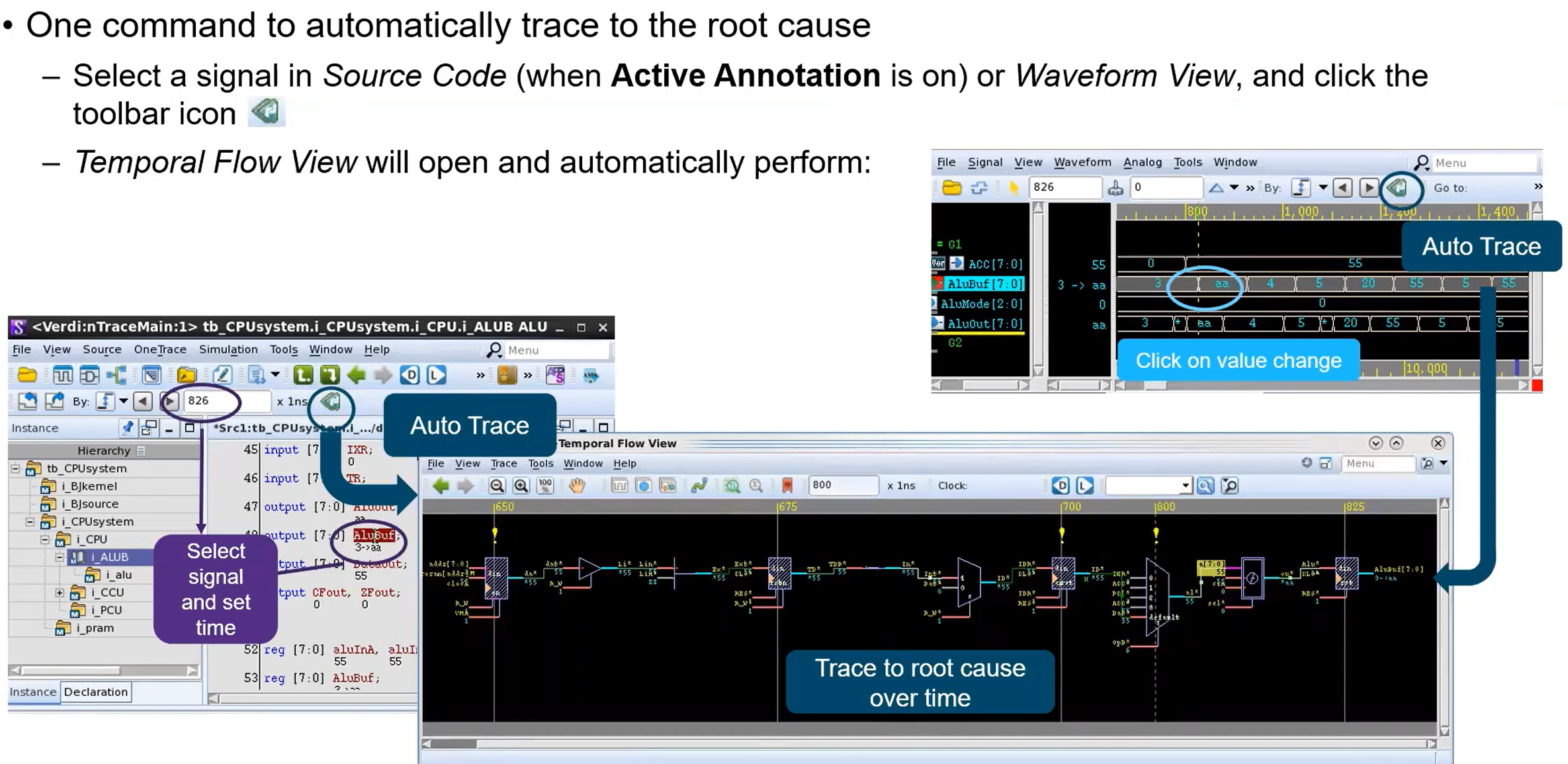

(3)Auto Trace

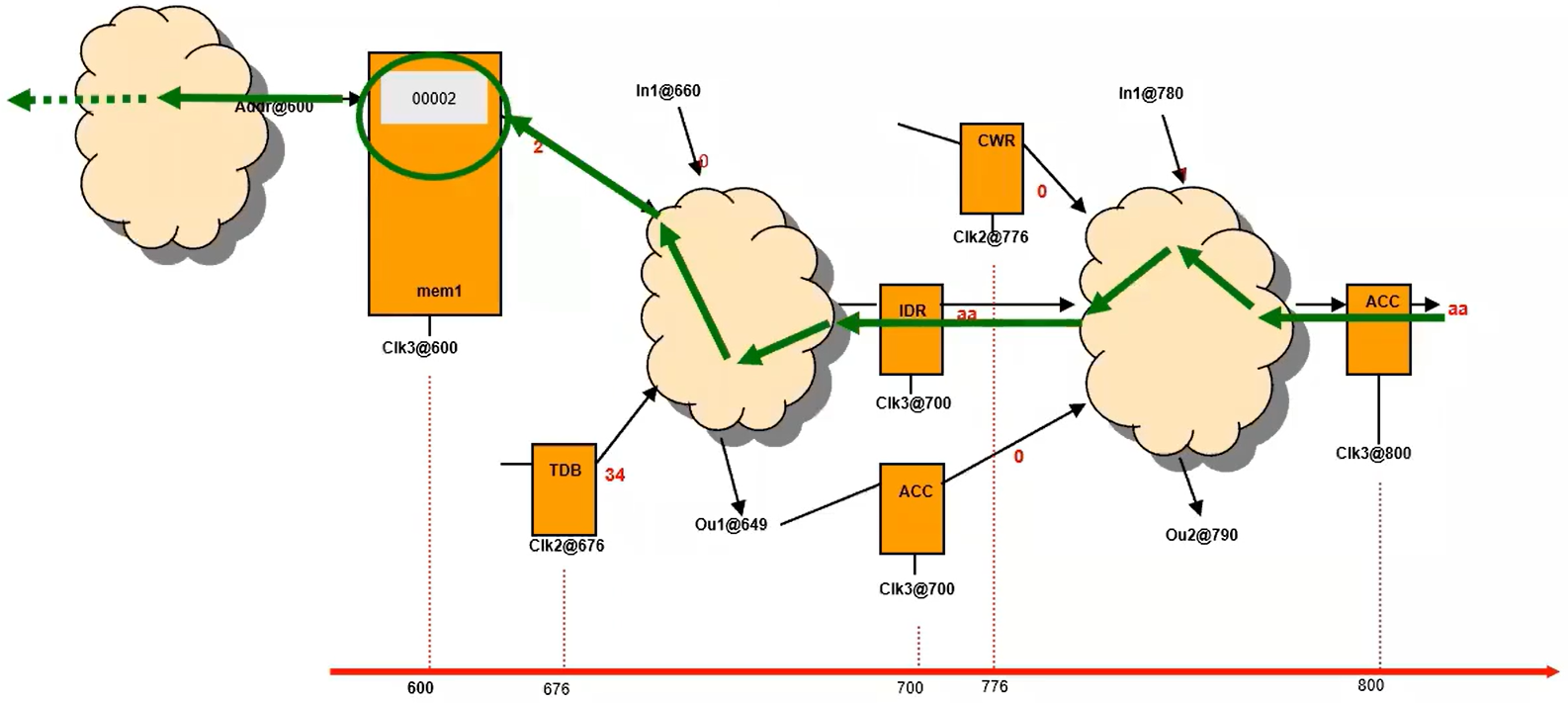

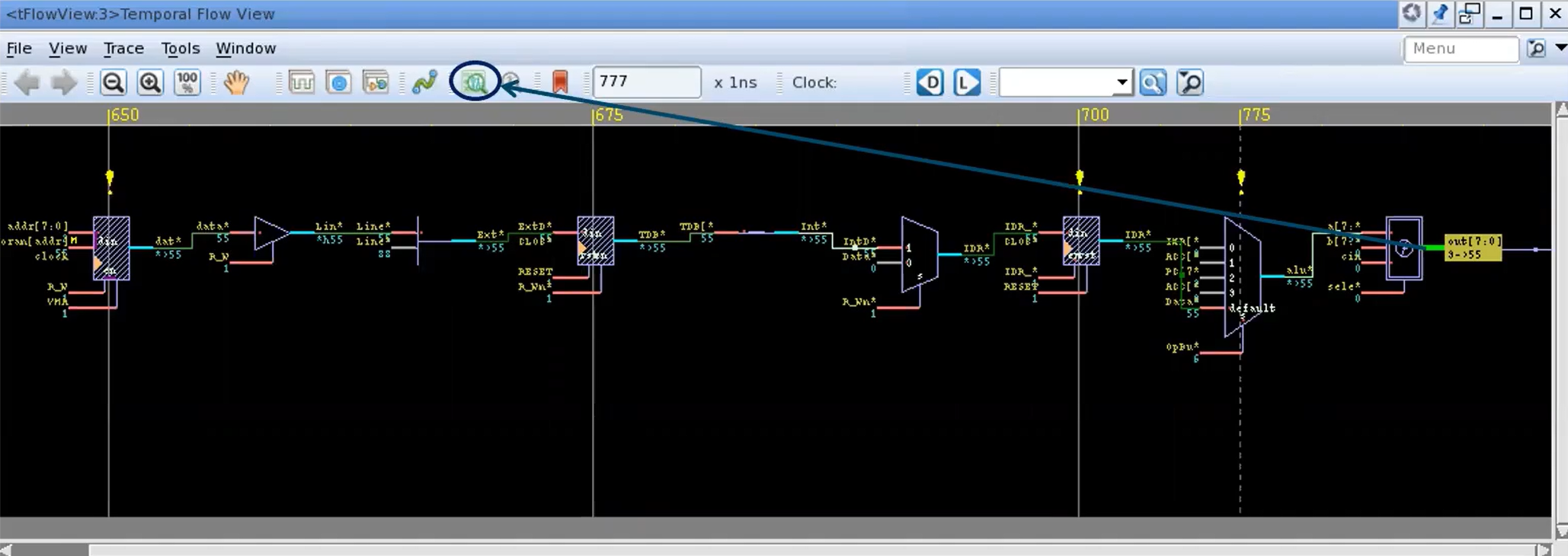

(4)TFV

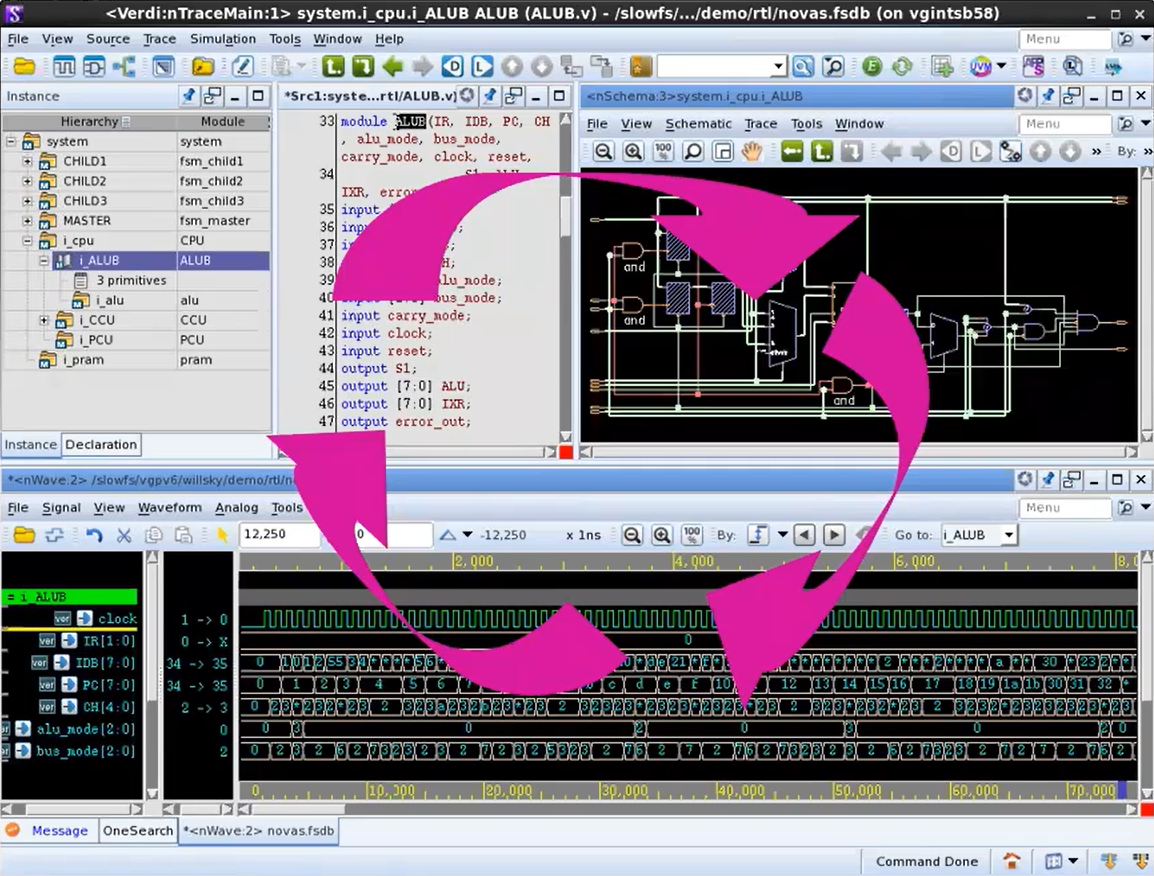

大部分时候追波形都是点三个窗口来回看,一点点找 root cause:

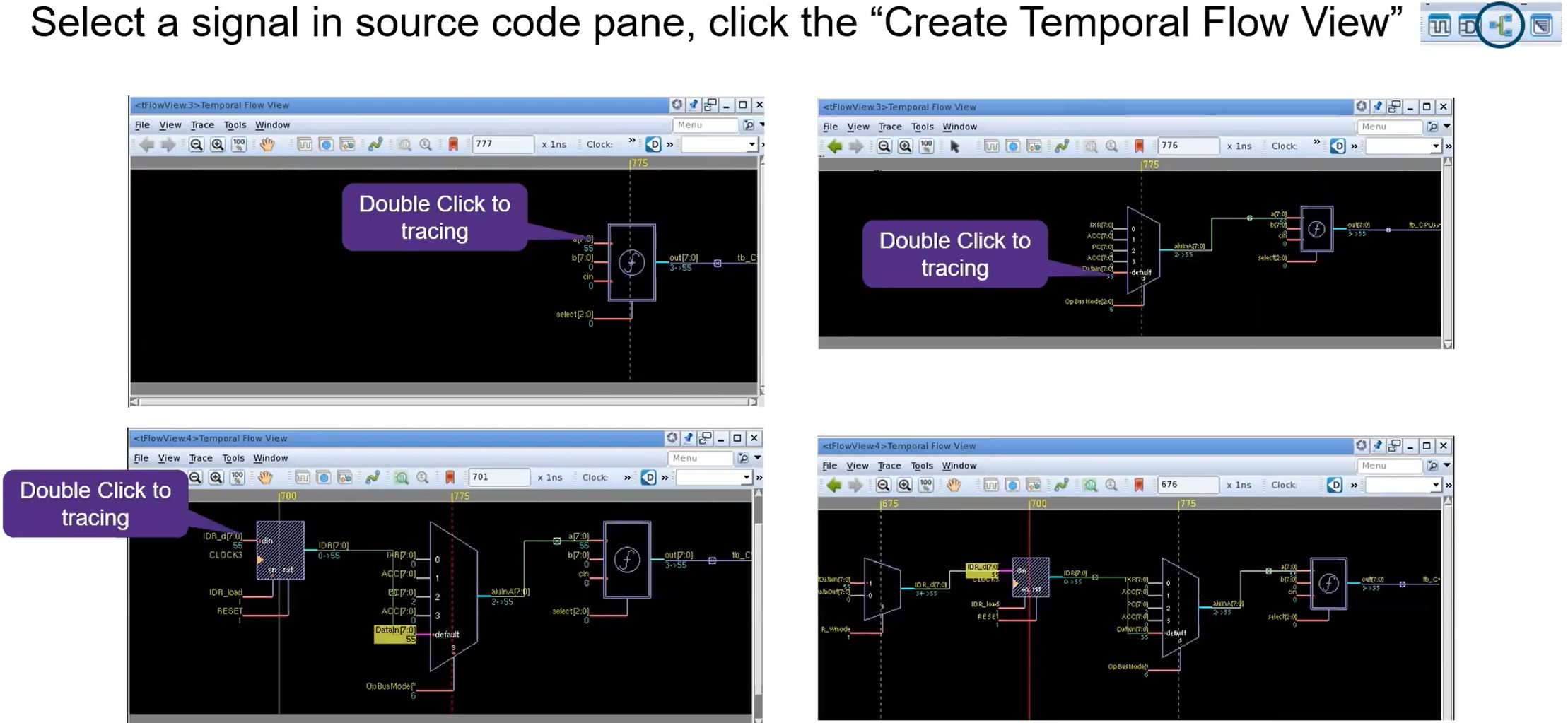

可以试试 TFV(Temporal Flow View)的方式追波形:

具体用法:

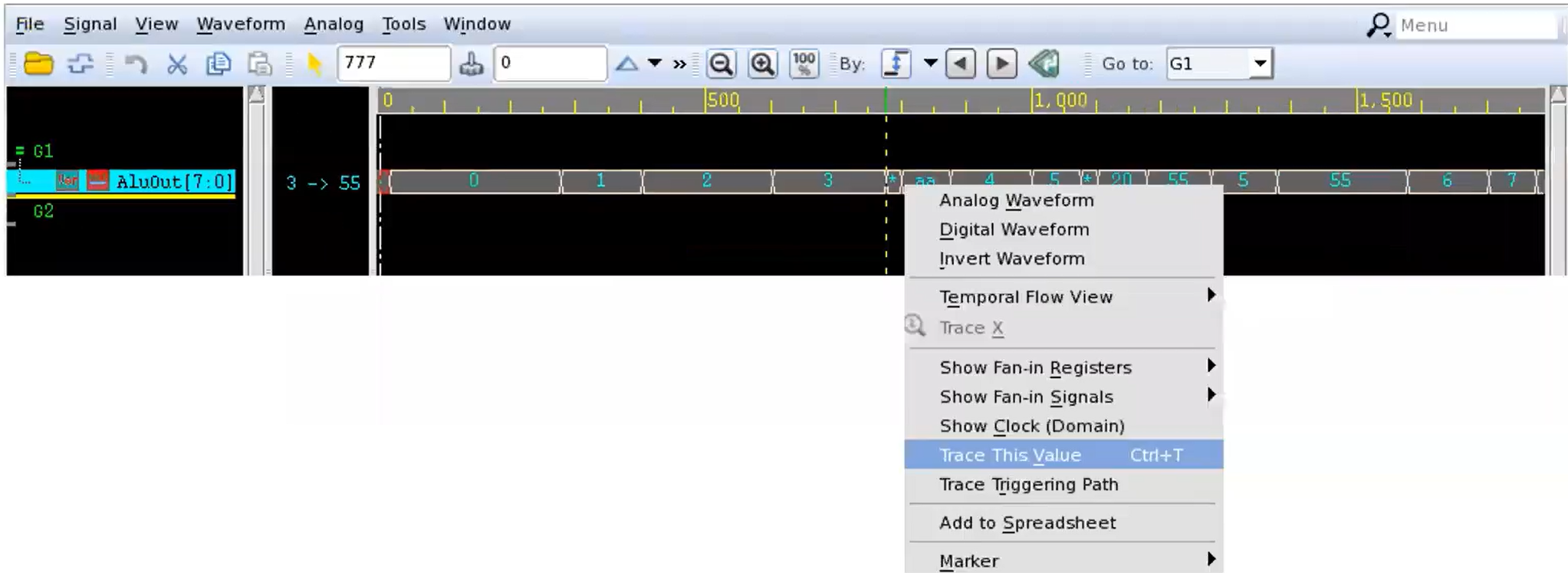

如果不想一个个的点,那么可以选中信号,点击”Trace This Value“,直接显示所有:

Waveform上也可以点出这个界面:

4.6 查找vio

(1)Trace X

波形中出现 X 态,可以右键选择”Trace X“,如果不对劲看看设置有没有问题。

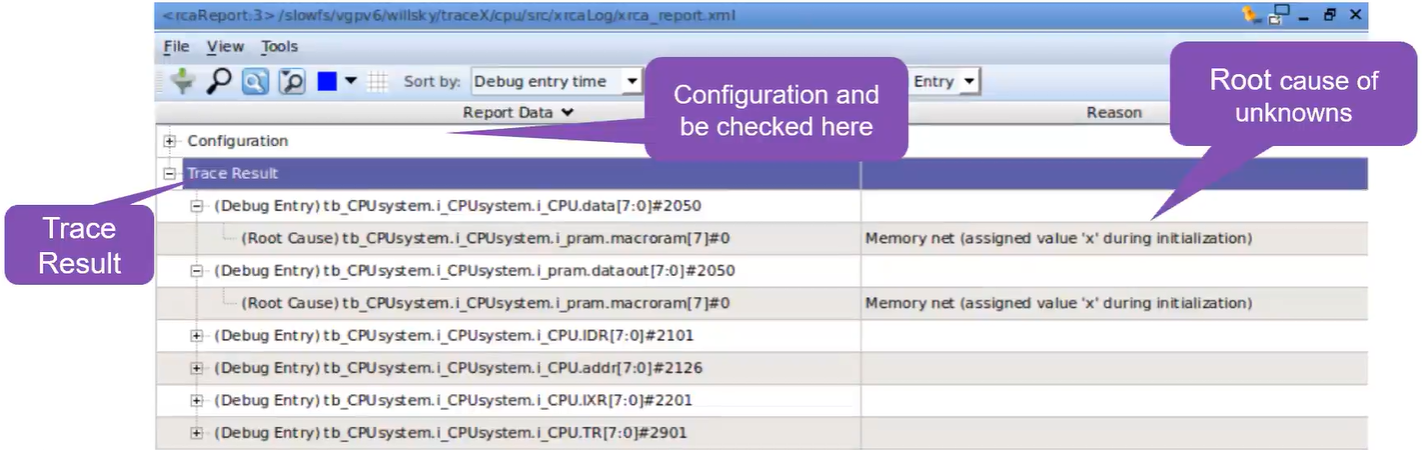

(2)xrca选项

用途:

- 手动模式:

- 经用信号列表捕获了未知数,用户给文件加上-signal_file 选项;

- xrca实用程序跟踪给定的未知因素并找到根本原因;

- 自动模式:

- 无需给出信号列表,xrca 实用程序将从导入 FSDB 文件中查找所有未知项,并从那时开始跟踪;

例子:

xrca -lca -dbdir simv.daidir -ssf rtl.fsdb

xrca -lca -ssf rtl.fsdb

xrca -lca -dbdir simv.daidir -ssf rtl.fsdb -signal_file signal.listreport 保存在 ./xrcaLog/xrca_report.xml,更多选项可以用”xrca -lca -h“查看。

report 是 xml 格式,可以用 verdi 打开查看,命令是verdi -apex -load_trace_report ./xrcaLog/xrca_report.xml &

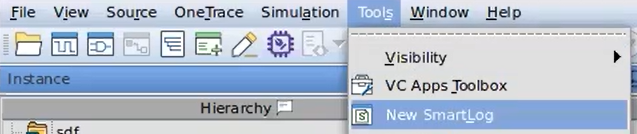

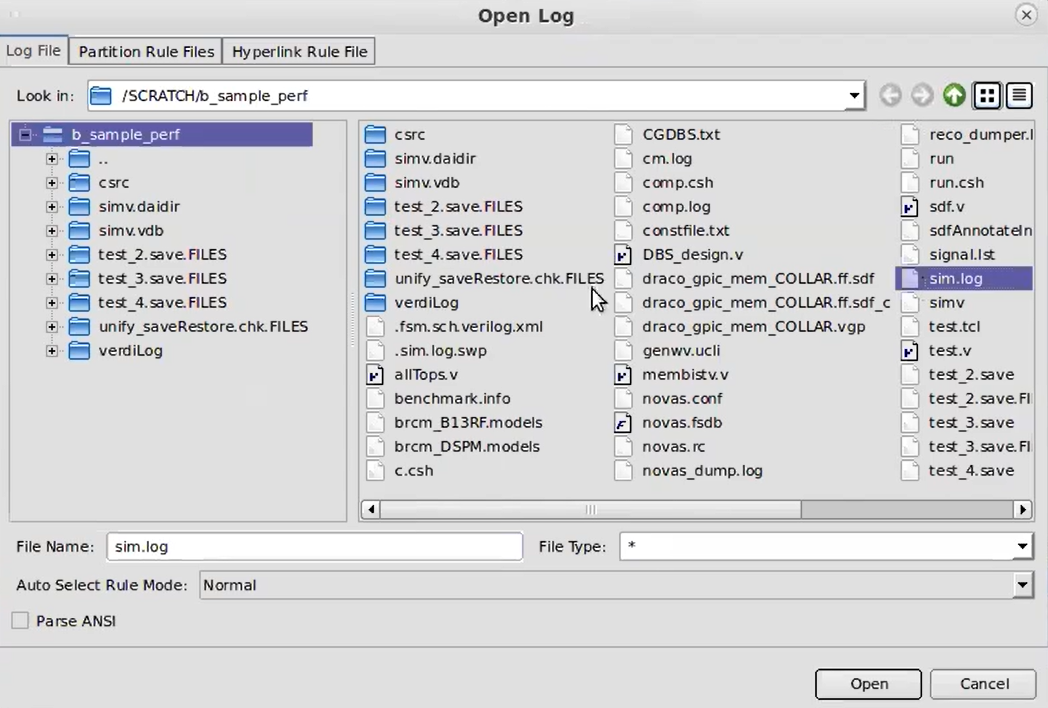

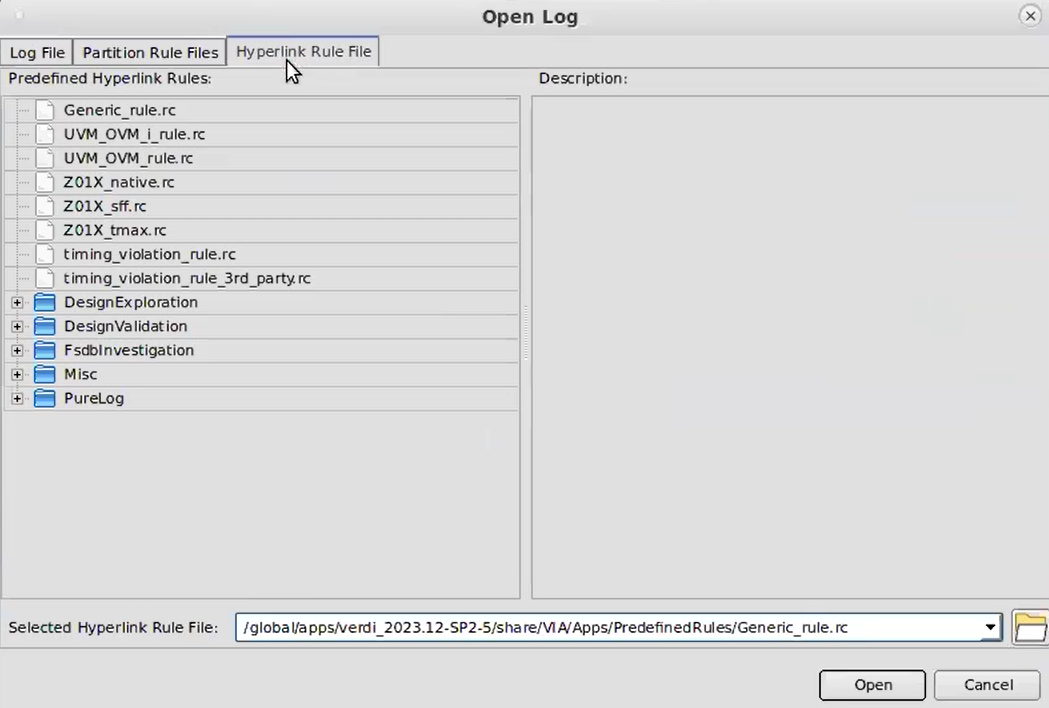

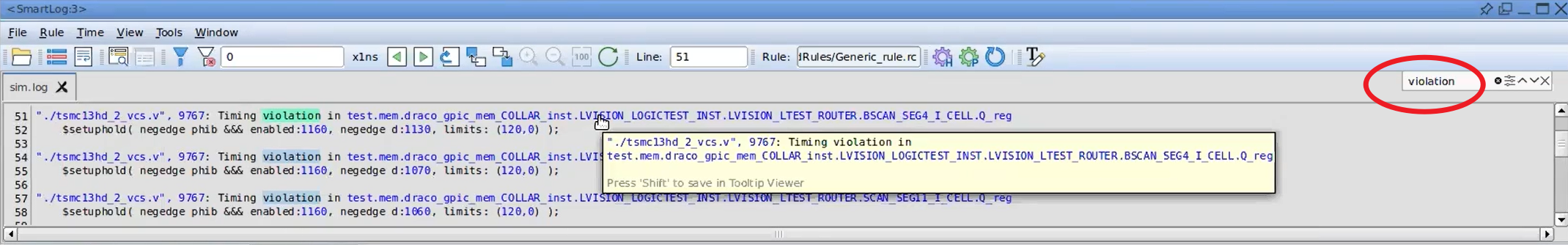

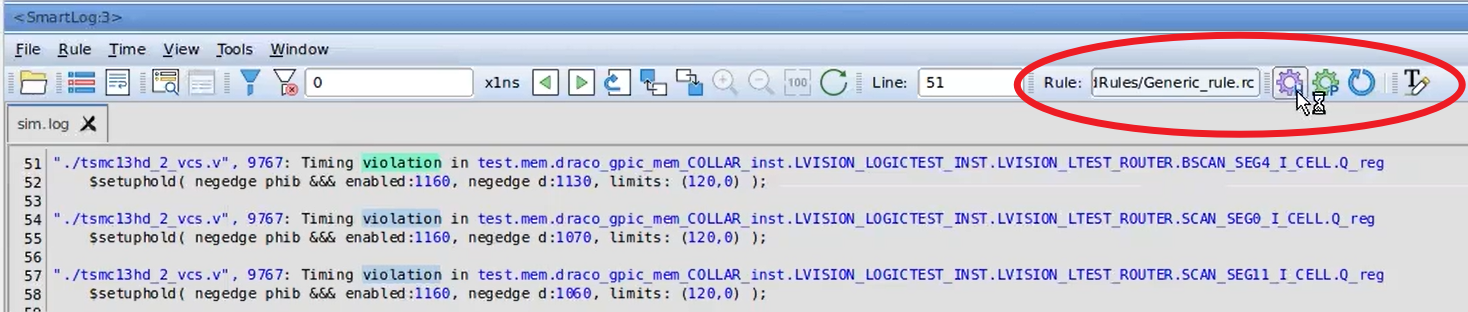

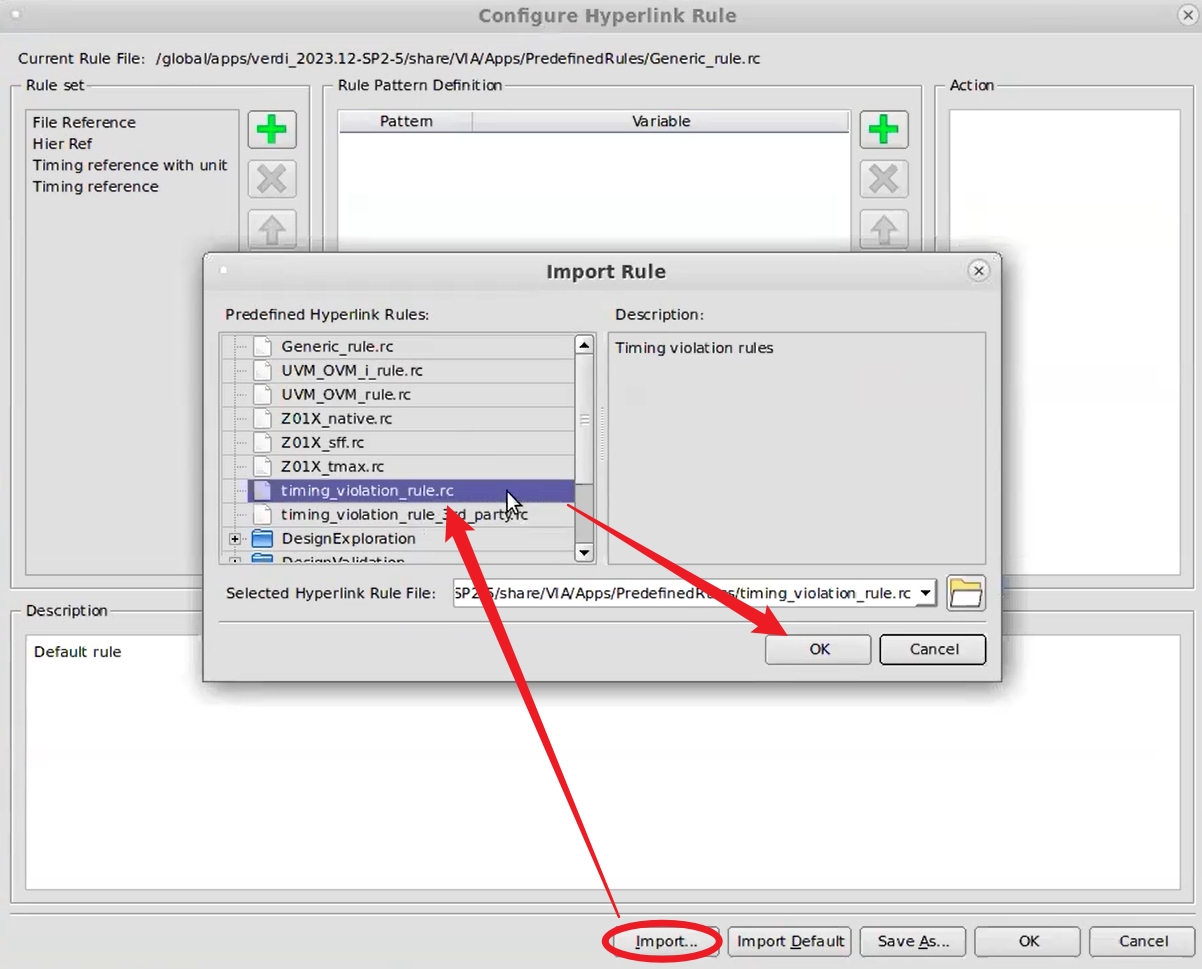

(3)smartLog查看所有vio

(1)点击 smartLog

(2)选择 sim.log

(3)选择 Hyperlink Rule File

(4)查找 vio

(5)点击rule设置

(6)点击 vio 信息就会自动加载波形到需要时间段

4.7 nSchema

(1)nSchema视图设置

nSchema 的原始视图直接改 view 只能单次生效,可以在 Preference 处设置,即可永久生效:

具体功能不啰嗦了,自己多点点点吧,有时候比代码好看些~

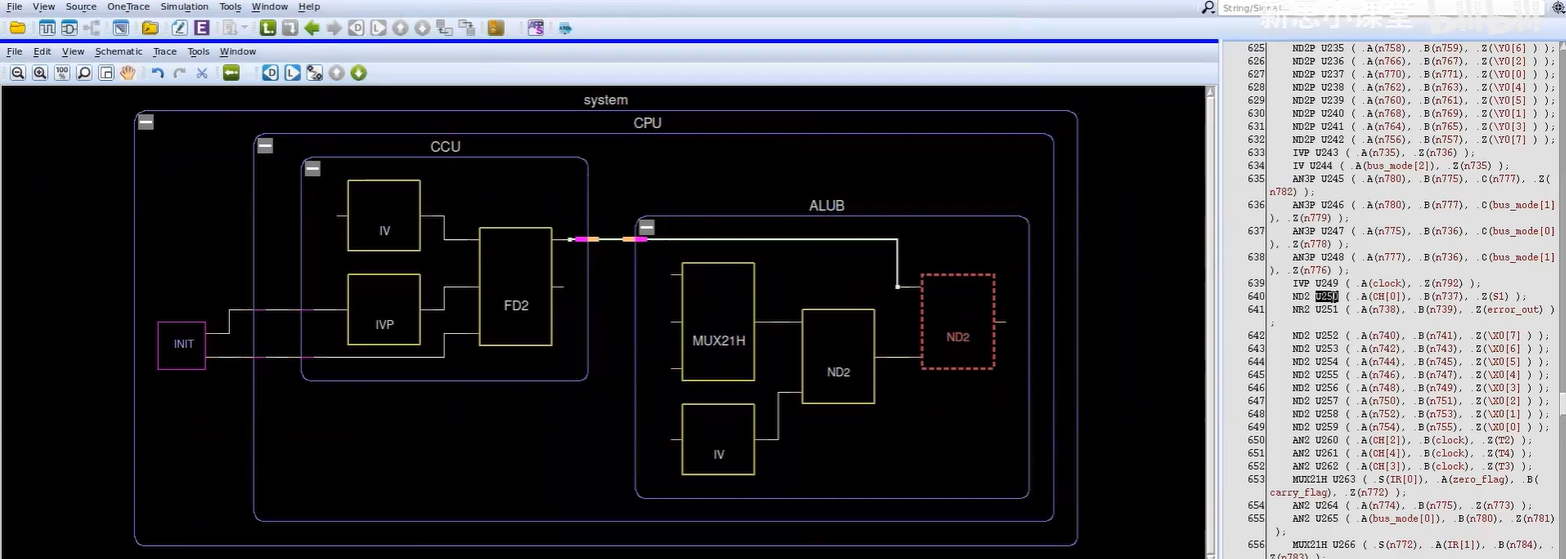

(2)电路图找逻辑

后仿比较难点代码,可以打开一个新的电路图:

右边代码的信号往左边拖,可以更方便的看来源:

4.8 点波形跳转到代码定义处

(1)普通方法

双击波形,或者用鼠标将信号拖拽到代码框里,可以跳转到该信号的”trace“处,而不是信号的”definition“处。这时需要继续操作:

- 点击鼠标右键选择”Signal >>> Show Signal Definition“,可以到达信号定义处;

- 或者,点击 Message 框,会呈现刚刚选中的信号的”definition“处和”trace“处,双击”definition“处可以到达代码定义点;

(2)修改配置

修改 Preference,就可以实现跳转到该信号的”definition“处了,如下所示:

这样设置后,双击波形还是到达信号的”trace“处,但是用鼠标将信号拖拽到代码框里,就能到达信号的”definition“处了。这样想到哪就到哪,非常方便。

(3)同步按钮

点亮两个方框的同步按钮,再点击波形信号,代码就会自动同步到定义处了。

参考资料:

[2] Bilibili 【新思小课堂】

[3] 芯片验证日记 Verdi用法小节

浙公网安备 33010602011771号

浙公网安备 33010602011771号