校招基础——数电和Verilog

1、逻辑函数的表示方法

常用的逻辑函数表示方法有逻辑真值表,逻辑函数式,逻辑图,波形图,卡诺图和硬件描述语言等。

2、什么是格雷码?

在一组数的编码中,若任意两个相邻的代码只有一位二进制数不同,则称这种编码为格雷码(Gray Code),另外由于最大数与最小数之间也仅一位数不同,即“首尾相连”,因此又称循环码或反射码。格雷码(Gray Code)又称Grey Code、葛莱码、格莱码、戈莱码、循环码、反射二进制码、最小差错码等。

3、为什么要使用格雷码?

格雷码是一种具有反射特性和循环特性的单步自补码,其循环和单步特性消除了随机取数时出现重大错误的可能,其反射和自补特性使得对其进行求反操作也非常方便。格雷码属于一种可靠性编码,它在相邻间转换时,只有一位产生变化,它大大减少了一个状态到另一个状态时逻辑的混淆,因此格雷码在通信和测量技术中得到广泛应用。

4、格雷码有哪些特点?

(1)格雷码具有反射特性;

(2)格雷码具有循环特性;

(3)格雷码是一种准权码;

(4)格雷码相邻的码组间仅有一位不同;

(5)格雷码从编码形式上杜绝了逻辑冒险的发生;

(6)卡诺图是按格雷码来画的;

(7)格雷码不是一种二进制;(易错)

5、格雷码和独热码的区别

独热编码占用较多的位,也就是消耗较多的触发器,但这些额外触发器占用的面积可与译码电路省下来的面积相抵消。

6、二进制转格雷码

Gray = (bin>>1) ^ bin;(右移一位后和自身异或)

7、下面那些是格雷码的特性?(ACD)

A、格雷码具有反射特性

B、格雷码是一种二进制

C、格雷码可以减少干扰

D、格雷码相连码组之间只有一个码元不同

8、A和B均为补码表示的二进制,其中A=10010010B,B=10001011B,请问下列选项中哪一个为A+B的运算结果:(A)

A.100011101

B.110011101

C.111100010

D.011100011

注意:已经是补码表示的了,复习一下有符号数加减法就行。

9、将二输入的与非门当非门使用时,另一端的接法是

与非门:(AB)’=A’+ B’,当非门使用,A正常,B接1即可,所以另一端接高电平。

10、B’+ABC+(AC)’+(AB)’,最简为(1),(A+B)(AB’)最简为(AB’)。

(1)原式=B’+ABC+A’+C’+A’+B’=A’+B’+C’+ABC=(ABC)’+ABC=1

此处用到摩根定理:(A+B+C)’=A’*B’*C’

(A*B*C)’=A’+B’+C’

或者画卡诺图,会发现全部都填满了1,因此答案也是1。

(2)分配律:(A+B)(AB’)=AAB’+AB’B = AB’

11、设计一电路,其输入端为A,B,C,输出端为Y,要求其功能为:

当A=1时,Y=B;

当A=0时,Y=C;

设计内容包括:

(1)列出真值表;(2)写出Y的最简与或表达式(3)用最少的与非门画出逻辑图。

解:(1)真值表

A B C Y

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 0

1 1 0 1

1 1 1 1

(2)Y的与或表达式

根据(1)真值表,将Y=1里含有1的加起来就行,Y = A’B’C + A’BC + ABC’+ ABC = AB+A’C=AB+A’C,忘了公式也可以画卡诺图,很快就得到答案了。

(3)Y=AB+A’C=((AB)’(A’C)’)’所以只需要4个与非门即可。

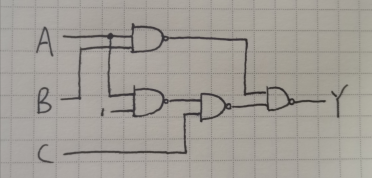

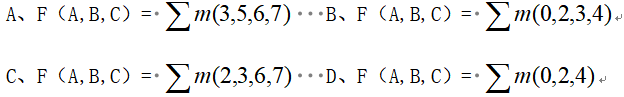

12、函数F(A,B,C)=AB+BC+AC的最小项表达式为(A)

13、下图中为组合逻辑Y=f(A,B,C,D)的真值表,请根据此真值表在下列答案中选择Y的逻辑表达式(D)

|

|

AB=00 |

AB=01 |

AB=11 |

AB=10 |

|

CD=00 |

0 |

0 |

0 |

0 |

|

CD=01 |

1 |

1 |

1 |

1 |

|

CD=11 |

0 |

0 |

1 |

1 |

|

CD=10 |

0 |

0 |

1 |

1 |

A、C’D+AD

B、AC+D

C、AC+A’D

D、AC+C’D

本题考查的是卡诺图,有1的是有效项。

14、约束项就是逻辑函数中不允许出现的变量取值组合,用卡诺图化解时,可将约束项当做1,也可当做0。(错误)

对输入变量取值的限制称为约束。当限制某些输入变量的取值不能出现时,用对应的最小项等于 0 表示,这些最小项就是约束项。(考察对书本概念的熟悉)

以下是Verilog部分

1、HDL语言的层次概念?

HDL语言是分层次的、类型的,最常用的层次概念有系统与标准级、功能模块级,行为级,寄存器传输级和门级。

系统级,算法级,RTL级(行为级),门级,开关级

2、FPGA的可综合和不可综合有哪些?

可综合:aupply0、supply1、buf、buff0、buff1、notif0、notif1、integer、for、function、instantitation、operators。

不可综合:defparam、$finish、initial、events、real、time、force、release、fork、join、delays、wait、#。

3、下面关于verilog描述正确的是:(ABCD)

A.如果A=1’b1,B=1’b0,F=A&~B|B&~A|B,则F=1’b1。

B.y=a+b;属于阻塞赋值语句,执行该语句时,先计算a+b值,然后更新y值,在此过程中不能运算其他语句。

C.generate,for,function语句可以综合(for循环可综合时,循环变量必须是固定值)。

D.如果A=4’hb,则^A=1’b1。

解析:~优先级最高,&第二高,|第三高

4、下列语句中不属于并行语句的是(A)

A、过程语句 B、assign语句 C、无条件例化语句 D、when...else语句

5、块语句有两种:begin-end语句是(顺序)执行语句;fork-join是(并行)执行语句。

6、时间尺度定义为timescale 10ns/100ps,选择正确答案(C)

A、时间精度10ns B、时间单位100ps

C、时间精度100ps D、时间精度不确定

7、verilog语言中,wire型数据如果定义后没有赋值,则默认值为(A)

A、x B、0 C、1 D、z

解析:wire初始值是x,它只是根线。Reg是可以赋初值的,不赋值为0.

8、Verilog的3种语言描述方式?

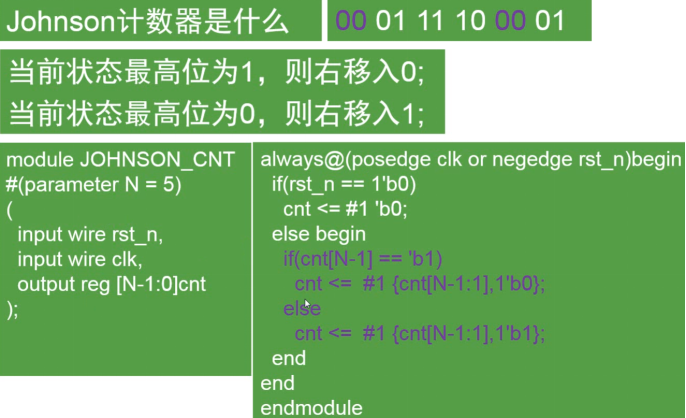

9、实现N位Johnson计数器,N=5.

10、以下哪些不属于function的特性?(B)

A、可以调用其他function;

B、消耗非0仿真时间;

C、必须至少有一个输入参数;

D、不得包含任何延迟和时序控制语句;

11、qword、dword、word、byte、bit的区别?

- 1qword = 2dword = 4word = 8byte = 64bit;

- 1dword = 2 word = 4byte = 32bit;

- 1word = 2byte = 16bit

- 1byte = 8bit

12、task和function的区别?

(1)task可以定义自己的仿真时间单位;

function只能与主模块共用仿真时间单位;

(2)task是过程性语句,要出现在always块或initial块中;

function不是过程性语句,不能出现在always块或initial块中;

(3)task可以有时间控制语句,如#,@,wait;

function不能有时间控制语句;

(4)task可以没有输入输出端口;

function至少要有一个输入参量;

(5)task不返回值;

function返回一个值;

(6)task可以调用function;

function不能调用task;

浙公网安备 33010602011771号

浙公网安备 33010602011771号