求职经验之综合岗位二面

NVIDIA的综合二面,感觉挺简单(额。。。)

1:问我是否感兴趣,双向选择

2:team综合主要做的方面

3:verilog知识

if..else与case的区别

if语句指定了一个有优先级的编码逻辑,而case语句生成的逻辑语句是并行的,不具有优先级。if语句可以包含一系列不同的表达式,而case语句比较的是一个公共的控制表达式。通常if-else结构速度较慢,但占用的面积小,如果对速度没有要求但对面积有较高要求,则可用if-else结构完成编解码。case结构速度较快,但占用面积较大,所以用case语句实现对速度要求较高的编解码电路。嵌套的if语句如果使用不当,就会导致设计的更大延时,为了避免较大的路径延迟,最好不要使用特别长的嵌套if结构。如想利用if语句来实现那些对延时要求苛刻的路径时,应将最高优先级给最迟到达的关键信号。

latch以及产生latch的原因

什么是敏感列表

阻塞与非阻塞

同步复位与异步复位

3:setup 与hold,不满足怎么做

4:综合知识

流程,可以以DC流程来说

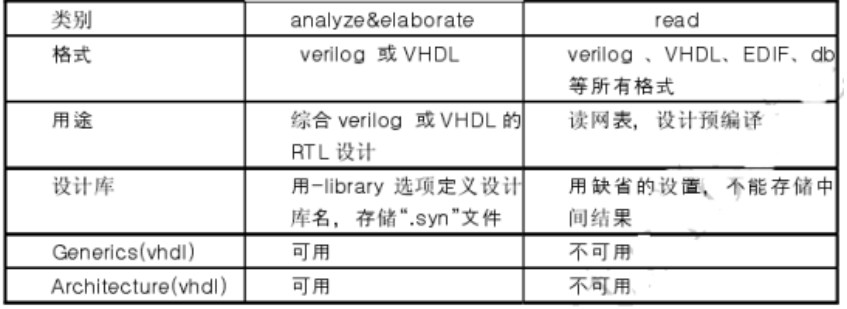

read 与 analyse..elaborate的区别(不知道)

从中可以看到,analyze & elaborate 可以自由指定设计库,并生成 GTECH中间文件前生成.syn 文件存储于 work 目录下,便于下次 elaborate 节省时间,我们一般选择 analyze & elaborate 的方法读入设计。

约束有哪些?具体

怎样进行timing优化(从design与DC优化上说明)

link library与target library的区别(不知道)

Link library 和 target library 统称为 technology library(即工艺库,习惯称之为综合库),technology library 由半导体制造商提供,包含相关 cell 的信息及设计约束标准,其中:

Target library: 在门级优化及映射的时候提供生成网表的 cell,即DC 用于创建实际电路的库。

Link library: 提供设计网表中的 cell,可以跟target_library使用同一个库,但是 DC 不用 link library中的 cell 来综合设计。

当 DC 读入设计时,它自动读入由 link library 变量指定的库。当连接设计时,DC 先搜寻其内存中已经有的库,然后在搜寻由 link library 指定的库。

注:当读入的文件是门级网表时,需要把 link library 指向生成该门级网表的库文件,否则 DC 因不知道网表中门单元电路的功能而报错。 关于工艺库里面的具体内容,后面会专门进行说明。

5:脚本知识

tcl的遍历,排序

6:跨时钟方式

7:抗压能力强的一个举例

8:问问题:

(A)螺丝丁问题

(B)

浙公网安备 33010602011771号

浙公网安备 33010602011771号