DDR学习(1)基础知识

一:存储器

1:存储器分类

2:RAM(random access memory 随机存取存储器)

随机存取,易失性,高访问速度,对静电敏感;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。

RAM与ROM最大的区别是,RAM在断电以后保存在上面的数据会自动消失,而ROM不会。

3:SRAM(静态RAM)

不要刷新,只要不掉电,数据可以一直保存,存取速度快,但结构复杂,价格昂贵,CPU的缓存用的就是SRAM

4:DRAM(动态RAM)

需要不断刷新,存取速度相对SRAM较慢

5:SDRAM(同步动态RAM)

同步指工作时需要同步时钟,内部的命令的发送与数据的传输都以它为标准

6:DDR SDRAM(双倍率同步动态RAM)

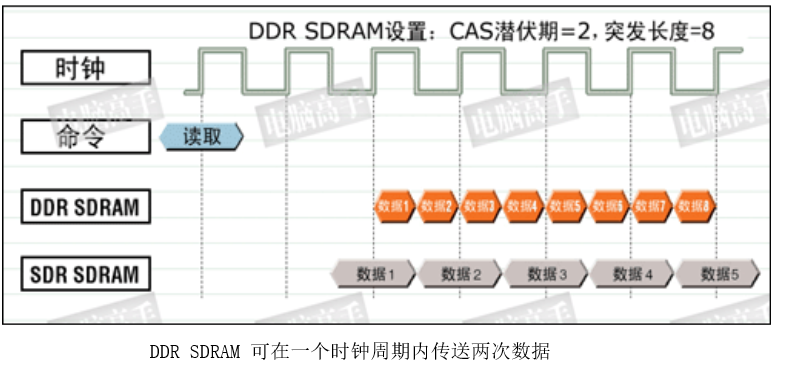

在SDRAM内存基础上发展而来,仍然沿用SDRAM生产体系;SDRAM在一个时钟周期的上升沿传输一次数据,DDR在时钟的上升期与下降期各传输一次数据。

二:SDRAM

1:物理Bank(P-Bank),意为通道

P-Bank就是内存总线的数据位宽,CPU数据总线的位宽

2:芯片位宽

一般芯片的位宽较小,为了组成P-Bank所需的位宽,需要多颗芯片并联工作。

P-Bank = 芯片位宽*芯片存储单元总个数*芯片数量

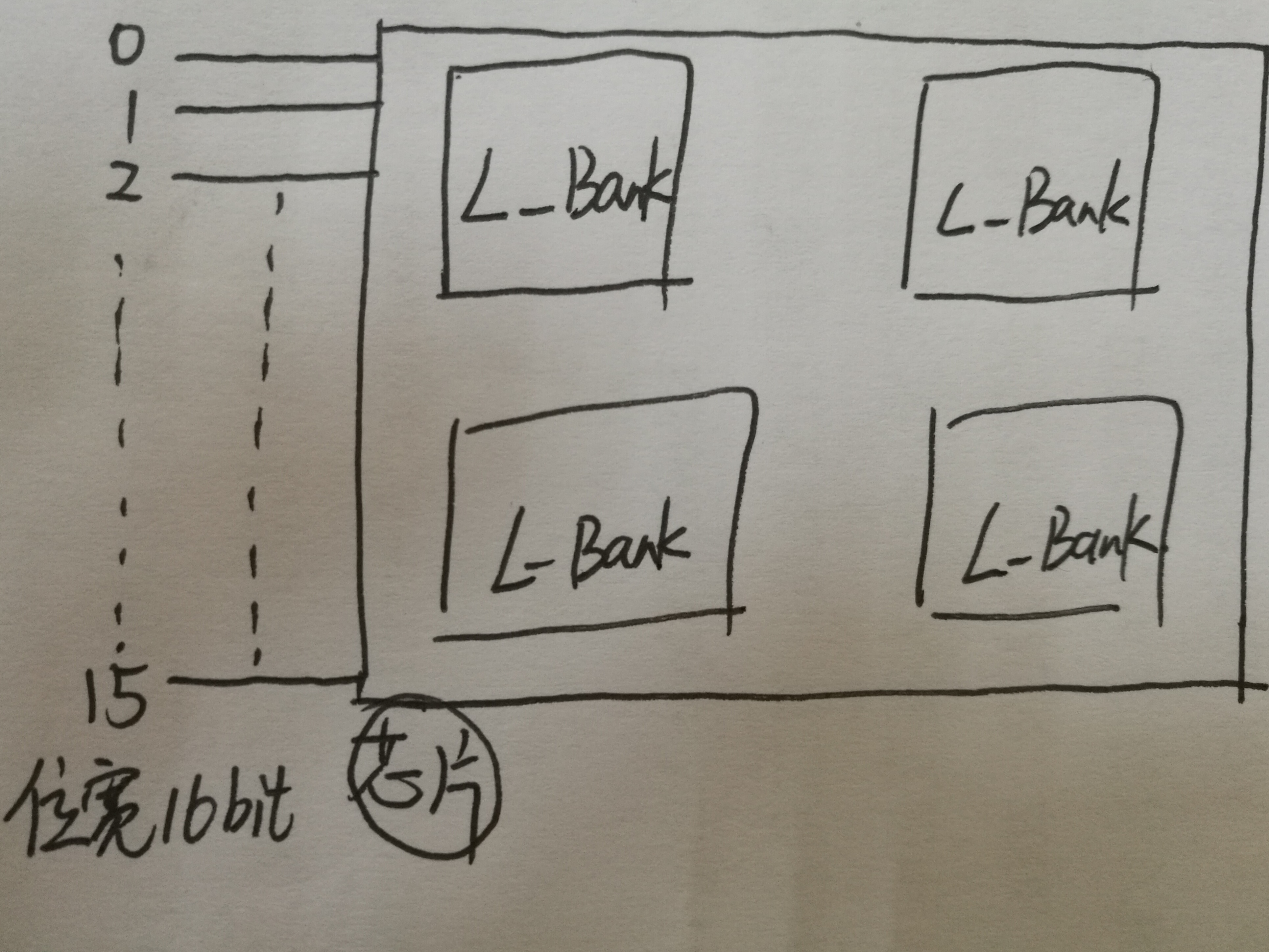

3:逻辑Bank(L-Bank):一个芯片上有多个L-Bank,目前一般是4个

行列表示

存储单元数量 = 行数 *列数 * L-Bank的数量

比如8M*8,这是一个8bit位宽的芯片,有8M个存储单元,总容量是64Mbit

4:128Mbit芯片的引脚

5:基本操作与时序

5.1:芯片初始化(MRS)

设定BL数值,读写操作模式(突发与否),突发传输模式(顺序传输,交错传输)

5.2:行选址(Row),使之处于活动状态

片选与L-Bank的定址同时进行,RAS(行地址选通脉冲)也处于有效状态。此时An地址线则发送具体的行地址

5.3:列选址与读写命令

列寻址地址线与行寻址地址线共用,但CAS可以区分行与列寻址的不同。

列选址时,CAS(列地址选通脉冲)与RAS命令之间必须有一个间隔,间隔为tRCD,可以理解为行选通周期,一般以时钟周期为单位,比如tRCD=2,代表延迟周期为两个时钟周期。

读写命令与列寻址信号同时发出,WE#无效时,为读取命令。

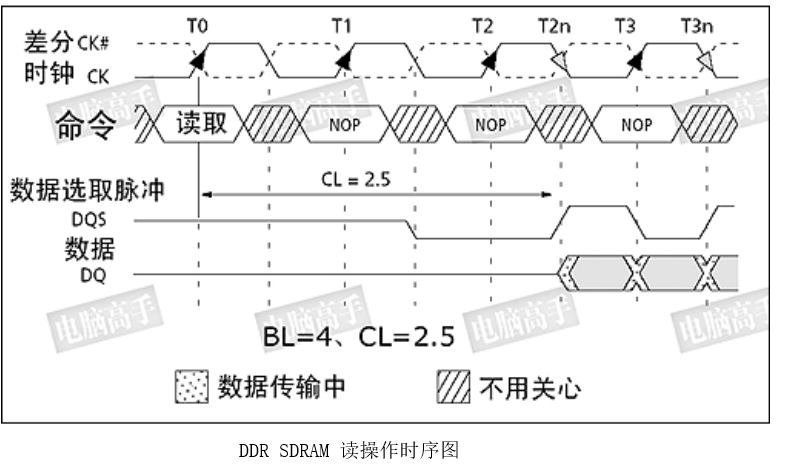

5.4:读操作

数据通过数据IO通道(DQ)输出到内存总线上;

CAS瞬间到达存储单元,但存储体中晶体管的反应时间会造成数据不可能与CAS在一个上升沿触发;从CAS与读取命令发出的第一笔数据输出的时间称为CL(CAS潜伏期),是时钟周期数。

数据在数据总线上,输出之前要经过S-AMP通道对数据进行放大,这段时间称为tAC;tAC的时间包括在CL时间内。如下图

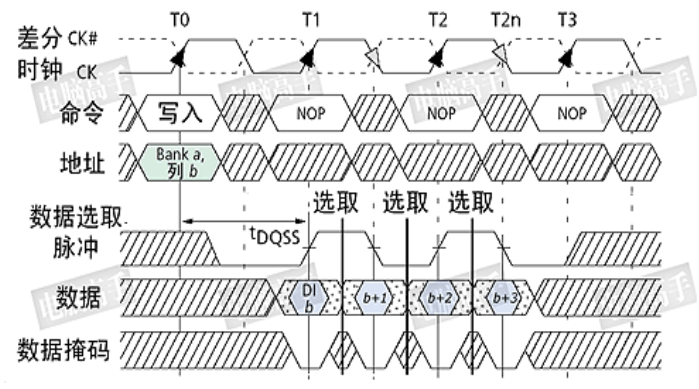

5.5:写操作

写入的操作也是在tRCD后,但此时没有CL;WE#此时为有效状态。

写操作的写入数据可以与CAS同时发送,也就是说写入延迟为0。但是选通三极管与电容充电必须有一段时间,所以真正的写入需要一定周期:tWR,这个操作也被称为写回。

5.6:突发长(burst):同一行相邻的存储单元连续进行

突发传输技术产生原因:当要连续读写时,对当前存储单元的下一个单元寻址,不断发送读写命令与列寻址命令(行地址不变),占用大量内存控制资源。所以burst技术应运而生。

burst技术只要指定起始列地址与突发长度,内存就会依次自动对后面相应数量的存储单元进行读写操作而不再需要控制器连续地提供列地址。

BL的数值,不能随便设置,在MRS阶段就要对BL设置,一般是定死的,常见设置为4和8。

5.7:预充电

对一行读写操作后,关闭现有工作行,准备打开新行的操作就是预充电。

在发出预充电命令后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行,这个间隔称为tRP(precharge period)

5.8:刷新

DRAM要不断进行刷新才能保留住数据。

预充电是对一个或所有L-Bank中的工作行操作,并且是不定期的,有固定周期(64ms);刷新过程中,所有L-Bank都停止工作,等待刷新结束后,才能进入正常的工作状态。

5.9:数据掩码

为了屏蔽不需要的数据,采用数据掩码(DQM)技术;

在读取时,被屏蔽的数据仍然会从存储体中传出,只是在“掩码逻辑单元”处被屏蔽。

三:DDR

1:基本原理

从中可以看出多了两个信号:CLK#与DQS,CLK#与正常CLK时钟相位相反,形成差分时钟信号。而数据的传输在CLK与CLK#的交叉点进行,可见CLK的上升沿与下降沿都有数据触发。

工作原理:在读取时,L-Bank在内部时钟信号的触发下一次传送8bit的数据给读取锁存器,再分成两路4bit数据传给复用器,由后者将它们合并为一路4bit数据流,

然后由发送器在DQS 的控制下在外部时钟上升与下降沿分两次传输4bit 的数据给主芯片。这样,如果时钟频率为100MHz,那么在I/O 端口处,由于是上下沿触发,那么就是传输频率就是200MHz。

2:差分时钟

由于数据是在CK 的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求CK 的上下沿间距要有精确的控制。但因为温度、电阻性能的改变等原因,CK上下沿间距可能发生变化,此时与其反相的 CK#就起到纠正的作用(CK 上升快下降慢,CK#则是上升慢下降快。

3:数据选取脉冲(DQS)

DQS 是DDR SDRAM 中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。每一颗芯片都有一个DQS 信号线,它是双向的,在写入时它用来传送由北桥发来的DQS 信号,读取时,则由芯片生成DQS 向北桥发送。完全可以说,它就是数据的同步信号。

4:写入延时

在发出写入命令后,DQS与写入数据要等一段时间才能送达,这个周期被称为DQS相对于写入命令的延迟时间(tDQSS)

5:突发长度与写入掩码

浙公网安备 33010602011771号

浙公网安备 33010602011771号