28nm工艺介绍与设计规则详解

微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

B站1:UID:3546863642871878

B站2:UID: 3546955410049087

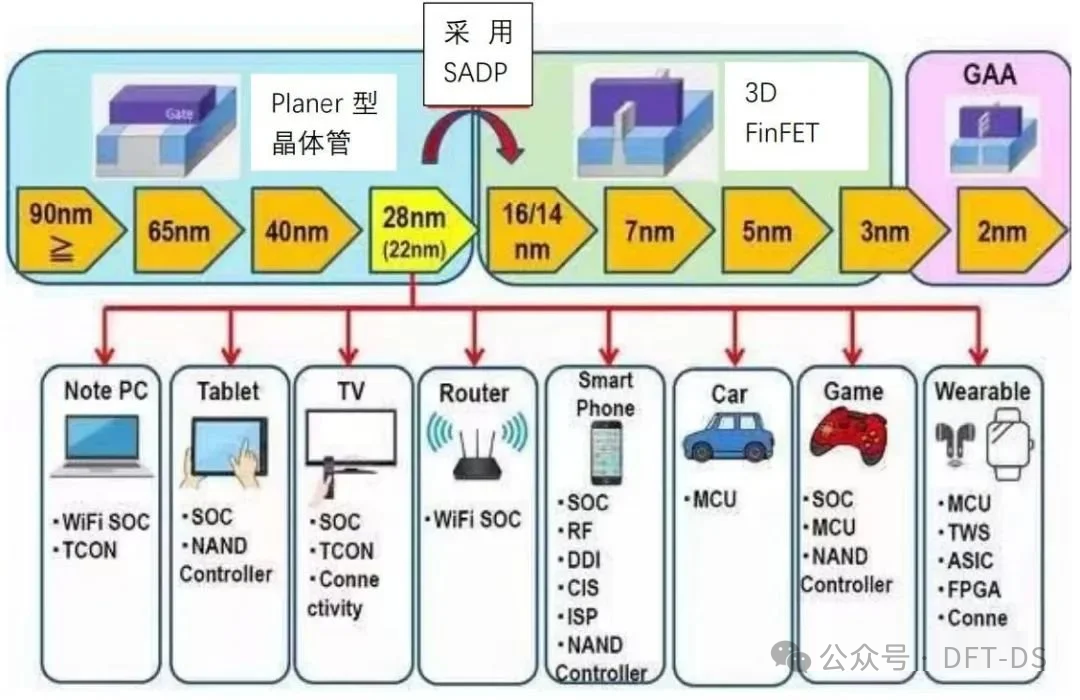

随着半导体技术进入深亚微米时代,28nm 工艺节点成为了一个关键的“平衡点”——它在性能、功耗、成本和良率之间取得了优异的平衡,广泛应用于移动处理器、FPGA、物联网芯片、网络芯片和汽车电子等领域。 不同于单一的工艺节点定义,28nm 实际上是一系列不同优化方向的工艺版本的集合,由不同晶圆厂(如台积电 TSMC、联电 UMC、格芯 GlobalFoundries)提供。每个版本针对特定应用场景进行了定制化优化。 本文将深入解析 28nm 工艺的主要版本划分、技术差异、设计规则演进及其对芯片设计的影响。

添加图片注释,不超过 140 字(可选)

一、28nm工艺版本划分(以台积电TSMC为例) 台积电(TSMC)是28nm工艺的领导者,其28nm家族包含多个子版本,主要分为以下四类:

1. 28LP(Low Power) 目标市场:物联网传感器、MCU、蓝牙芯片等超低功耗场景。

-

技术基础:Poly/SiON(多晶硅/氮氧化硅栅极); - 回归多晶硅栅极:采用氮氧化硅(SiON,k≈5)介质,等效氧化物厚度(EOT)增至1.8-2.0nm,漏电流比HKMG高2个数量级。 - 牺牲性能换功耗:晶体管驱动电流仅为HP版的50%,但静态功耗低至0.5nW/μm²(HP版为5nW/μm²)。 - 设计规则放宽: 栅极长度:31-38nm,光刻精度要求从HP版的3nm套刻误差放宽至5nm。 金属层数:从HP版的9层金属缩减至6层,顶层金属厚度仅1.8μm。 成本优势:单wafer成本比HP版低40%,适合量产的简单功能芯片,如Nordic nRF51822蓝牙芯片。

-

特点:

-

低阈值电压(Low Vt)器件丰富

-

漏电(Leakage)控制优秀

-

性能适中

-

优势:功耗最低,适合对电池寿命敏感的应用。

-

局限:性能上限较低,不适合高频设计。

适用场景:蓝牙芯片、传感器MCU、可穿戴设备。

2. 28HPM(High Performance for Mobile)

-

技术基础:High-k/Metal Gate(HKMG,高K金属栅极); - 混合栅极结构:PMOS保留金属栅极,NMOS采用低电阻多晶硅栅极,成本降低15%,但驱动电流损失约10%。 - 动态电压频率调节(DVFS):集成多组阈值电压晶体管,支持从0.8V到1.05V的宽电压调节范围。

-

工艺简化: - 光刻层数减少:通过合并部分通孔层,总光刻MASK层数从HP版的40层降至35层。 - 退火温度降低:快速热退火(RTA)峰值温度从1050℃降至1000℃,减少金属栅极的热预算压力。

-

特点:

-

高驱动电流(High Drive Current)

-

低栅极漏电

-

支持多阈值电压(Multi-Vt)优化

-

优势:在功耗和性能之间取得良好平衡,支持GHz以上主频。

-

典型客户:高通、联发科、博通等移动SoC厂商。

适用场景:智能手机应用处理器、4G/5G基带。

3. 28HPC(High Performance Computing)

-

技术基础

:HKMG + 优化工艺控制;28nm HPC工艺通过提升晶体管开关速度(较28LP版本提速约30%)和优化电路布局,显著提高运算能力,适用于服务器、工作站等高性能计算场景。该工艺采用高-k金属栅极(HKMG)技术,等效氧化膜厚度(EOT)从1.6nm降至0.9nm,实现更高能效比

-

核心改进:

-

更好的工艺角控制:显著降低“全局慢速”(SS)和“全局快速”(FF)工艺角的分布,提升芯片性能一致性。通过严格的工艺控制(如全局慢速与快速工艺角优化),28nm HPC可将系统级芯片(SoC)性能提升10-15%,同时减少20%漏电,动态功耗降低显著。HPC+版本在此基础上进一步优化,性能提升15%,漏电减少25%

-

更低漏电:相比HPM,漏电减少约20%。

-

更高的频率潜力:支持更高工作频率,适合高性能计算。

-

设计优势:

-

可使用更低驱动的逻辑单元满足时序要求

-

提高系统级芯片(SoC)整体性能10–15%

适用场景:FPGA(如Xilinx 7系列)、网络处理器、GPU。

4. 28HPC+(High Performance Computing Plus)

-

技术基础:HKMG + 掺杂优化 + 栅极工程;采用更严格的工艺控制,全局慢速(SSG)和快速(FFG)工艺角优化使系统级芯片(SoC)性能提升10-15%,同时动态功耗和电迁移要求得到更好控制。

-

关键提升:

-

性能提升15%:通过优化高K金属栅结构,提升载流子迁移率。通过高-K金属栅极(HKMG)技术改进掺杂特性,分离部分原子以优化晶体管性能。

-

漏电降低25%:改进掺杂特性,减少亚阈值漏电。其沟道长度设计比HPM工艺更长,漏电减少达50%,且无需高成本光刻闸极偏置。

-

工艺变异性进一步降低:提高良率和性能一致性。

-

结构改进:

-

从高K金属栅中分离部分原子,减少界面态

-

支持更长的沟道长度,减少短沟道效应

适用场景:高端AI推理芯片、5G基站SoC、高性能FPGA。

添加图片注释,不超过 140 字(可选)

二、28nm设计规则演进 随着工艺版本的演进,设计规则(Design Rules) 也不断优化,直接影响芯片的面积、性能和可布线性。 1. 灵活的工艺规则(Flexible Design Rules)

-

更广的栅极长度范围:支持从30nm到40nm的多种栅极长度(Gate Length),允许设计者在性能与漏电之间灵活权衡。

-

去除部分光刻步骤:减少制造复杂度,降低成本。

-

改善栅极间距(Gate Pitch):支持稍大的栅极间距,有利于改善性能或降低漏电。

2. 更小的单元高度(Cell Height)

-

传统单元高度:如9T(9-track)、12T

-

HPC/HPC+支持更矮单元:如7.5T、6T

-

优势:

-

减少芯片面积

-

提高布线资源利用率

-

折中:

-

较矮单元可能需要更大驱动强度的单元来满足时序,可能抵消部分面积优势

3. 布线规则改进

-

金属层间距优化:减少RC延迟

-

支持更多金属层堆叠:提高布线密度

-

低-k介质应用:降低金属间电容,提升信号速度

添加图片注释,不超过 140 字(可选)

三、逻辑库(Standard Cell Library)优化 不同28nm工艺版本配套不同的标准单元库,直接影响设计结果。

MBFF(Multi-Bit Flip-Flop):HPC+引入的新触发器类型,支持多重延迟、多重建立时间,帮助优化时序和功耗。 四、28nm工艺对比总结表

五、28nm工艺选择建议

联电(UMC)28HLP:性价比高,支持HPC/HPC+风格优化,适合中端市场。

添加图片注释,不超过 140 字(可选)

六、28nm工艺的生命周期与现状(2025年) 尽管先进工艺已进入3nm/2nm时代,28nm仍处于“黄金生命周期”:

-

需求旺盛:电源管理IC(PMIC)、显示驱动、MCU、汽车电子持续增长

-

产能充足:全球多条产线支持,供应稳定

-

成本优势:成熟工艺,良率高,NRE(非重复性工程成本)低

-

设计生态成熟:EDA工具、IP库、设计服务完善

预测:28nm工艺将在未来5–10年内继续扮演重要角色,尤其在模拟/混合信号、汽车和工业领域。 七、总结 28nm并非一个单一工艺,而是一个多版本、多优化方向的技术平台。理解其版本划分与设计规则,对芯片设计至关重要:

-

28LP:功耗优先,适合IoT

-

28HPM:移动平衡,适合手机SoC

-

28HPC/HPC+:性能优先,适合FPGA、AI、网络芯片

-

设计规则演进:支持更小面积、更高性能、更低漏电

-

逻辑库优化:MBFF、灵活栅长、多Vt等技术提升设计自由度

掌握28nm工艺的差异,有助于在项目初期做出正确的工艺选择,优化PPA(Performance, Power, Area),提升产品竞争力。 未来趋势:28nm将与FD-SOI、先进封装(如Chiplet)结合,延续其生命力,在成熟制程市场中持续发光发热。

添加图片注释,不超过 140 字(可选)

微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

B站1:UID:3546863642871878

B站2:UID: 3546955410049087

参考文献链接

人工智能芯片与自动驾驶

浙公网安备 33010602011771号

浙公网安备 33010602011771号