从硅晶圆到芯片:CMOS工艺的全流程

微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

"如果把一颗芯片放大到城市尺度,晶体管就是其中的楼宇,金属互连则是纵横交错的道路与桥梁。"

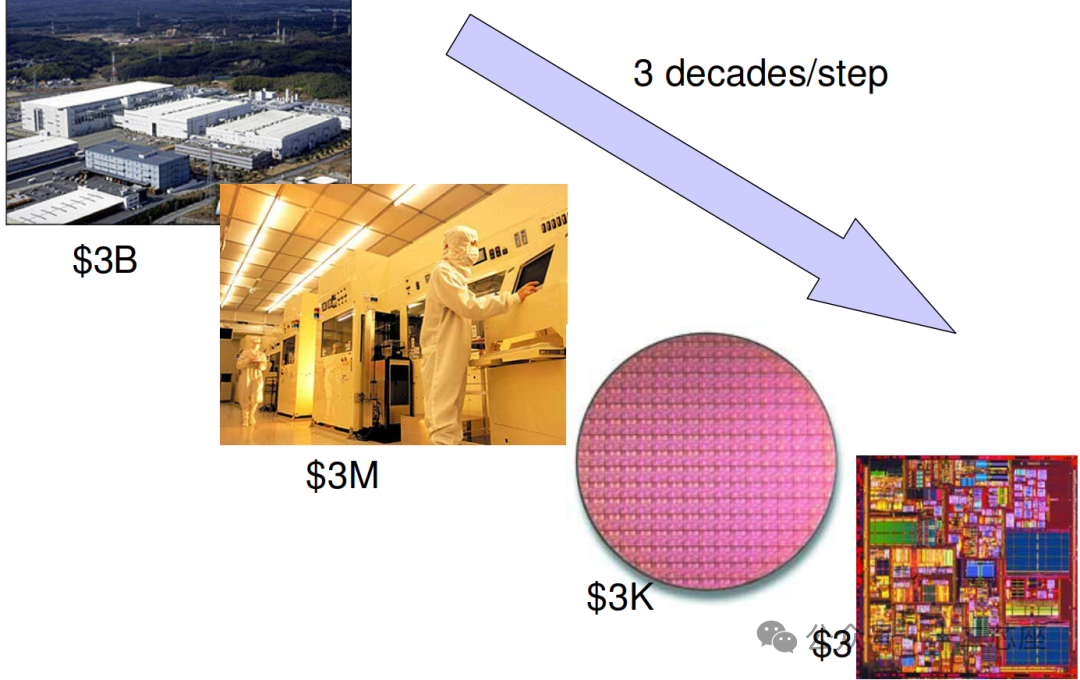

一、成本视角:为什么“晶圆厂”是烧钱巨兽

添加图片注释,不超过 140 字(可选)

$3B/$3M/$3K/$3:一座 12 寸先进工厂的资本支出约 30 亿美元;一条产线每天运营成本 300 万美元;一片(wafer)3 千美元;一颗裸片(die)仅 3 美元。 工艺越先进,晶体管越小,单位功能成本反而下降,但前期投入的门槛指数级上升。

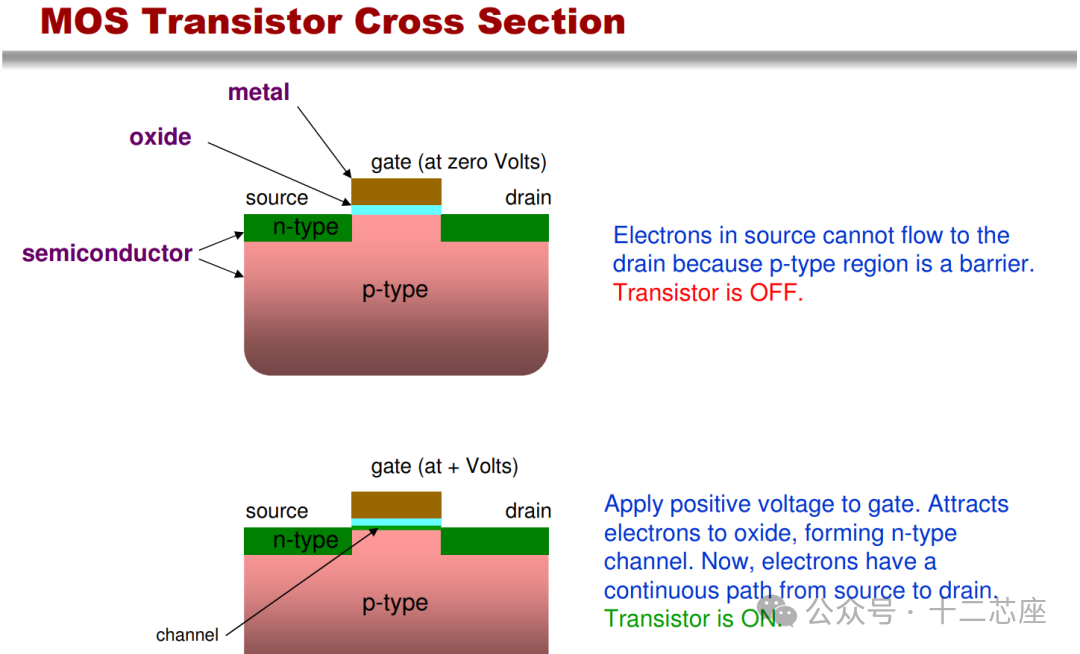

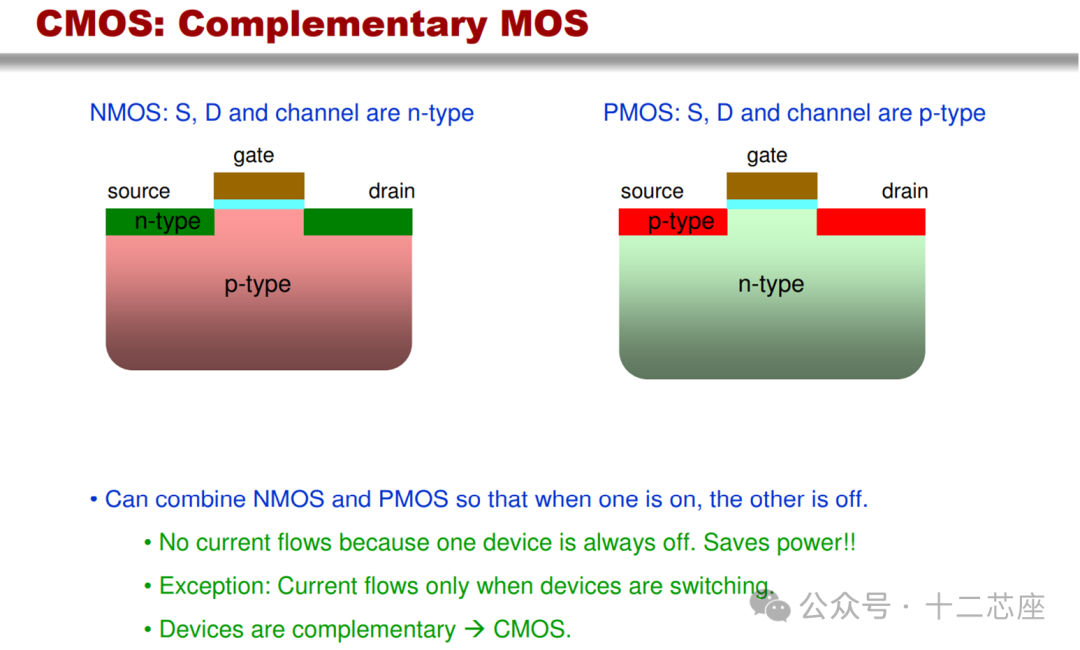

二、从“开关”概念到 CMOS NMOS 与 PMOS 的剖面图如下:

添加图片注释,不超过 140 字(可选)

添加图片注释,不超过 140 字(可选)

零栅压时,源极与漏极之间被 p/n 型势垒阻断,晶体管 OFF; 施加正栅压后,栅氧下方形成反型沟道,电子得以通行,晶体管 ON。

添加图片注释,不超过 140 字(可选)

三、七大工艺模块:循环往复 七大步骤:

光刻(Photolithography):旋涂光刻胶 → 掩膜曝光 → 显影 → 图形转移。

离子注入(Implant):高能量轰击,打出 n+/p+ 区。

扩散/退火(Diffusion/RTP):修复晶格损伤,激活杂质,控制结深。

薄膜沉积(CVD/PVD):氧化层、多晶硅、金属、阻挡层。

刻蚀(Etch):湿法各向同性 vs 干法 RIE 各向异性,图形精确雕刻。

化学机械抛光(CMP):把高低起伏磨成纳米级平整,才能继续下一层。

清洗 & 量测:每步前后都要确保无颗粒、无划痕,否则良率雪崩。

添加图片注释,不超过 140 字(可选)

Photolithography

四、前端制程(FEOL)

-

衬底选择:低阻 p 型硅

-

DNW(Deep N-Well):用高能离子注入构建深埋 N 阱,实现 NMOS 隔离。

-

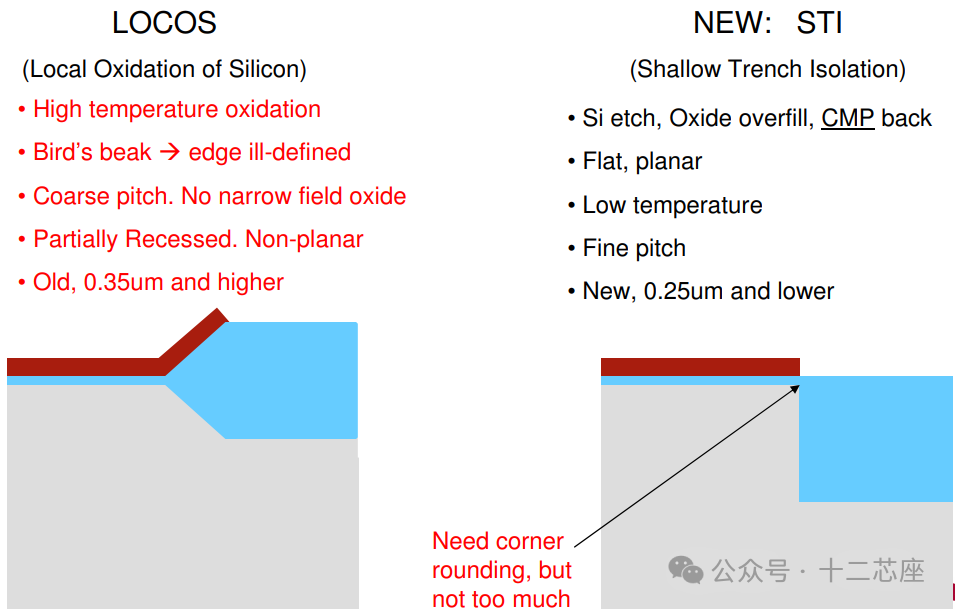

STI(Shallow Trench Isolation):取代老旧的 LOCOS,避免“鸟嘴”侵占。

添加图片注释,不超过 140 字(可选)

-

双阱 & 阈值调整:N-well、P-well、低/高压阈值注入,多掩膜、高能/低能搭配。

-

栅氧与多晶硅

-

LDD + halo/pocket注入:轻掺杂漏区 + 倾角口袋,抑制短沟道效应和热载流子。

-

侧墙 & 重掺杂:侧墙(spacer)做掩模,形成高浓度源漏,串联电阻骤降。

-

硅化物(Salicide):TiSi→CoSi→NiSi 演进,薄层电阻从 10 Ω/□ 降到 <1 Ω/□。

添加图片注释,不超过 140 字(可选)

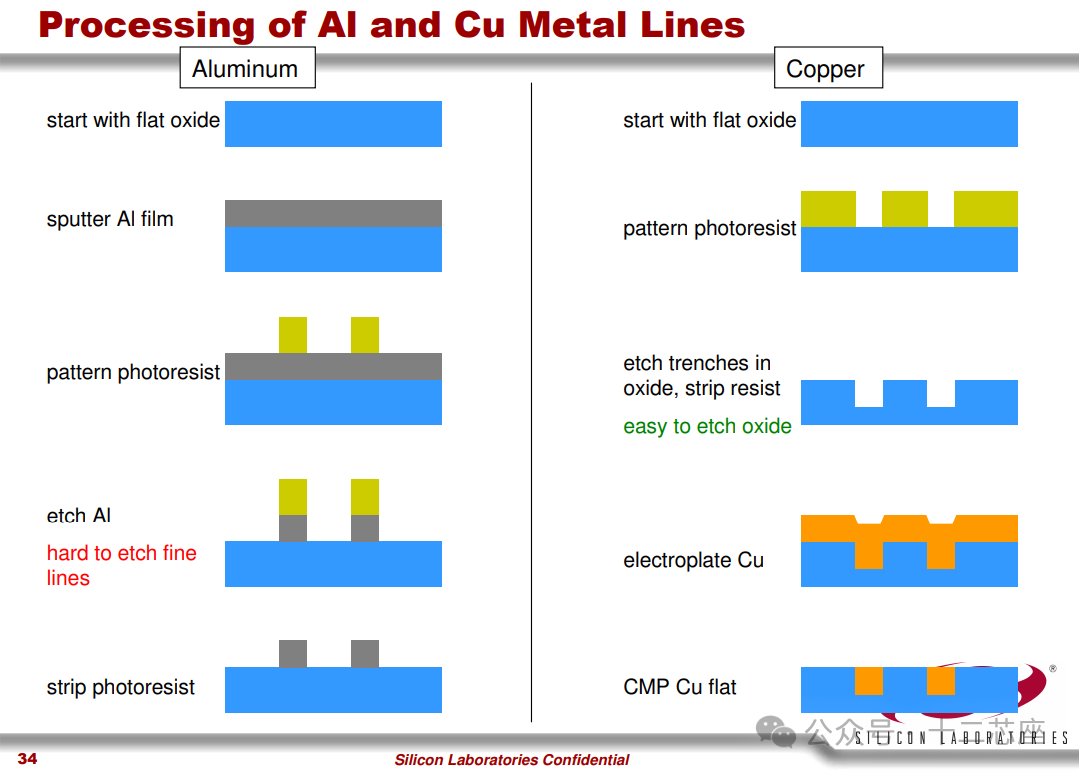

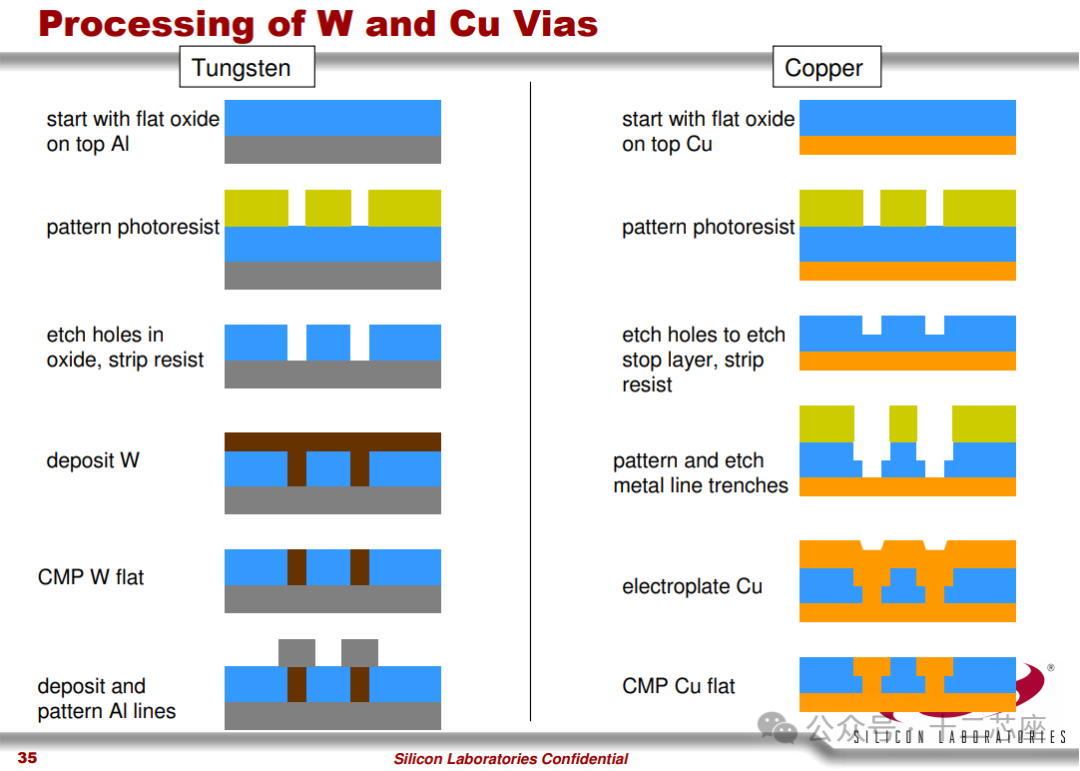

五、后端制程(BEOL):铜互连的时代

钨塞(W-plug)与铝线:0.18 µm 以上节点主流,铝电阻 2.7 µΩ·cm,但电迁移差。

铜 + 低 k:0.13 µm 之后全面转向大马士革铜(Damascene Cu): 先刻蚀氧化层沟槽 → 电镀 Cu → CMP 抛光 → 电阻降低,电流密度提升。

平面化挑战:CMP 容易在宽金属线上产生“dishing”与“erosion”,解决方法是加 dummy fill、限制线宽、slotting 等。

添加图片注释,不超过 140 字(可选)

添加图片注释,不超过 140 字(可选)

微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

B站:UID:3546863642871878

参考文献链接

人工智能芯片与自动驾驶

浙公网安备 33010602011771号

浙公网安备 33010602011771号