芯片“流片”详解:上亿晶体管的生死跃迁--从设计到量产的终极博弈

微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

芯片流片(Tape Out)是集成电路设计转化为物理芯片的核心环节,涉及设计验证、工艺制造与样品测试,直接决定芯片量产的成功率。

其名源于早期将设计图“流式输出”到磁带的传统,如今演变为将 GDSII版图数据交付晶圆厂的全过程。一次流片成本可超 1.5亿美元(3nm工艺),耗时 4-6个月,堪称半导体行业最昂贵的“试错实验”。

添加图片注释,不超过 140 字(可选)

一、流片是什么?

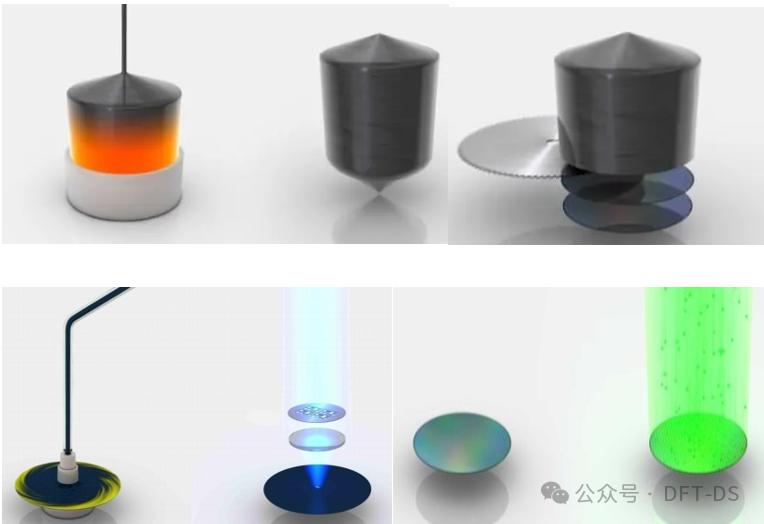

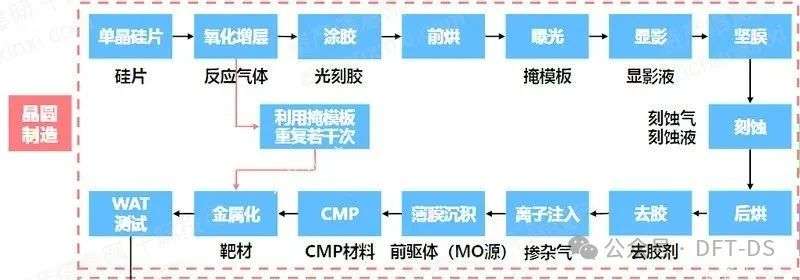

流片(tape-out)是指通过一系列工艺步骤在流水线上制造芯片,是集成电路设计的最后环节,也就是送交制造。这个过程包含光刻、刻蚀、离子注入、金属沉积等精密工艺,确保在硅片上精确构建设计的集成电路。

流片即为"试生产",简单来说就是设计完电路以后,先生产几片几十片,供测试用。如果测试通过,就照着这个样子开始大规模生产了及量产。

流片是把电路设计变成ASIC芯片的过程。即Fabless厂商设计完电路后,在所有检查和验证都正确无误的情况下,将最后的GDSII文件交由Foundry厂先生产一部分样品芯片(通常为数十片或上百片不等),以检验每一个工艺步骤是否可行,以及电路是否具备所需的性能和功能。

本质

流片是将设计的GDSII文件交付晶圆厂,通过光刻、蚀刻、离子注入等工艺制造样品芯片(通常数十至上百片),验证设计可行性与性能。

目标:检验电路功能、工艺兼容性,为量产铺路。

风险:失败可能导致数百万美元损失,初创企业可能因1-2次失败而破产。

价值

设计验证:暴露仿真未覆盖的物理缺陷(如时序偏差、功耗异常)。

量产前哨:通过样品测试优化良率,避免大规模投产风险。

技术闭环:工程师通过流片完成“设计-制造-测试”全流程能力闭环。

添加图片注释,不超过 140 字(可选)

二、 流片方式

Fabless设计者一般会将集成电路设计的最终结果以GDSII格式记录的电路版图数据交给Foundry,这个动作叫做Tape Out,俗称流片(投片)。Full Mask和MPW都是集成电路的一种流片(将设计结果交出去进行生产制造)方式。

添加图片注释,不超过 140 字(可选)

1. Full Mask

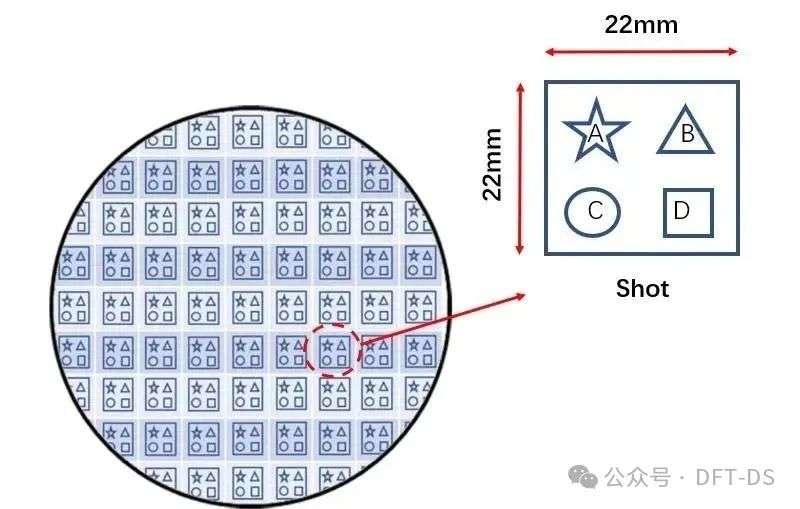

一种流片方式,“全掩膜”的意思,即在一次制造流程中整个掩膜只为某一个芯片设计服务。

2. MPW

一种流片方式,MPW全称为Multi Project Wafer,即多项目晶源,有别于Full Mask,即在一次制造流程中整个掩膜为多个芯片设计项目服务,也即同一次制造流程可以承担多个IC设计的制造任务。

优缺点

Full Mask就是指整个晶圆制造过程中的全部Mask都是为某个芯片所用,因此投片的成本很高。只有在设计完全有把握成功并且准备大批量生产、商用的时候,才会采用Full Mask方式,因为批量生产可以降低成本。

MPW成本仅为单独进行原型制造成本的5%-10%,极大地降低了产品开发风险。但是MPW有一定的流程,通常由Foundry或者第三方服务机构来进行组织,各种工艺在某一年之中的MPW时间点是预先设定好的,因此对参与者来说,在设计和开发方面有一定的进度压力。

MPW就是和别的厂家共享一张掩模版,而FULL MASK则是独享一张掩膜版。如果芯片风险比较高,则可以先做MPW,测试没有问题,再做FULL MASK。

添加图片注释,不超过 140 字(可选)

三、流程与关键技术

添加图片注释,不超过 140 字(可选)

1. 掩膜版制作(成本核心)

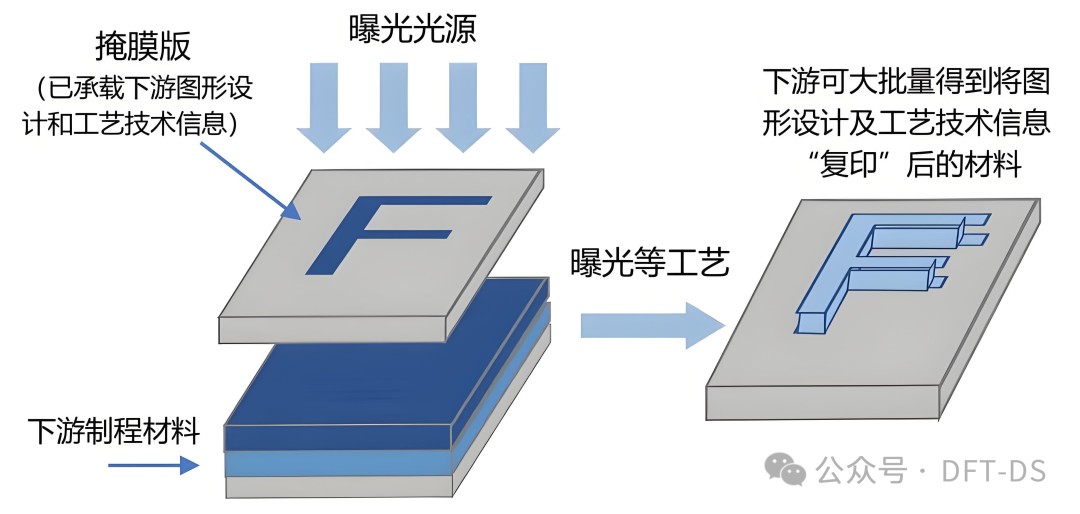

掩膜版又称光罩、光掩膜、光刻掩膜版等,是微电子制造过程中的图形转移工具或母版,是承载图形设计和工艺技术等知识产权信息的载体。

添加图片注释,不超过 140 字(可选)

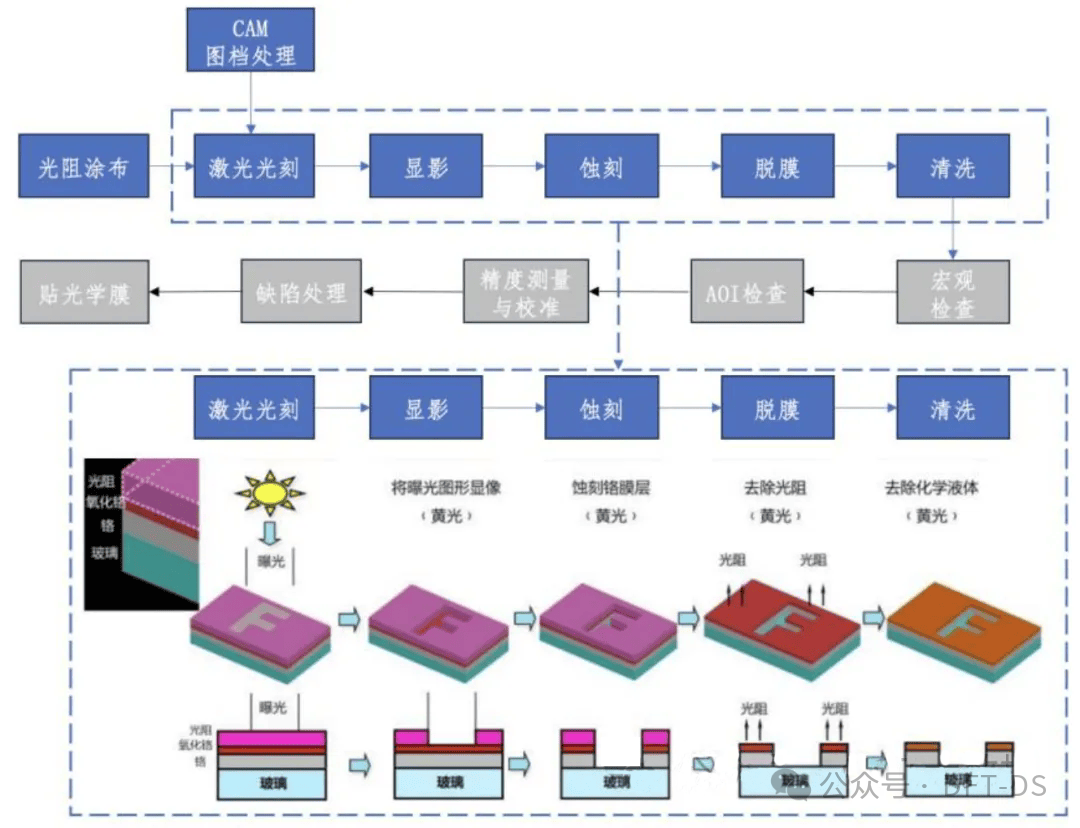

根据客户所需要的图形,掩膜版厂商通过光刻制版工艺,将微米级和纳米级的精细图案刻制于掩膜版基板上(掩膜版的原材料掩膜版基板是制作微细光掩膜图形的感光空白板),随后再将不需要的金属层和胶层洗去,即得到掩膜版产成品。掩膜版对下游行业生产线的作用主要体现为,利用掩膜版上已设计好的图案,通过透光与非透光的方式进行图像(电路图形)复制,从而实现批量生产。

作为光刻复制图形的基准和蓝本,掩膜版是连接工业设计和工艺制造的关键,掩膜版的精度和质量水平会直接影响最终下游制品的良率。

掩膜版的功能类似于传统照相机的“底片”:将设计者的电路图形通过曝光的方式转移到下游行业的基板或晶圆上,从而实现批量化生产。作为光刻复制图形的基准和蓝本,掩膜版是连接工业设计和工艺制造的关键,掩膜版的精度和质量水平会直接影响最终下游制品的优品率。掩模版是光刻工艺中的关键耗材,对于光刻工艺的重要性不弱于光刻机、光刻胶。

光刻工艺的“底片”,7nm工艺需80层以上掩膜,占流片成本60%-70%。

价格示例:40nm约500万元,14nm超2500万元。

添加图片注释,不超过 140 字(可选)

2. 晶圆制造关键工艺

光刻:

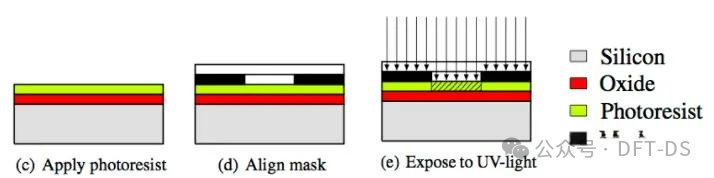

DUV/EUV技术将电路图形转印至硅片,精度达纳米级。硅片上抹上一层光刻胶,一般来讲光一照,光刻胶就溶解(正胶)。然后用做好的掩模mask来照射wafer。

添加图片注释,不超过 140 字(可选)

下面这个剖面图,黄色的就是我们加入的光刻胶。黑色是我们根据版图制作出来的模板。然后用UV光去照,把光刻胶镂空。

添加图片注释,不超过 140 字(可选)

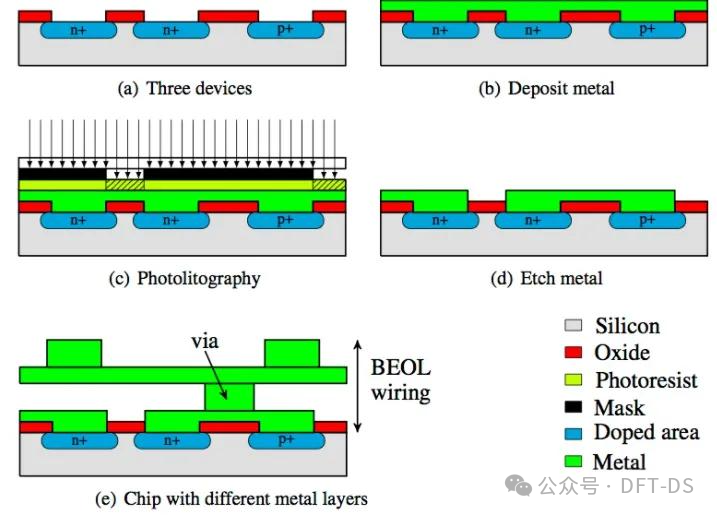

刻蚀与离子注入:

用药水把oxide刻蚀了,然后把光刻胶洗掉,最后注入离子。调整硅片导电性,形成晶体管。

金属化:

这一步主要是在硅片上连上金属线。这个过程我们看下面的剖面图比较清楚。沉积铜/铝连线,构建电路互联。

添加图片注释,不超过 140 字(可选)

看b图,首先在上面电镀一层金属,c图用光刻胶和掩膜版再刻蚀一遍得到d图,然后一层一层刻蚀叠加起来就行,层与层之间只有固定的通孔via用于连接。

3. 测试与封装

WAT (Wafer Acceptance Test), 这个主要是测试一下晶圆的电学特性是不是正常的。WAT测试电路代工厂在流片的时候就直接加入到晶圆里了,主要包括了各种晶体管参数比如阈值电压,漏电流,电阻,电容是不是正常的。一般WAT的测试向量是代工厂自己出,自己做测试。

CP(Chip Probing)测试。WAT测试没问题以后,接下来进行CP测试,先用探针看看芯片是不是好的,有问题的芯片直接扔掉,免得浪费封装成本。一般会用到以前文章讲的DFT三把斧,sacn chain, JTAG, BIST。CP测试向量由设计商提供。如果CP不合格,直接标记出来,扔掉。

CP测试(晶圆测试):筛除不良裸片,良率决定经济效益。

CP测试完了以后,就把芯片按照划片槽切成一个个小的芯片,装盒,寄出来进行封装/测试(Final Test)。

封装:陶瓷/塑料封装保护芯片,支持板级集成。

四、流片成本构成与优化策略

流片成本深度解剖(以5nm芯片为例)

添加图片注释,不超过 140 字(可选)

成本优化策略:

1)MPW(多项目晶圆)共享;

2) 晶圆尺寸博弈,12英寸 vs 8英寸晶圆;

3)开源IP替代, IP复用策略;

4) 提高流片良率水平,使用成熟工艺等。

五、流片费用为什么这么贵?

一次流片的价格主要由掩膜版和晶圆价格构成,其中掩膜版占比很大。

掩膜版(Photomask),又称光罩,是微电子制造中光刻工艺所使用的图形母版,从掩膜母版的图形转换到晶圆上的过程,就像印钞机工作一样。我们可以把光刻机想象成印钞机,把钞票母版的图形印到纸张上的过程,如同光刻机把芯片图形印到晶圆上,都需要有母版,这个母版就是所谓的掩膜版。

制造一款芯片需要几百甚至上千道工序,掩膜版也不只是一层,例如14nm工艺制程大约需要60层,7nm大约需要80层甚至更多。掩膜版的价格主要取决于芯片所选用的“工艺节点”,工艺节点越高,流片价格越贵。一般来说,越先进的工艺节点,所需要使用的掩膜版层数就越多。例如使用7nm EUV工艺的麒麟985流片费用至少在3000万美元左右,若采用16nm或28nm等比较成熟的工艺技术,流片费用就会大大降低。

一般来说,40nm的掩膜版大约在500万左右,而28nm的掩膜版大约在1000万左右,14nm的掩膜版大约在2500万左右。(不同厂家价格会有差异,这里只是说明MASK的成本比较高)

另外,掩膜版的总体费用,包括石英,光刻胶等原材料的成本,Mask Writer和Inspection等机台的使用成本,还有掩膜版相关数据的生成,包括OPC、MDP等软件授权、服务器使用、和人工开发成本等等。对于一款芯片,动辄几十层的掩膜版,需要如此多的步骤,设备、软件、人员缺一不可,费用昂贵也就不足为奇了。

六、流片经验的重要性?

参与流片是芯片工程师的必经之路,是入行的芯片工程师的成人礼。

对于芯片工程师来说,包含流片环节的才算是一个完整的芯片项目,参与流片也能帮你在IC开发流程的学习更完善。

比如做基带芯片,在什么场景下做低功耗、低功耗有哪些策略,从设计到实现再到应用层面,这些都需要流片环节做支撑/辅助。因为你不能只关心原理,你还需要清楚什么是流片中的不确定因素,并且要采用有效措施规避。这样一来你每做完一个芯片项目,你都有机会进一步为自己制定标准、优化自己的工作流程、提升工作效率的同时还能保证交付质量。

尤其是商用芯片,流片就相当于一次考试,考工程师,也考公司。每一次流片都是真金白银,流片失败次数不需要多,一两次就能把公司干垮。

对于有研发底蕴和资金支持的公司来说,流片也是很重要的。国内那些TOP级别的Design House,要的就是高质量交付,追求First time right,也就是尽可能一次性把芯片做成功。

还有一种情况,超大芯片,几百个工程师,每人只参与其中一小部分。这种对于参与感没有那么直接的同学,感受也会等比例下降。

但,无论如何,只有流片才能把你的想法,汗水变成这个世界实际的一个部分,参与到这个世界的实际运转中,无论如何也是值得你骄傲的第一步。

流片过程通常需要2-6个月(包括原料准备、光刻、掺杂、电镀、封装测试),这是芯片制造中最重要最耗钱的环节。不过流片的具体情况还要看芯片流片厂家产能情况而定。

流片流程之后会过渡到量产阶段,进行芯片量产级别测试,同时也会开发芯片内的软件,最终进行量产。

七、 流片的挑战与解决方案

设计与成本挑战

在芯片的设计与流片过程中,设计与成本的挑战日益凸显,成为制约行业发展的重要因素。

设计复杂性:随着摩尔定律的延续,芯片上的晶体管数量不断增加,导致电路规模的扩大。这不仅增加了版图验证和布线优化的工作量和技术难度,还要求性能的提升和功耗控制的更高标准。互连线的长度和密度的上升,也使得设计和验证变得更加复杂。

工艺技术进步:高精度要求推动了从深亚微米到纳米级工艺的技术跨越。这对设备精度和材料性能提出了更高要求,导致设备成本上升和材料研发、采购的难度增加。同时,高精度工艺需要更为严格的质量控制,以确保每一个生产环节的稳定性和可靠性,进一步增加了流片的整体成本。

应对策略:

设计环节:通过引入更高效的设计工具和方法,如高级综合、自动布线等,提高设计效率并降低人为错误。采用层次化设计、模块化设计等思想,将复杂系统分解为更易于管理的子模块,从而降低设计的复杂性。

成本控制:优化工艺参数和材料选择是关键。深入研究工艺原理和材料性能,找到性价比更高的工艺方案和材料组合。提高设备利用率、降低废品率等方式也是降低成本的有效途径。加强与供应链合作伙伴的沟通与协作,确保材料供应的稳定性和价格合理性。

设计与成本的挑战是芯片流片过程中不可回避的问题。通过不断创新和优化设计与流片流程中的各个环节,可以有效应对这些挑战并推动半导体行业的持续发展。

流片失败的应对措施:

在半导体制造领域,流片失败可能带来严重的后果,包括资金损失、时间延误,甚至可能影响整个项目的成败。因此,采取有效的应对措施至关重要。

加强设计验证和测试:在设计阶段进行详尽和严谨的仿真测试,以及在实际流片前进行严格的版图验证和时序分析,可以尽可能在设计阶段发现并修正潜在问题,从而显著提高流片的成功率。

与流片厂商的紧密沟通:流片过程中可能遇到各种工艺和设备问题,建立与流片厂商的定期沟通机制,及时反馈和解决问题,对于确保流片的顺利进行至关重要。

建立完善的失败分析和改进机制:即使做了充分的预防和准备工作,流片失败的可能性仍然存在。通过对失败原因的深入剖析,可以找出问题的根源,并据此优化设计和流片流程,从而避免类似问题的再次发生。

降低流片失败的风险需要从多个方面入手,包括加强设计验证和测试、与流片厂商的紧密沟通,以及建立完善的失败分析和改进机制。这些措施的实施,不仅可以提高流片的成功率,还可以为半导体制造行业的持续发展和技术创新提供有力保障。

添加图片注释,不超过 140 字(可选)

微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

参考文献链接

人工智能芯片与自动驾驶

浙公网安备 33010602011771号

浙公网安备 33010602011771号