数字IC Debug记录

综合后的网表功能与RTL不对

1、VCS仿真选项+nospecify和+notimingcheck没打开,注意后仿(带sdf)时应该将+nospecify去掉

2、有的模块没接上复位信号,用VCS仿真时rstn为高阻,功能可能正确;但是综合工具可能会把这些DFF的复位端口统统接0,这样输出就永远为0,进而就会被工具优化掉

3、如果想要工具不优化上述constant型的寄存器,可以将compile_seqmap_propagate_constants变量设置为false

4、RTL功能正确,综合后网表仿真存在大量不定态,原因有可能是控制通路存在X态、输入输出信号声明错误(即input声明为output,output声明为input,RTL仿真可能没问题),控制通路存在X态考虑如下实际例子:

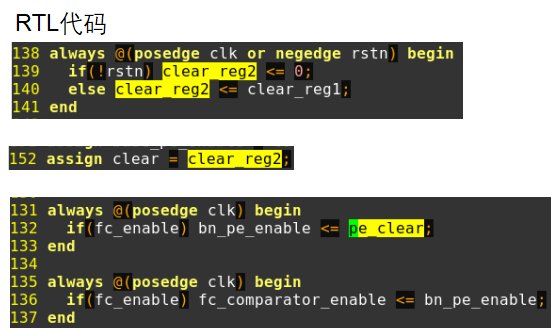

RTL代码如下,其中clear2(pe_clear)信号带有复位逻辑,而bn_pe_enable和fc_comparator_enable不带复位:

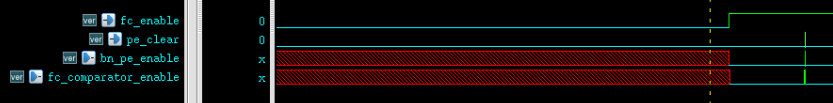

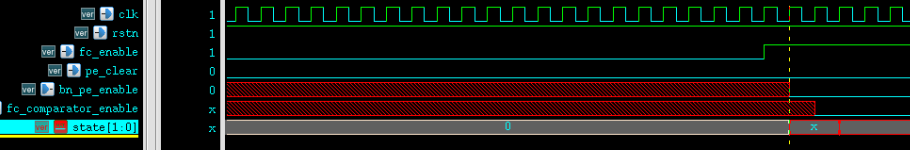

RTL仿真波形如下图所示,可以看到,pe_clear被复位至0,在fc_enable信号拉高以后,bn_pe_enable和fc_comparator_enable三个信号都立即变为低电平(这其实与实际电路不符,不定态没有传播,所以不定态在RTL阶段传播很重要!!!)

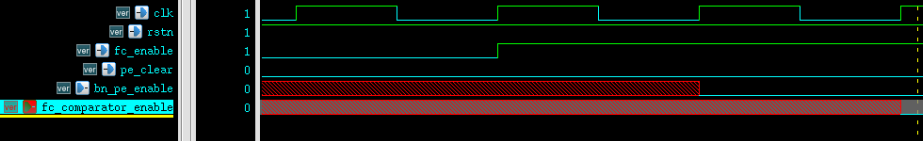

综合以后的网表仿真如下图所示,可以看到,在fc_enable拉高后1个周期bn_pe_enable才从X态变为低电平,而fc_comparator_enable在fc_enable拉高2个周期后才从X态变为低电平

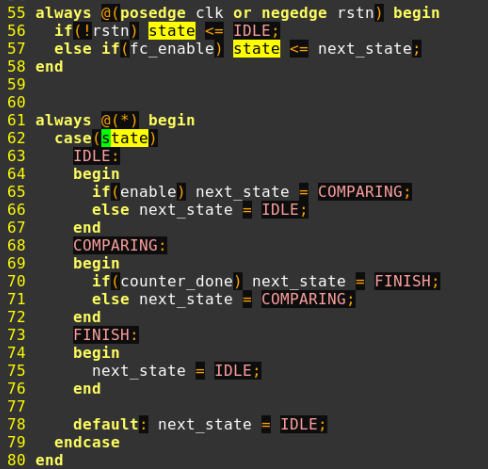

上述控制信号被用于fc_comparator中的如下状态机:

网表仿真如下图所示,可以看到,在fc_enable拉高后state开始更新状态,由于输入的fc_comparator_enable为X态,state更新为了一个X态,导致电路出错。

关于+neg_thck

http://ee.mweda.com/ask/340138.html

https://wenku.baidu.com/view/48912cf558fb770bf68a55b4.html

1.PR后的timing rpt没有时序违反,那sdf里负的hold 是什么意思,是好是坏?

没有关系,hold为负值的意思是信号在时钟沿之前指定时间内(那个负值的绝对值)翻转都不会出问题。

2 有error,提示要加+neg_thck,这个和负的hold有什么关系吗?加+neg_tchk貌似把负的hold修成0了?

需要+neg_thck,我认为不是因为“+neg_tchk”才把负值改为0,而是因为工具不支持负值,

所以把负值改为0来计算,这样相当于仿真时hold check更苛刻了。

3.+notimingcheck就相当于不检查负的hold?那影响仿真所加时序吗?这个命令在仿真时候需要加吗?

时序仿真不能用“+notimingcheck”,只有功能仿真时才可以加这个选项。

Round问题

https://blog.csdn.net/thl789/article/details/109018926

tensorflow的tf.round()函数其实不是“四舍五入”,而是“四舍六入五取偶”,即:

1、整数为偶数则舍去小数;

2、整数为奇数则进位到整数

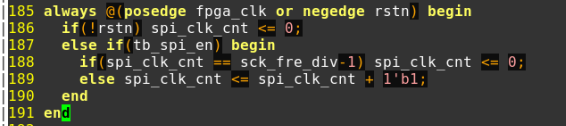

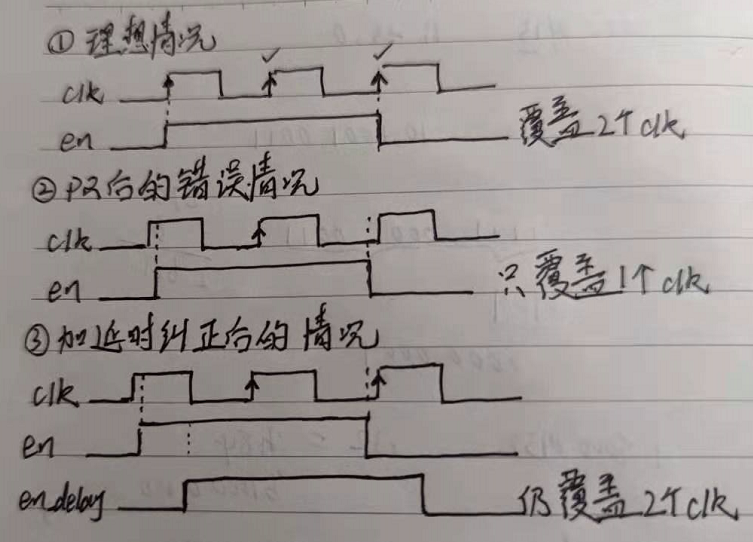

PR后的网表反标SDF功能不对

可能的原因是SPI发数据错误,在以下代码中,spi_clk_cnt根据tb_spi_en信号来进行计数,PR后,由于clk有jitter或信号延时的原因,tb_spi_en这个使能信号可能并不能覆盖到预期数目的时钟周期,导致出错。解决办法:可以给tb_spi_en添加一定的延时。

浙公网安备 33010602011771号

浙公网安备 33010602011771号