随笔分类 - _数字设计与计算机体系结构

摘要:#arm-elf-gcc汇编代码个人理解有关arm-elf-gcc的安装使用问题请参照本人博客的另一篇文章[http://www.cnblogs.com/wsine/p/4664503.html](http://www.cnblogs.com/wsine/p/4664503.html)由于各种对齐问...

阅读全文

posted @ 2015-07-21 15:12

Wsine

摘要:#arm-elf-gcc交叉编译器的使用教程一开始需要安装arm-elf-gcc,但是这是一个32位的程序,我是安装了64位的系统,据说安装ia32.libs依赖库能运行这个,但是看到博客上面前人安装完了系统图标少了一半,然后就怕了。经过了翻看ubuntu论坛和各种博客,才知道14版之后的ubunt...

阅读全文

posted @ 2015-07-21 14:55

Wsine

摘要:#QtSpim实现MIPS指令的编写由于各种对齐问题,cnblogs的格式难以控制,故贴图片,谅解。所增加的Hazard处理,相...

阅读全文

posted @ 2015-07-20 13:15

Wsine

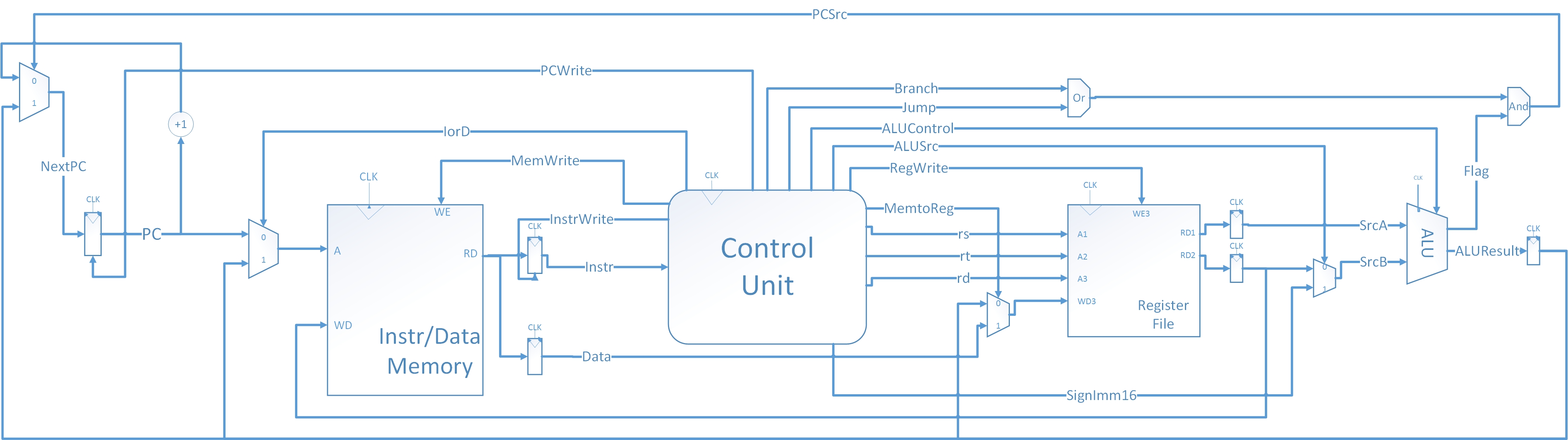

摘要:#16位CPU多周期设计这个工程完成了16位CPU的多周期设计,模块化设计,有包含必要的分析说明。###多周期CPU结构图###多周...

阅读全文

posted @ 2015-07-18 00:54

Wsine

摘要:#verilog实现的16位CPU单周期设计这个工程完成了16位CPU的单周期设计,模块化设计,包含对于关键指令的仿真与设计,有包含必要的分析说明。###单周期CPU结构图##实验状态图 浙公网安备 33010602011771号

浙公网安备 33010602011771号