STM32—TIM定时器第一部分

【TIM定时器】

第一部分:定时器的基本定时功能

第二部分:定时器的输出比较功能

第三部分:定时器的输入捕获功能

第四部分:定时器的编码器接

【定时器简介】

- 定时器TIM(Timer)

- 定时触发中断功能:可以对输入的时钟进行计数,并在计数值达到设定值时触发中断

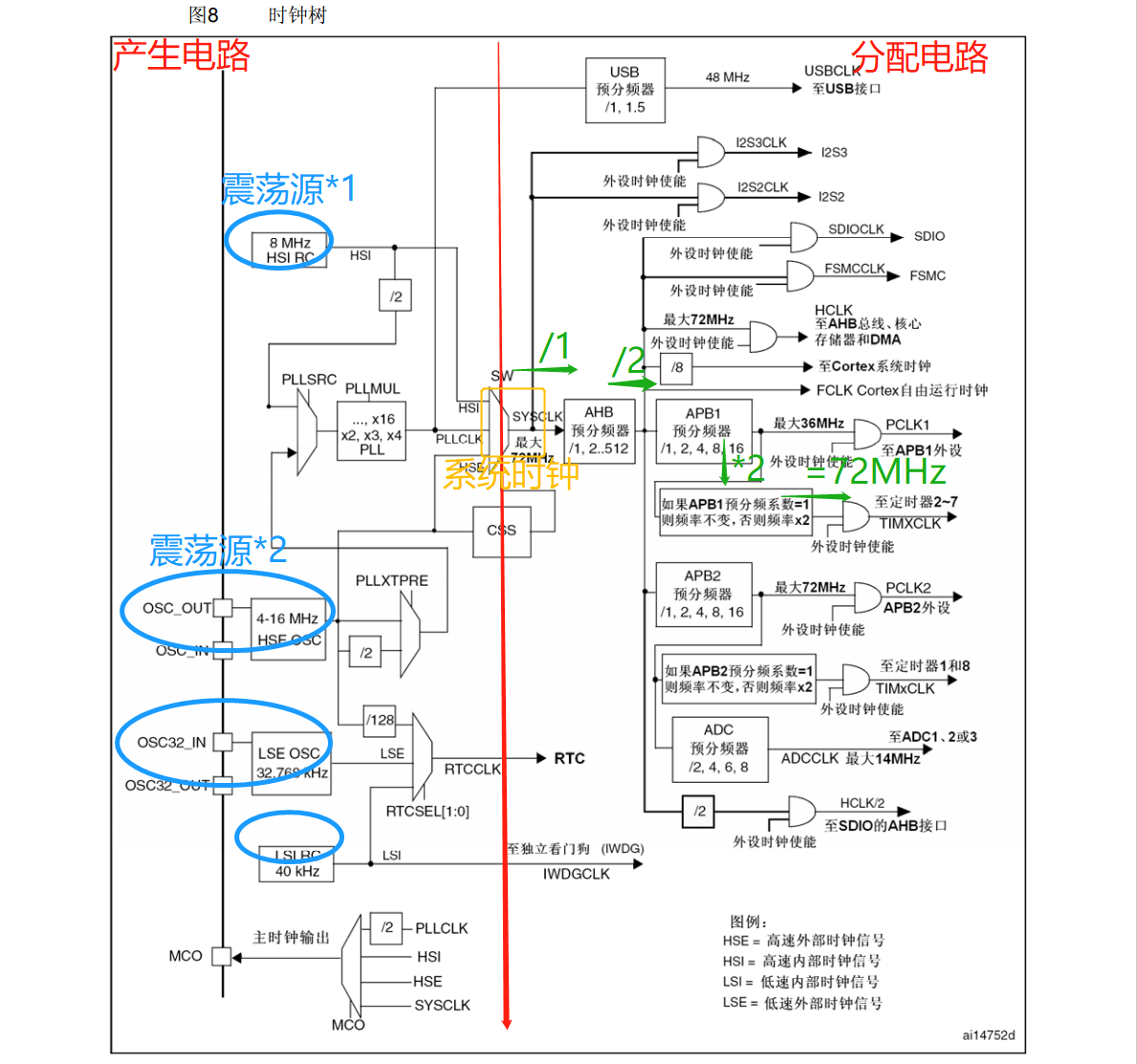

- 可以理解为计数器,计时的过程是对基准时钟进行计数的功能。在STM32中,定时器的基准时钟一般是主频72MHz。(周期是频率的倒数)

- 这个基准时钟就是单片机的时钟周期,就是主频的倒数,CPU中最小的时间单位,定时器就是对这个时钟周期进行计数,看过了多少个时钟周期

- 时基单元:16位计数器,预分频器,自动重装寄存器。都是16位的。2^16 = 65536。如果预分频器设置最大,自动重装也设置最大,定时器的最大定时时间是72M/65536/65536 = 中断频率 = 1 / 59.65s(第一个65536是自动重装最大值,达到最大值计数器加一,计数器最大也是65535),周期接近一分钟。

- 不仅具备基本的定时中断功能,而且还包含内外时钟源选择,输入捕获,输出比较,编译器接口,主从触发模式等多种功能

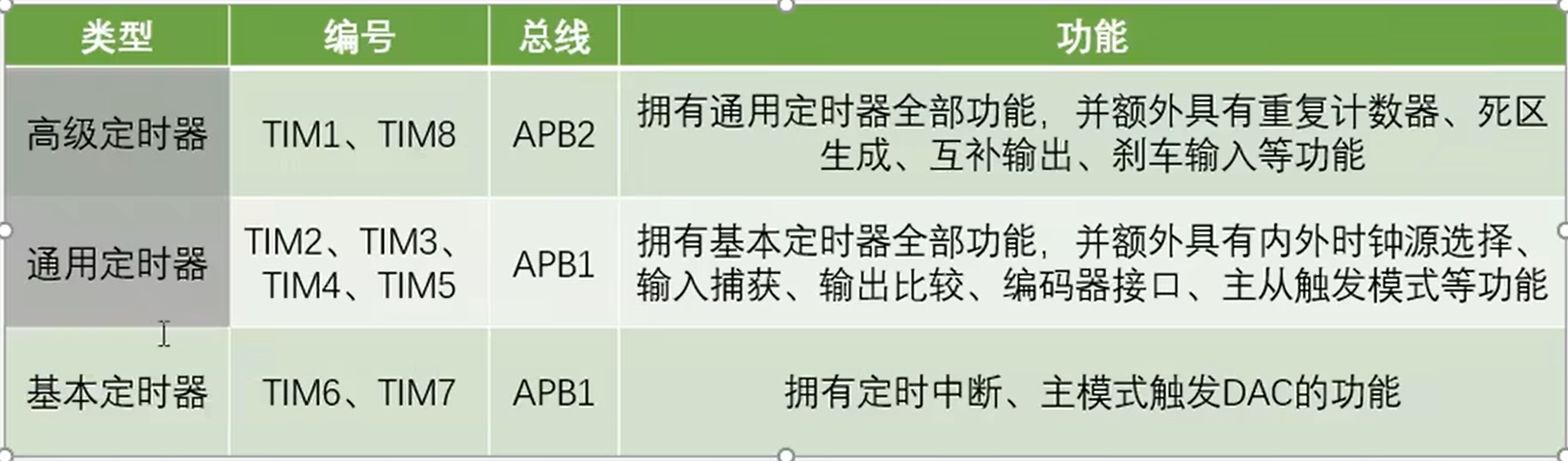

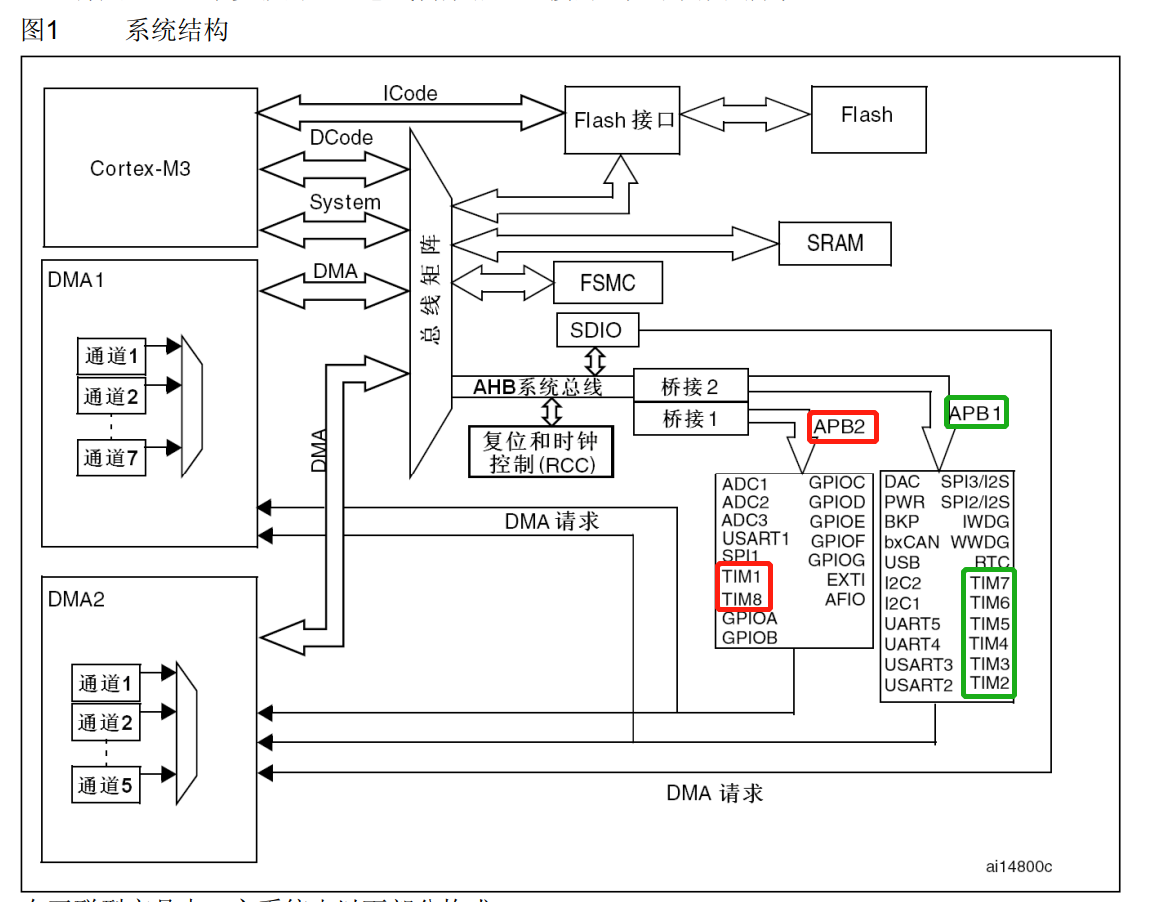

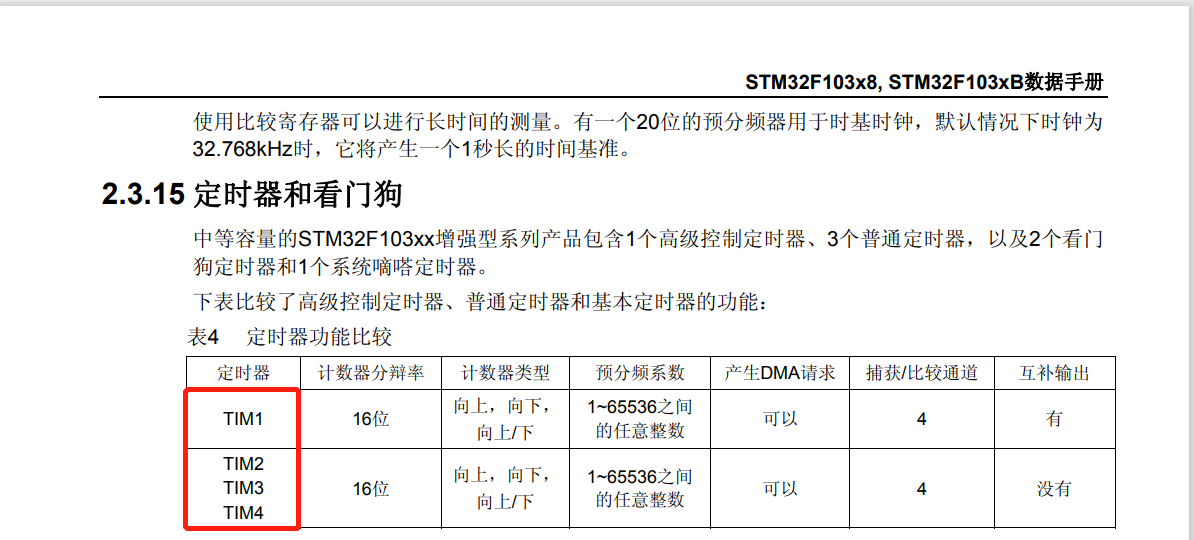

- 根据复杂度和应用场景分为高级定时器,通用定时器和基本定时器

【定时器的类型,编号,总线的对应情况】

STM32F103C8T6定时器资源:TIM1~TIM4

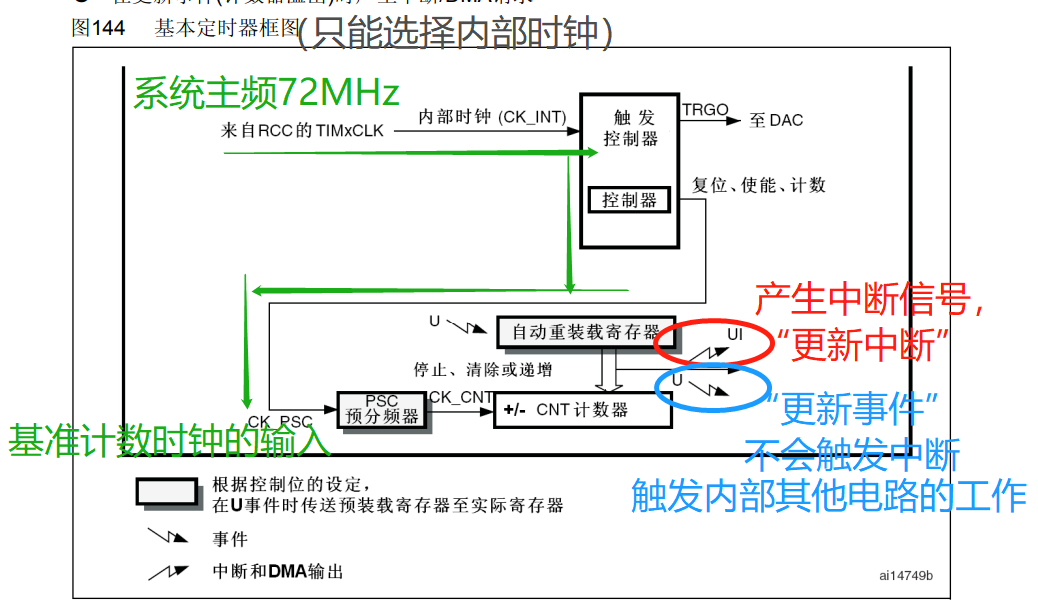

【基本定时器结构图】

- 基本定时器功能:定时中断,主模式触发DAC

- 基本定时器只能选择内部时钟

- 时基电路:最基本的计数计时电路包括预分频器,计数器和自动重装寄存器

- 预分频器

- 预分频器可以对72MHz的计数时钟进行预分配,对输入的基准频率提前进行一个分频的操作

- (寄存器写0是不分频,输出频率 = 输入频率 = 72MHz),(预分频器写1是2分频,输出频率 = 输入频率 / 2 = 36MHz)

- 实际分频系数 = 预分频值 + 1

- 目的:把72MHz分成想要的频率。比如1MHz,每周期1us,这样便于计算

- 记忆:刀切蛋糕,一刀切两块

- 理解:预分频器实质是寄存器,如果设置值为3,则每个时钟上升沿预分频加一。取值范围为(0 1 2 3)。四个数,就是4分频

- 计数器

- 对预分频后的计数时钟进行计数(使用向上计数模式:计数器从0开始,向上自增,记到重装值,清零同时申请中断)

- 计数时钟每来一个上升沿,计数器的值+1,故计数器的值会在计时过程中不断地自增运行,当自增到目标值时产生中断,完成定时的任务

- 自动重装载寄存器(存储目标值的寄存器)

- 在此之中存储的是写入的计数目标

- 在运行过程中,计数值不断自增,自动重装值是固定的目标,当计数值等于自动重装值时,也就是计时时间到了

- 产生中断信号,并清零计数器,计数器将自动开始下一次的计数计时

- 主从触发模式(让内部硬件在不受程序的控制下实现自动运行)

- 在使用DAC时,需要用DAC输出一段波形。每隔一段时间触发一次DAC,让它输出下一个电压点

- 主模式:把【定时器的更新事件】映射到触发输出TRGO(Trigger Out)的位置,TRGO直接接到DAC(数模转换器)的触发转换引脚上

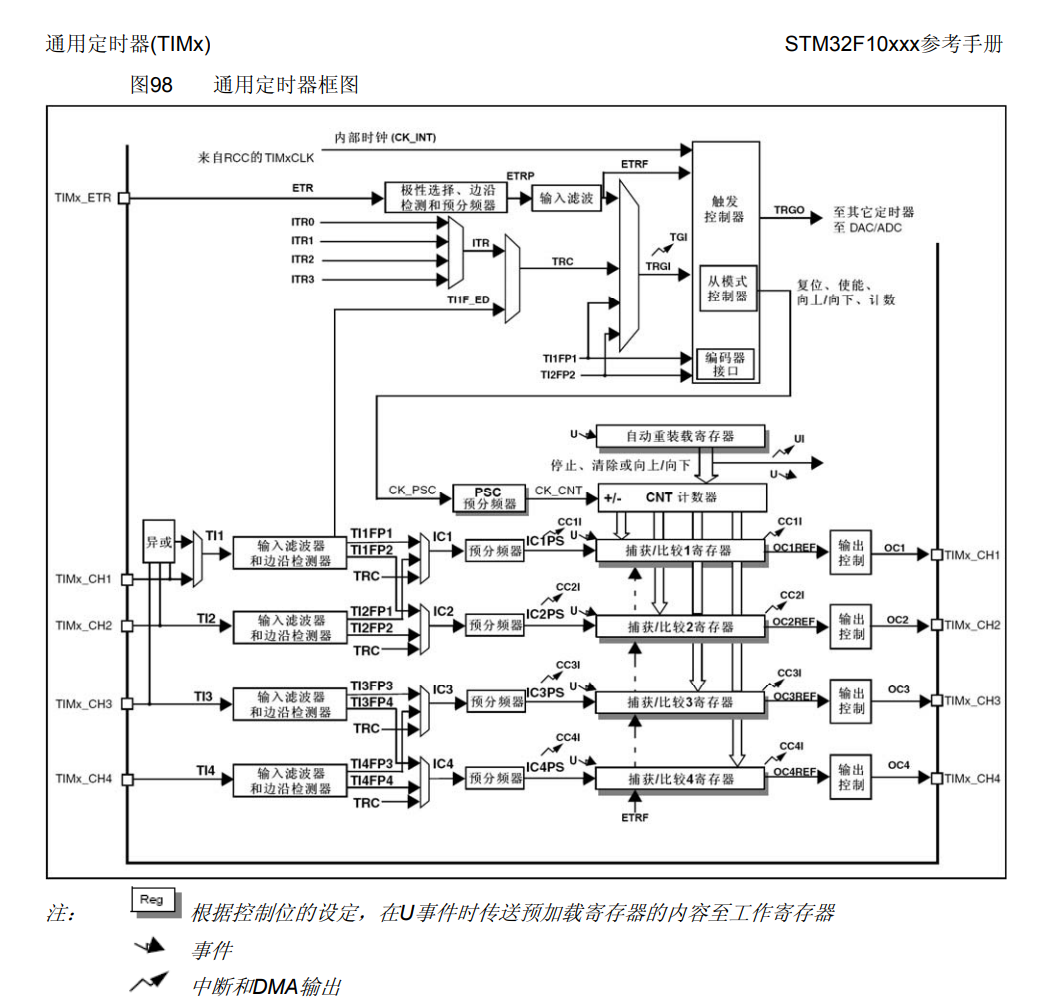

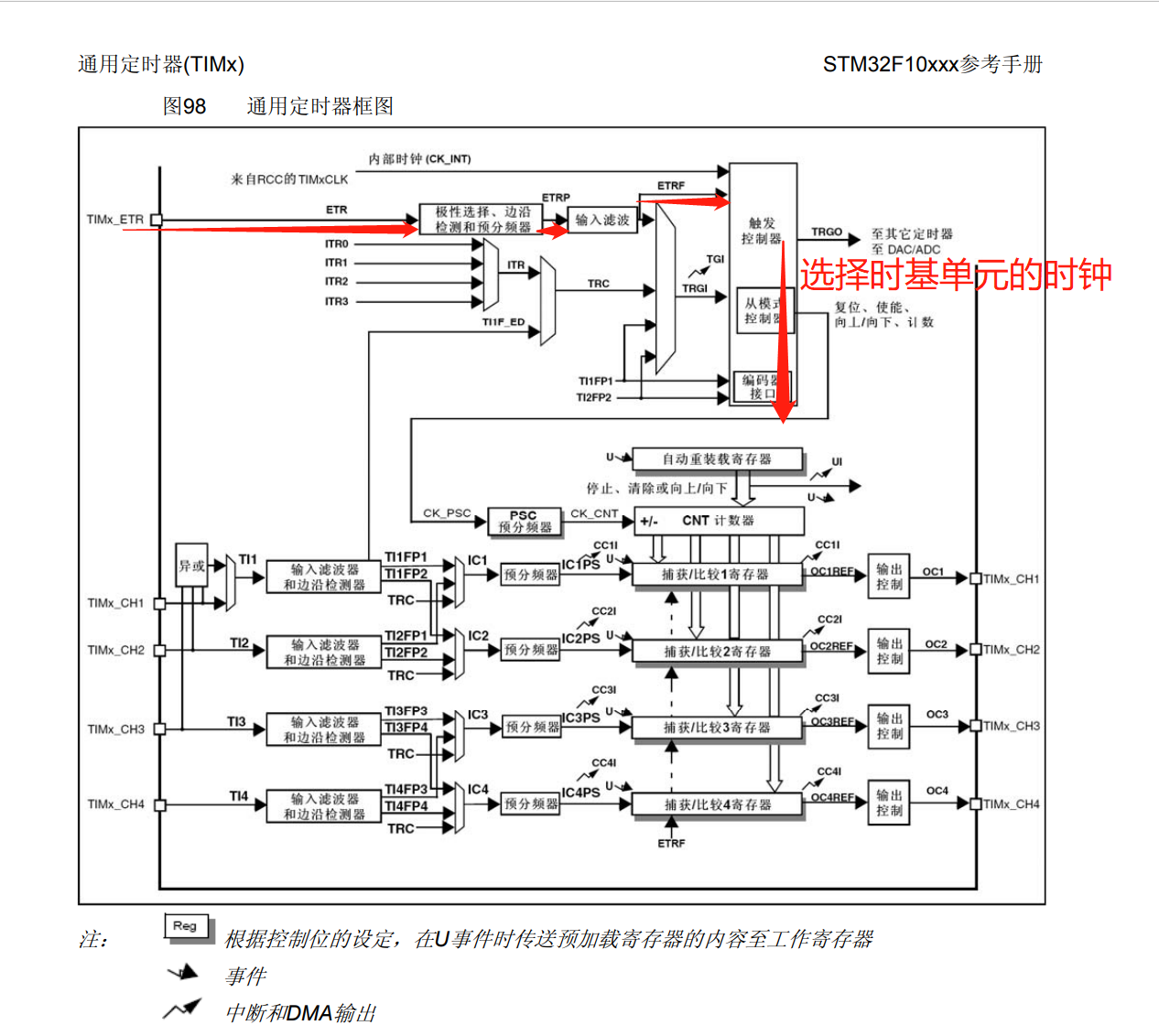

【通用寄存器结构图】

- 计数器的计数模式:通用定时器和高级定时器不仅支持向上计数,同时支持向下计数模式和中央对齐模式。向下计数模式指从重装值开始,向下自减,减到0之后,回到重装值同时申请中断。中央对齐的计数模式指从0开始先向上自增,增到重装值申请中断,再向下自减到0,申请中断。

- 内外时钟源选择:对于通用定时器,时钟源不仅可以选择内部的72MHz时钟,还可以选择外部时钟

- 外部时钟模式2

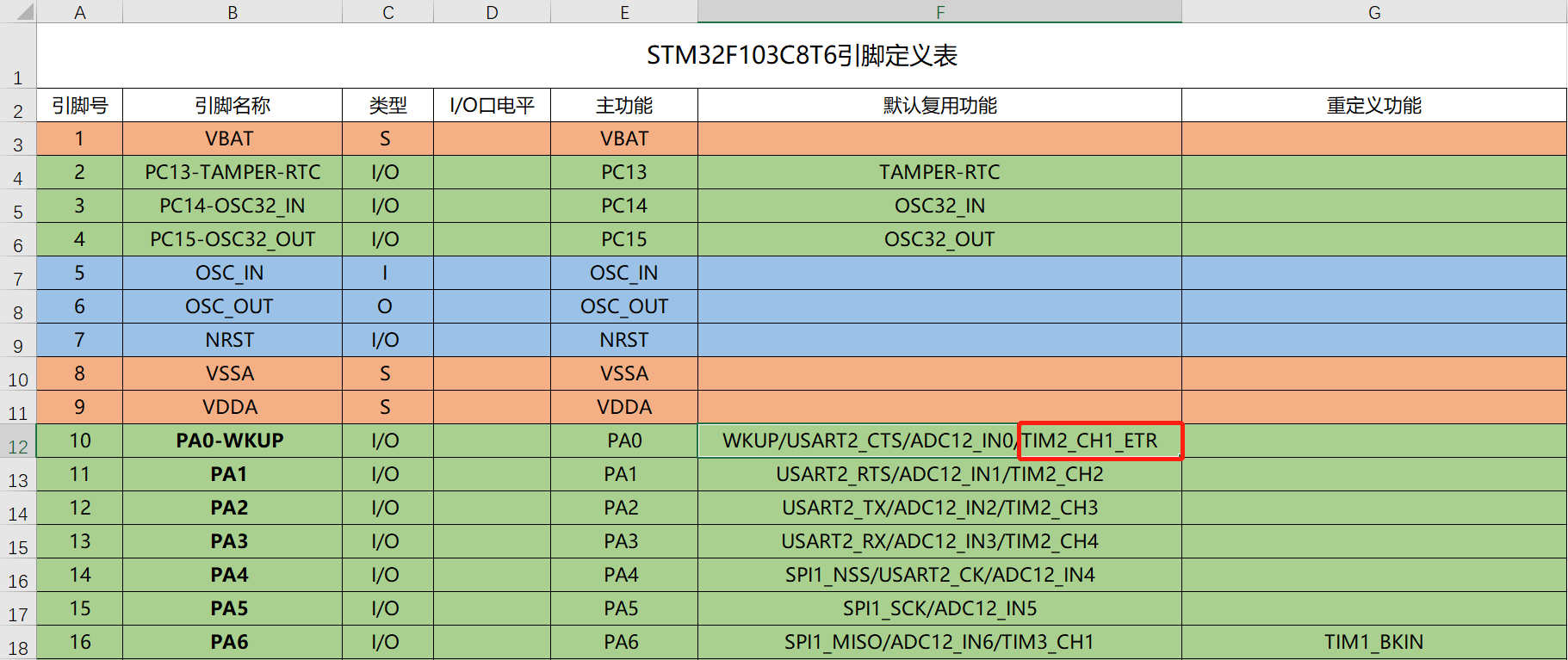

![]() 外部时钟来自于TIMx_ETR引脚上的外部时钟。

外部时钟来自于TIMx_ETR引脚上的外部时钟。![]() 例如TIM2_CH1_ETR就是TIM2(定时器)的CH1(通道)和ETR(外设)都复用在了PA0这个引脚。CH是通道Channel的意思

例如TIM2_CH1_ETR就是TIM2(定时器)的CH1(通道)和ETR(外设)都复用在了PA0这个引脚。CH是通道Channel的意思 -

外部时钟模式1(待补充):其输入可以是ETR引脚,其他定时器,CH1引脚的边沿,CH1引脚和CH2引脚

- 外部时钟模式2

- 输入捕获(第三部分)

- 输出比较(第二部分)

【时基单元运行的一些细节问题】

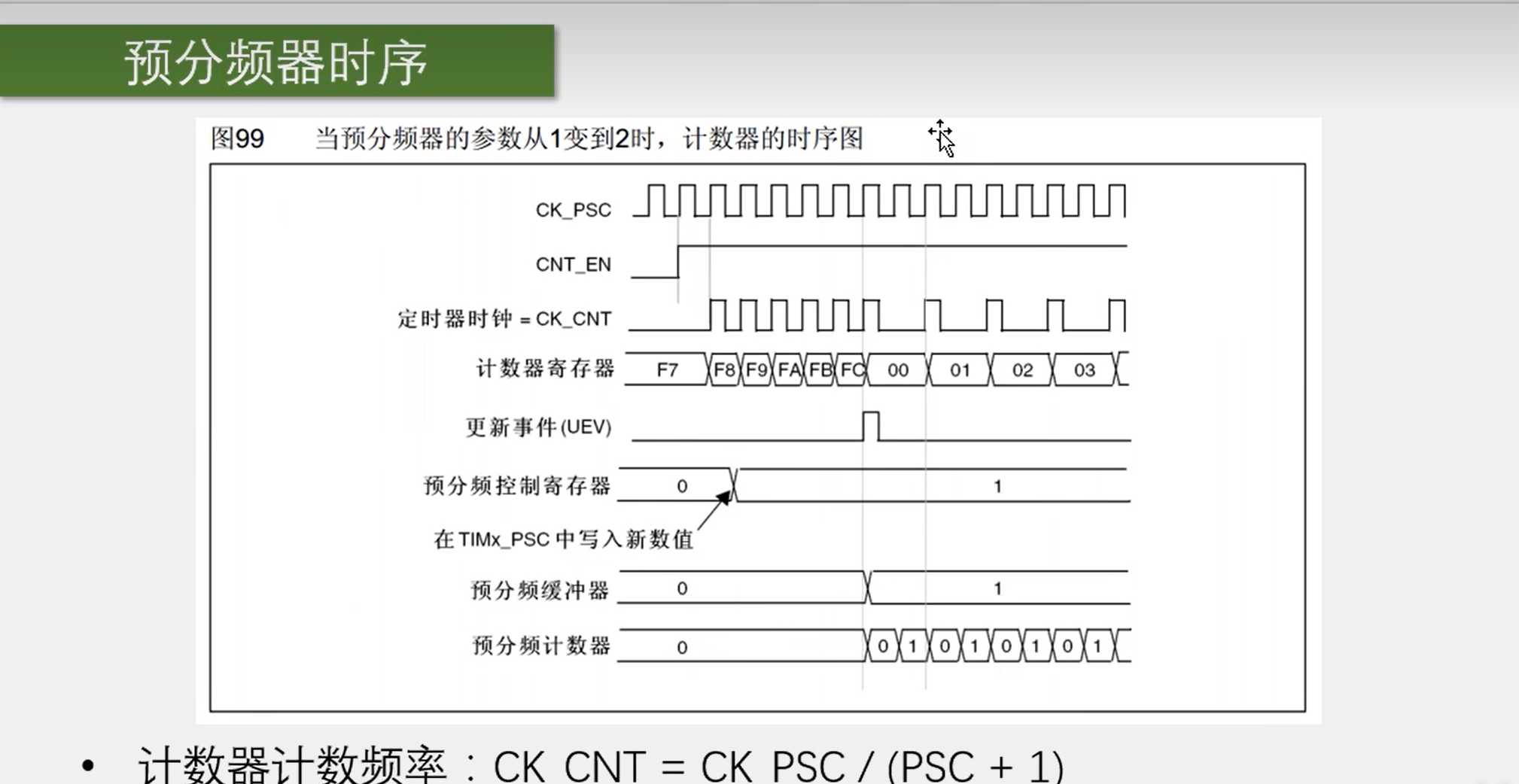

【预分频器时序】

- 重要前提:在改变预分频系数的时候,得等到下一次计数周期才能改变实际的频率

- 预分频器的输入时钟CK_PSC:选内部时钟的话一般是72MHz

计数器使能CNT_EN:高电平计数器正常运行,低电平计数器停止

计数器时钟CK_CNT:既是预分频器的时钟输出也是计数器的时钟输入 - 计时器未使能时,计数器时钟不运行。使能后,前半段预分频器系数为1,计数器的时钟等于预分频前的时钟;后半段预分频器系数为2,计数器的时钟变为预分频器前时钟的一半

- 在计数器时钟的驱动下,计数器寄存器也随时钟的上升沿不断自增,在“FC”后计数值变为0,可以推断出自动重装值就是FC,因为当计数值和重装值相等,并且下一个时钟来临时,计数值才清零,同时产生一个更新事件

- 预分频寄存器的缓冲机制:预分频控制寄存器是供我们读写用的并不直接决定分频系数;而预分频缓冲寄存器才是真正起作用的。避免时钟的分频系数突然改变,导致一个计数周期内,前后部分的频率不一样。

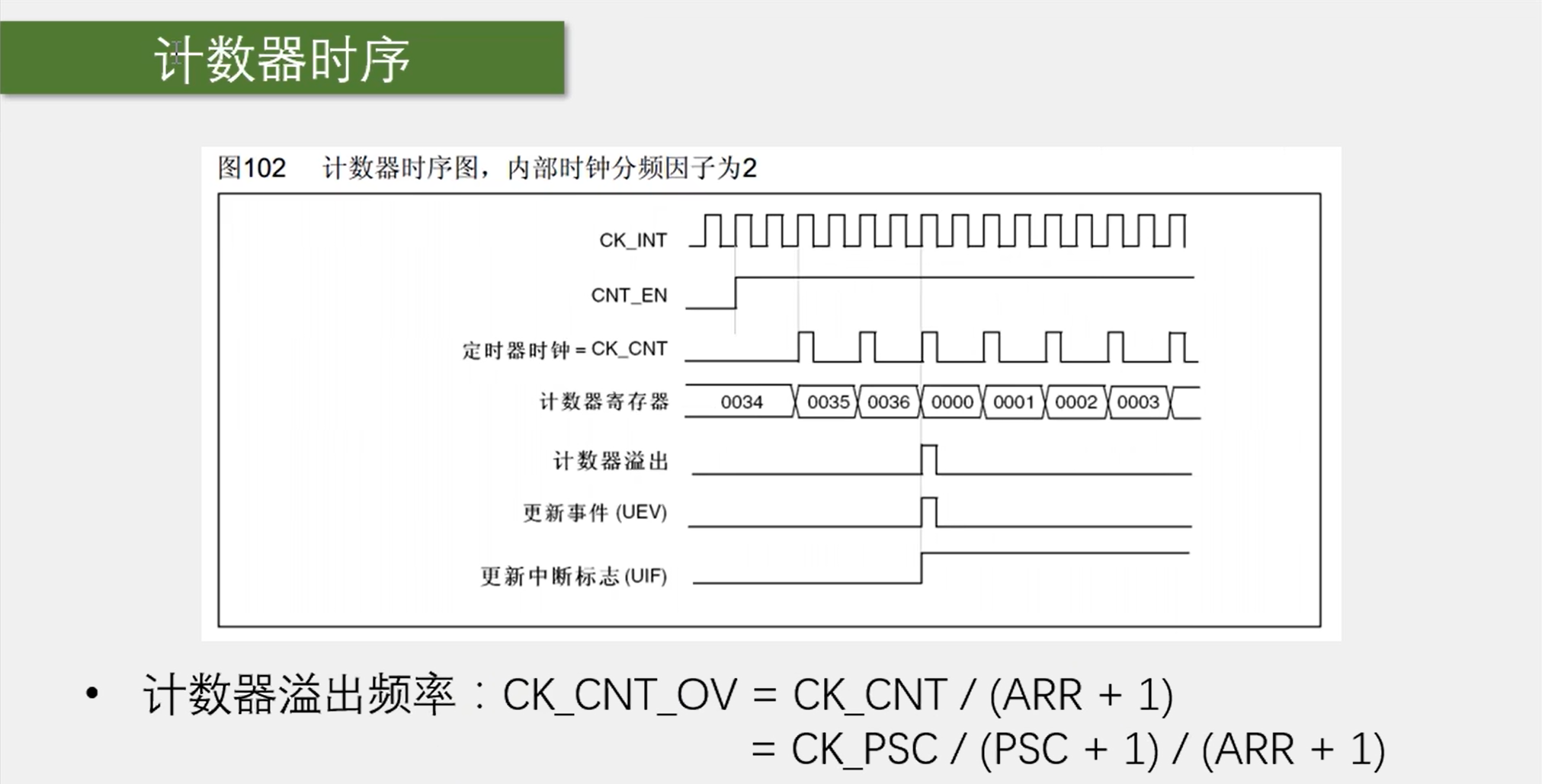

【计数器时序】

-

预分频器的输入时钟CK_PSC:选内部时钟的话一般是72MHz

-

计数器使能CNT_EN:高电平计数器正常运行,低电平计数器停止

-

计数器时钟 = CK_PSC / 2,计数器在时钟的每个上升沿自增,溢出后清零,产生一个更新事件的脉冲,另外还会将更新中断标志位UIF置1,随即申请中断,中断响应后,需要在中断程序里手动清零

-

通过设置ARPE位,可以选择是否使用预装功能

【RCC时钟树】

外部时钟来自于TIMx_ETR引脚上的外部时钟。

外部时钟来自于TIMx_ETR引脚上的外部时钟。 例如TIM2_CH1_ETR就是TIM2(定时器)的CH1(通道)和ETR(外设)都复用在了PA0这个引脚。CH是通道Channel的意思

例如TIM2_CH1_ETR就是TIM2(定时器)的CH1(通道)和ETR(外设)都复用在了PA0这个引脚。CH是通道Channel的意思

浙公网安备 33010602011771号

浙公网安备 33010602011771号