后仿真+后仿真过的电路的细节点

[学习笔记]Cadence Virtuoso中CONFIG功能的使用 - 知乎 (zhihu.com)

LDO轻重负载及其ESR概念

ESR: 与负载电容串联的电阻

轻重载:与负载电容并联的负载,对应指标中有相应的电流;输出电压/电流 的值就是并联电阻值

dropout电压定义

对应仿真的是dc,观察随着电源电压增大输出电压趋于稳定后和电源电压的差值,dropout=vdd-95%*vout 一般其值越小越好

后仿真有输出波形但与前仿真有差别的原因

网表和cdf文件的端口没有一一对应,顺序一定要一致

电源电压的设置

在仿真LDO中,对于输出电压在4.4V则电源电压得高于4.4,至少为4.75后续仿真才不会有错

而对于1.9V的输出,则可以电源电压设置在4.5V时电路要正常工作

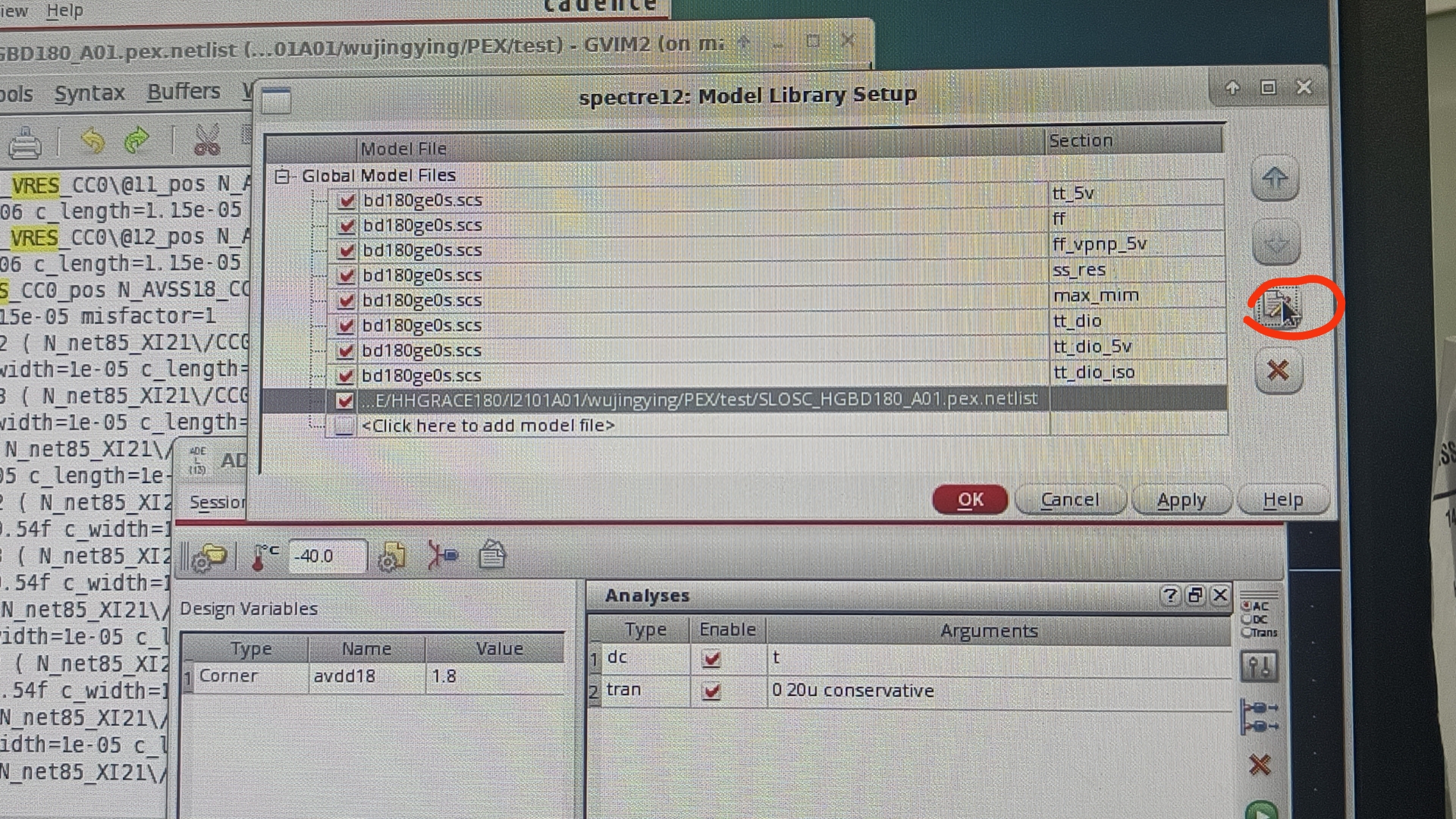

后仿真工艺角仿真出现以下错误的解决方法:可能是工艺角重复选择了,如同时选中了两个ff_5v

Please try to add `+spice' in command line or option `redefinedparams' in netlist to avoid these type of errors.

在已知的仿真测试电路中如何确定用的是后仿还是前仿数据

在ADE test editor中点击simulation netlist display查看是否含有后仿网表

BG电路后仿与前仿真出入问题

可能是BG电路在某些工艺角的后仿真没有正常启动,需要先跑tran把电路启动,再把结果给其他仿真

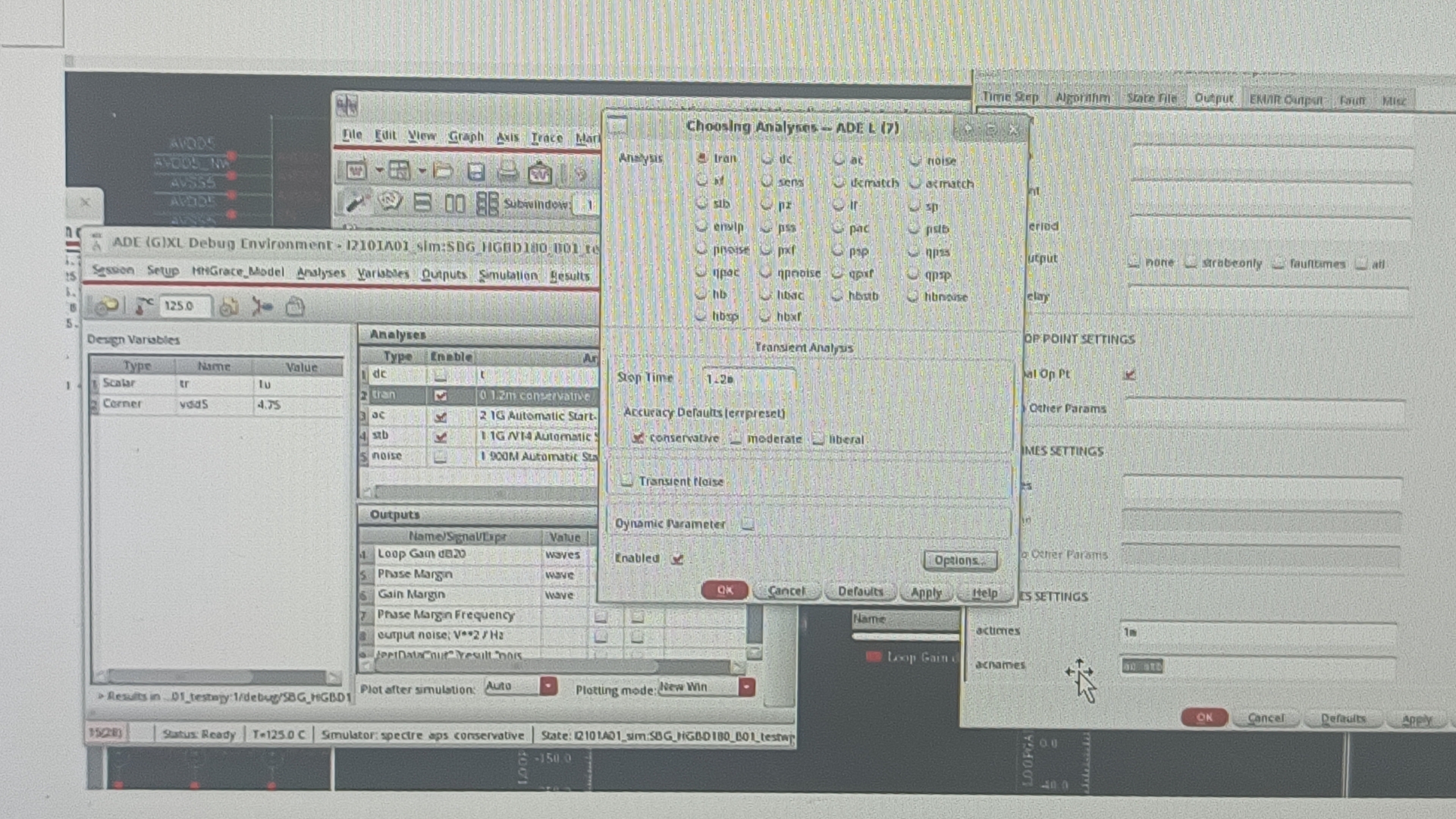

在ADL中tran的选项——>option——>output——>设置actime(表示设置完时间后,电路正常启动),设置acnames(表示在启动后电路所要跑的其他仿真)

LVS出现版图电路图npn器件不对应,选中YC解决

振荡器的后仿真

如果振荡器后仿真不能正常工作,除了网表可能错误的情况外,还可能需要设置电压为vpwl设定由0到电源电压一个抬升的变化,表示让振荡器起振。

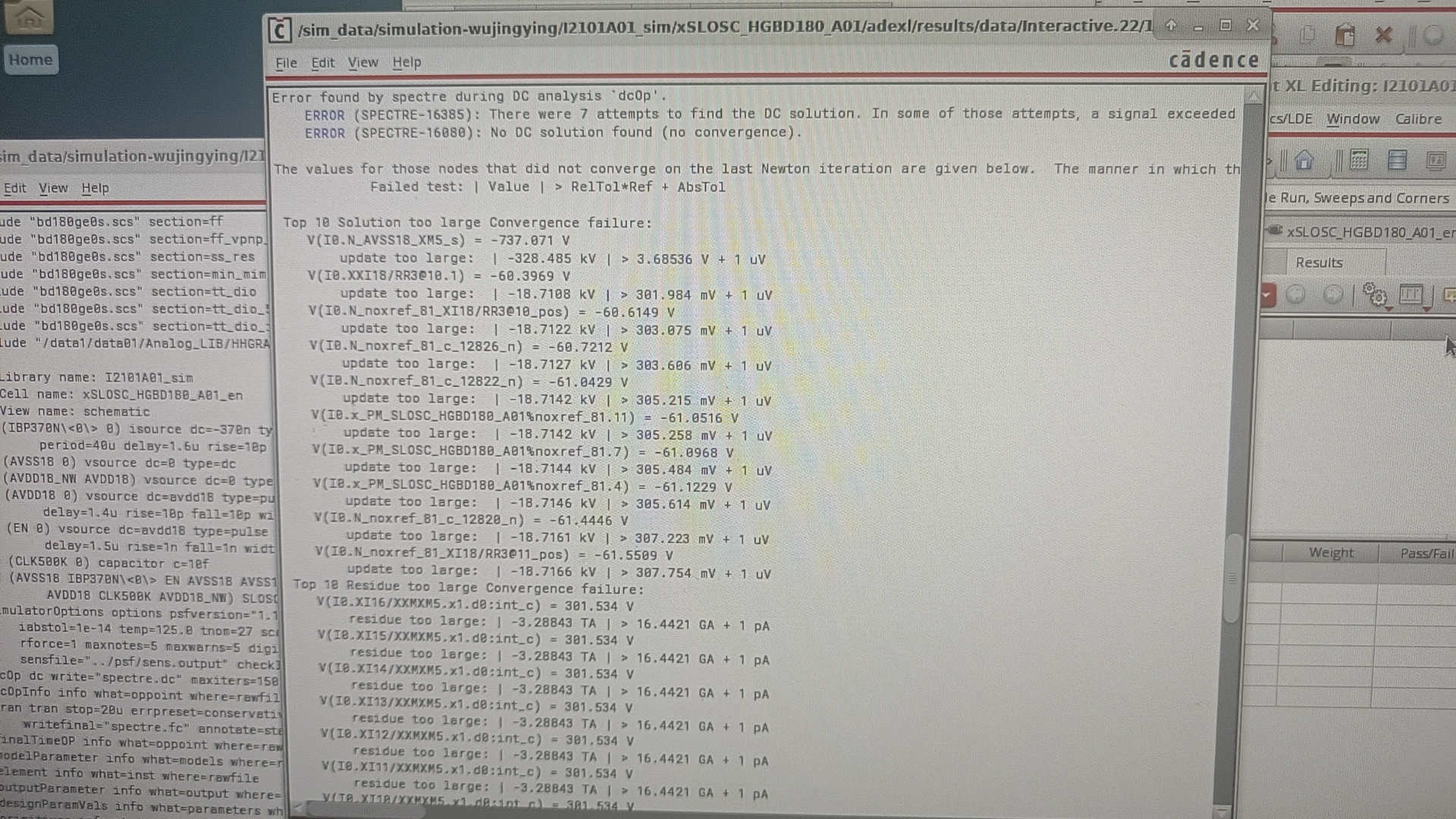

振荡器后仿真工艺角不收敛

将电流源设置为ipwl,电压源也设置为vpwl或者vpulse,且ipwl由0抬升到所需电流值的delay时间设置的比vpwl由0抬升到所需电压值的时间慢1ns,以保证收敛起振

收敛性问题

仿真问题 - Analog/RF IC 设计讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

Time step too small 解决办法 - Analog/RF IC 设计讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

后仿真工艺角出现不收敛报错eval err的解决方法:给电路中的电容上极板赋予初始值,在前仿中,通过ADE L Test Editor——Simulation——Convergence——initial Condition赋值,通过ADE L Test Editor——Simulation——Netlist——Create查看网表出现“ic I0.INP=0”表示赋值成功,其中,“I0.”表示在symbol里面的节点

具体报错

后仿方法一(不适用多个工艺角报错情况)

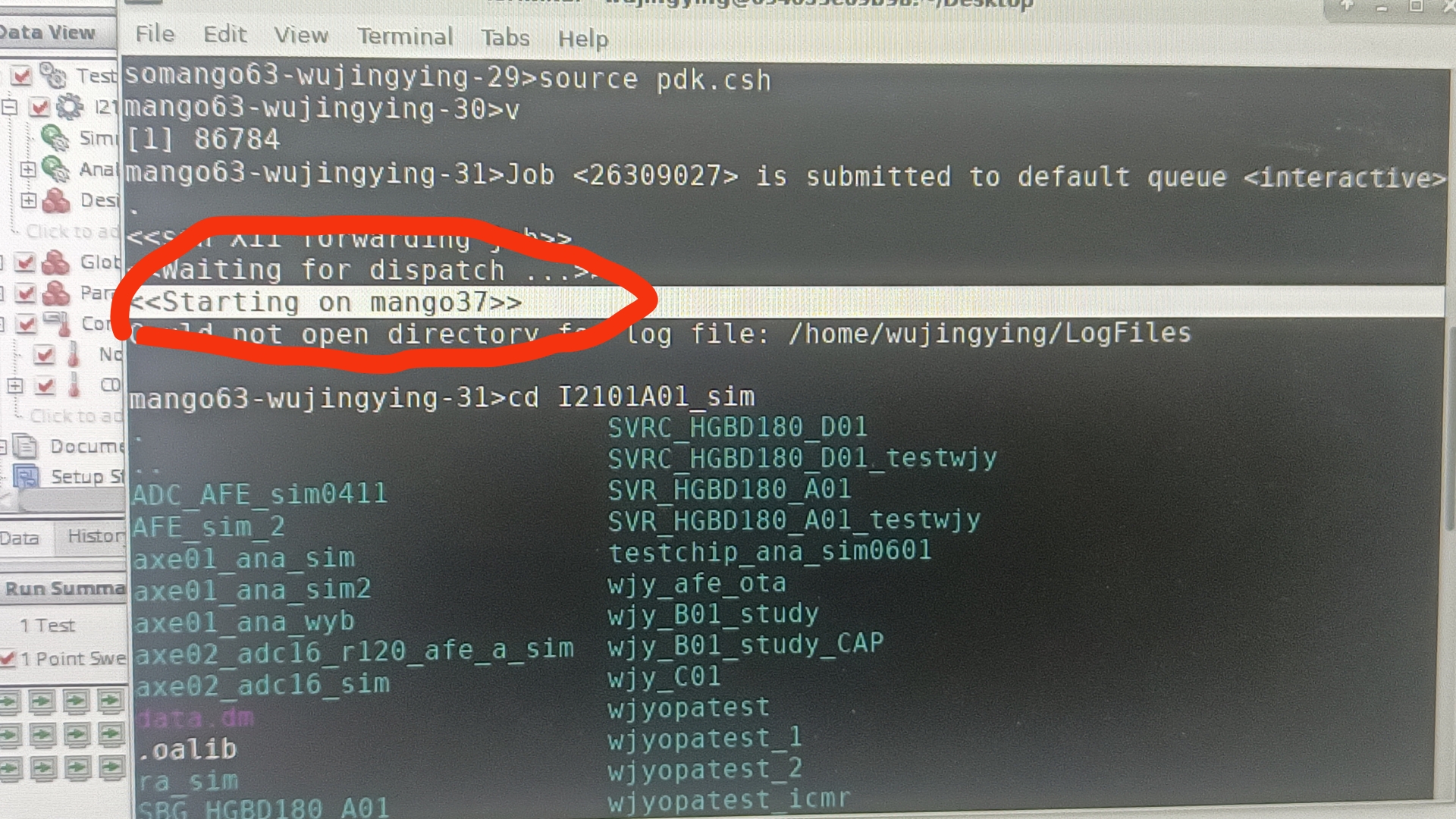

在后仿中,不可通过上述直接在电路图点击节点的方式赋予初始值,而是要通过终端打开编辑sim_data目录下的网表(Netlist)手动添加“ic I0.INP=0”这句话,而且每个connor的网表相互独立,需要挨个添加,并且在仿真的时候,在每个connor下的ADE L需要挨个打开,选择Choosing Simulator/Directory/Host——Host mode——local,必须在本地仿真,否则每次仿真都会重新生成一个新的netlist(网表),具体操作方法如下

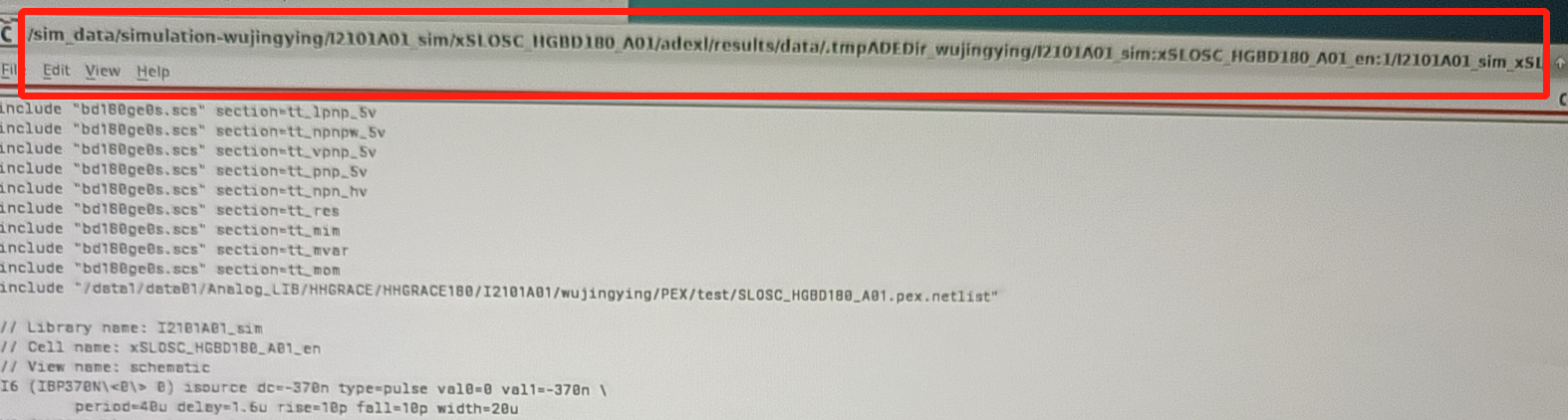

1.通过打开的netlist页面找到其所在路径

2.通过终端打开netlist才能编辑

打开input.scs文档

3.按“i”键进行编辑——按“Esc”退出编辑——按冒号加上“wq!”表示保存并退出(“q!”表示强制退出不保存)

4.检查

回到ADE L页面点击Simulation——Netlist——Display查看网表是否出现添加文字

5.运行

在Simulation——run不需要Netlist and run否则会从新生成网表

(91条消息) [Linux打怪升级之路]-vim编辑器(看就能马上操作噢)_:wq命令怎么使用_小蜗牛~向前冲的博客-CSDN博客

后仿方法二 此方法就是修改步长的方法

直接点击ADE XL——Simulatior——option——TOLERANCE OPTIONS讲里面的参数值都设置为默认值少一个数量级

减小仿真精度

如何编辑后仿真网表

打开并修改路径

后仿真使用config仿真减小误差

删除指定文件文件

rm core.*

docker:overlay2过大 清理 - 简书 (jianshu.com)

查看local工作区

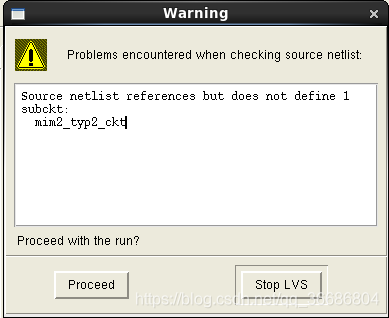

后方提参(出现Source netlist references but does not define 1 subckt:)

出现类似以下报错

定义文件没有添加

选择 Calibre —— setup—— Netlist export ——include file 添加subcircuit.cdl文件所在路径

浙公网安备 33010602011771号

浙公网安备 33010602011771号