[笔记] [数字逻辑设计] 时序电路设计

时序电路设计

一些其他类型的 Flip-Flop

J-K 触发器(J-K Flip-Flop)

与 S-R 触发器类似,但当 J=K=1 的状态可以接受,效果为将触发器的状态取反,同样,J-K 触发器也会产生一次性采样问题(被一个 Glitch 影响)

T 触发器(T Flip-Flop)

J=K=T 的 J-K 触发器,其功能为当 T=0 的时候触发器维持原状,当 T=1 的时候触发器状态翻转

次态(特征)方程与激励方程(Next State(Characteristic) Equation & Excitation Equation)

次态方程(在电路分析时使用):通过输入和现态得到次态的方程

激励方程(在电路设计时使用):通过现态和次态得到输入的方程(应当具有怎样的输入)

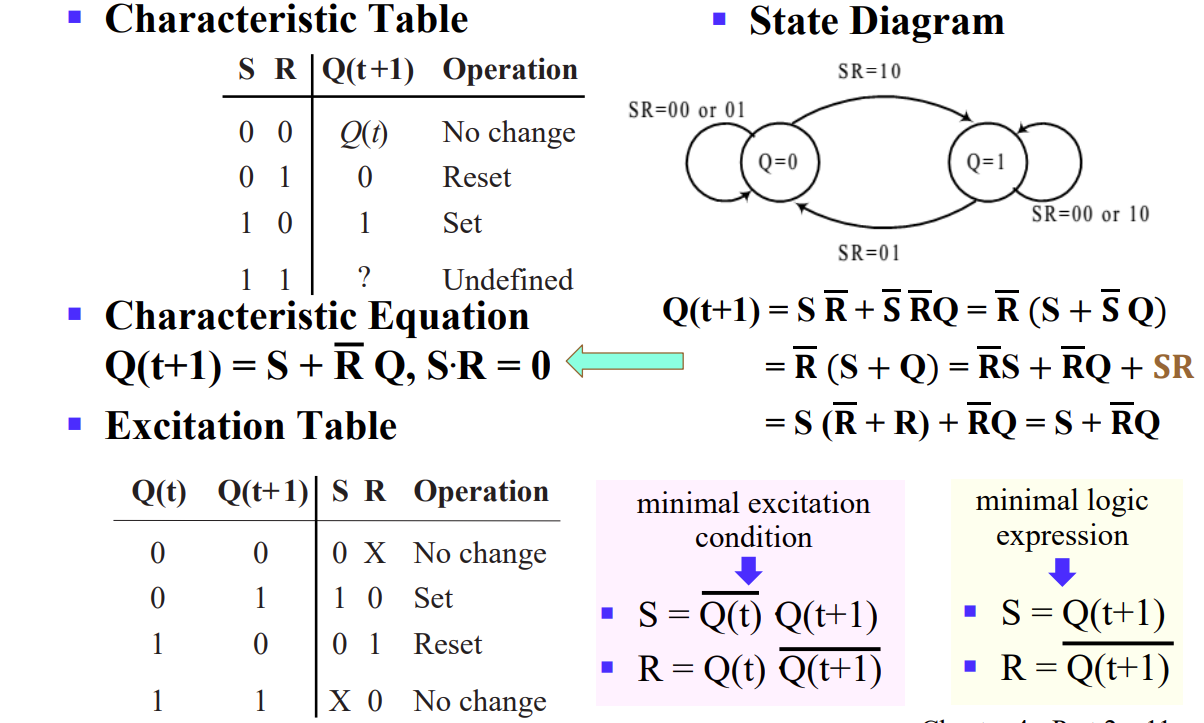

下面是 D 触发器和 S-R 触发器的次态方程以及激励方程,注意区分两个方程

具体的时序电路设计的例子我没有记录,建议结合具体的题目,自己多练一下状态图和状态表的画法

浙公网安备 33010602011771号

浙公网安备 33010602011771号