[笔记] [数字逻辑设计] 可编程模块

可编程模块

可编程逻辑器件(Programmable Logic Device)

- Read Only Memory (ROM):AND 门阵列固定,OR 门阵列可编程

- Programmable Array Logic (PAL):AND 门阵列可编程,OR 门阵列固定

- Programmable Logic Array (PLA):AND 门阵列可编程,OR 门阵列可编程

- Complex Programmable Logic Device (CPLD) / Field Programmable Gate Array (FPGA)

前三种器件均为:输入经过 AND 门阵列再经过 OR 门阵列,从而得到类似最小项之和的形式

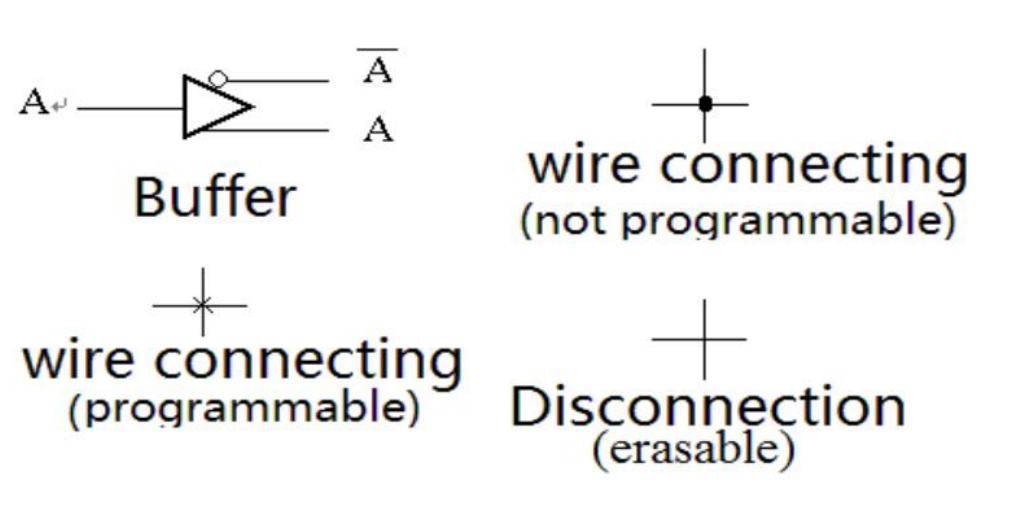

一些记号

ROM

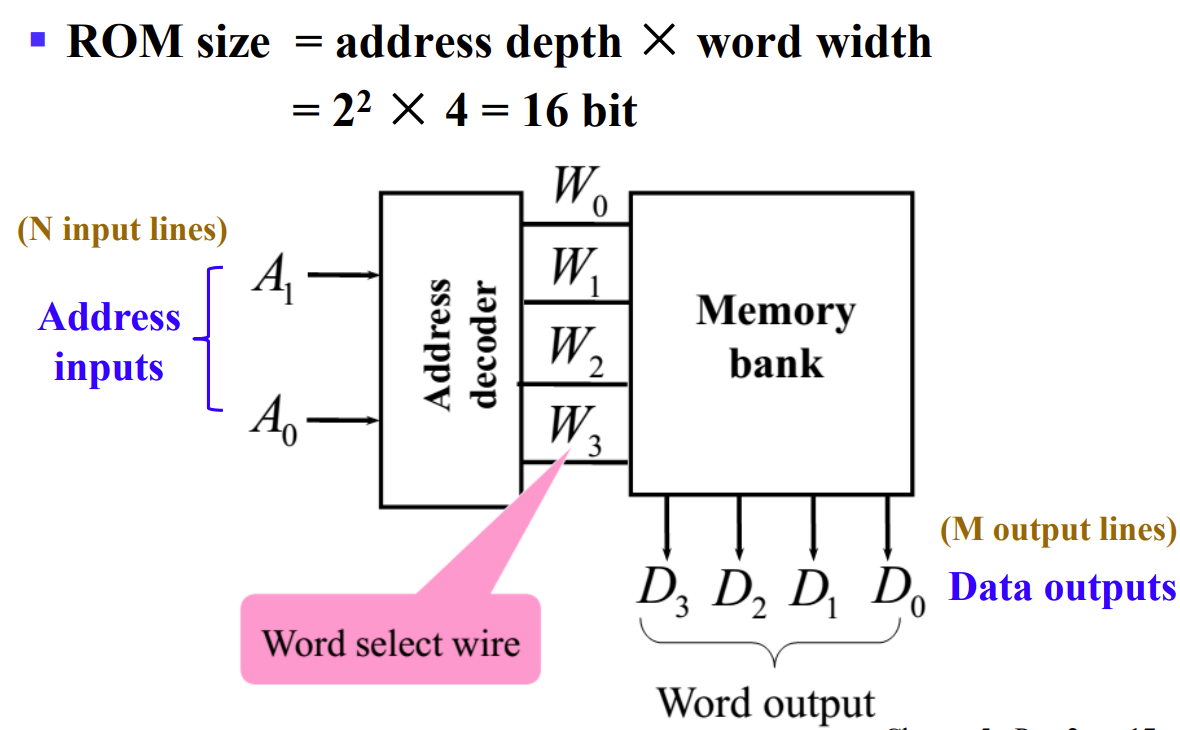

有 \(n\) 个输入,\(m\) 个输出和 \(2^n\) 个经过译码的最小项

其与门阵列是固定的,无法编程;或门阵列是可以编程的

因此,可以将一个 ROM 或者 PROM 简单地看作一个有多个输出的真值表,从而将 ROM 视作一个存储单元,输入的 \(n\) 个 bit 相当于数据的地址

下图展示了一个 ROM 的结构

其中 ROM 的大小通过地址深度乘上字宽得到,地址深度即为地址的个数,字宽表示一个数据有多少个二进制位

下面是一个具体的例子

四个或门的连接点是可以修改的

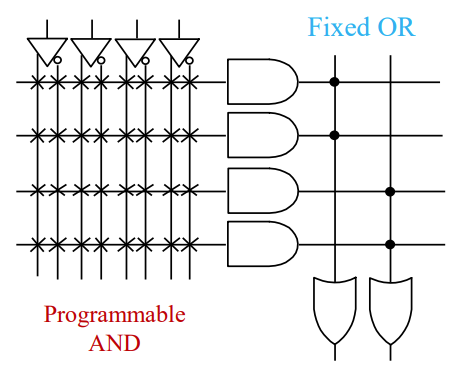

Programmable Array Logic (PAL)

与 ROM 相反,PAL 的与门阵列可以编程,而或门阵列是固定的,无法修改,下面是一个例子

需要注意的是,PAL 在使用时可能会出现与门个数不够的情况,这个时候可以通过将表达式中一部分最小项之和先计算出来,再重新放回前面的或门阵列中,下图是一个例子

Programmable Logic Array (PLA)

PLA 相比前面的几种可编程逻辑,其灵活性更强,因为它的或门阵列和与门阵列都是可以编程的

有时,输出的或门还会再加上可编程的异或门来实现更多的功能(controllable inverter),如下图

查找表(Lookup Tables, LUTs)

(其实没太看懂,建议自行寻找其他资料/kk)

思路 1:使用一个 MUX 进行查找

基础思路是使用静态内存(SRAM)与一个(可能较大的)MUX 进行数据的查找

由于上面一种思路可能需要非常大的 MUX,因此可以考虑使用树形结构的多层 MUX 来实现一个较大的 MUX 的功能

浙公网安备 33010602011771号

浙公网安备 33010602011771号