【5分钟+】计算机系统结构:CPU性能公式

计算机系统结构:CPU性能公式

基础知识

CPU 时间:一个程序在 CPU 上运行的时间。(不包括I/O时间)

主频、时钟频率:CPU 内部主时钟的频率,表示1秒可以完成多少个周期。

例如,主频为 4.1GHz,表示每秒可以完成 4.1*109 个时钟周期。

时钟周期:时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。

时钟周期 = 1 / 频率,例如 1/ 4.1*109 。

CPU 的时钟周期越短,CPU 性能越好。

指令周期:取出并执行一条指令的时间。

程序的时钟周期数

CPU时间 = 执行程序所需的时钟周期数 * 时钟周期时间

公式

指令周期:取出并执行一条指令的时间;

指令周期数CPI:平均每条指令耗费的时钟周期数

CPI = 执行程序所需的时钟周期数 / 所执行的指令条数

上面的公式换位置

执行程序所需要的时钟周期数 = CPI * 所执行的指令条数

CPU时间 / 时钟周期时间 = CPI * 所执行的指令条数

CPU时间 = CPI * 所执行的指令条数 * 时钟周期时间

我们约定 IC :所执行的指令条数,所以

CPU时间 = CPI * IC * 时钟周期时间

CPU时间 = (CPI * IC) / 时钟频率

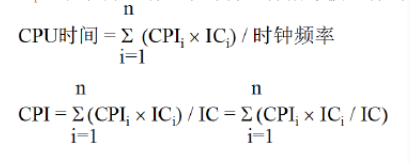

CPIi :第 i 种指令所需要的时钟周期数;

ICi :在程序运行过程中,第 i 种指令被运行的次数;

i 表示序号。

因为时间上 CPU 指令集指令很多,我们需要求得每条指令的平均耗时和程序使用到的指令、指令执行的次数。

总CPU时间为各个指令的 CPU时间 之和。

CPUi = (CPIi * ICi ) / 时钟频率

所以,公式总结如下

(ICi / IC) 反映了第 i 种指令在程序中所占的比例。

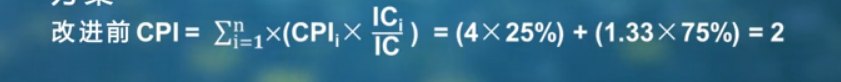

例题

各位同学,请看大屏幕:

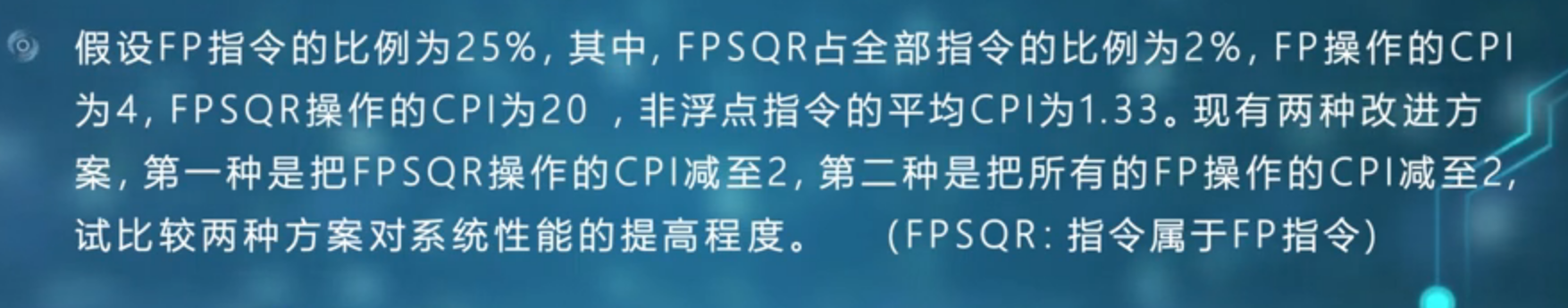

先求得未改进前的 CPI,目前有 FP指令(25%)、非浮点指令(75%),还知道了各自的 CPI 。

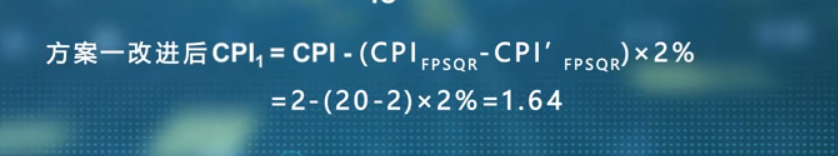

方案一改进后,提示的程度等于 (改进前CPI - 改进后CPI)。

因为本身也可以求得 FPSQR 在整体的比例,所以方案一不需要加入 FR。

看不明白的话,笔者讲解一下。

整体的 CPI 为 2

其中改进前, FPSQR 的 CPI 20*2% = 0.4 ,

其它指令CPI + FRSQR的CPI = 2;其它指令CPI=1.6;

改进后,FPSQR 的 CPI 2*2% = 0.04

提升了 0.36。

改进后的 CPI 需要时间 1.6 + 改进后的FRSQR的CPI = 1.64。

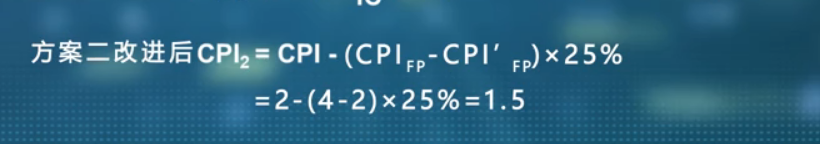

在上一道题目中,主要还是 CPI 相关的比例求解,相对来说比较容易。

但是如果加上频率和运行时间,则可能会有一些迷茫。此时就不能单纯看 CPI 了,要记住公式:

CPU时间 = CPI * IC * 时钟周期时间

1,计算机 A 的时钟频率为 800MHz,在计算机 A 上运行某程序需要 12S。现在硬件设计人员需要使用新技术设计一台计算机 B,希望能够将程序的运行时间缩短到 8S。使用新技术后,B 的 CPU 时钟频率大幅度提高,但是在 计算机 B 上,运行程序所需要的时钟周期数为 A 上的 1.5 倍。求在计算机 B 的 CPU 时钟频率至少为多少 GHz 才能达到所希望的需求。

也就是说,程序在 A、B 计算机上需要执行的指令数(IC)不变,但是时钟周期数变化了,即 CPI 变成了 1.5 倍。

按照 CPU 时间公式,得到在 A、B 计算机上:

1/800MHz * CPI * IC = 12S

1/nMHz * 1.5*CPI * IC = 8S

所以:

12/(CPI* 1/800) = 8/(CPI * 1.5 * 1/n )

最终可得到 n 为 1800,所以计算机 B 的 CPU 需要 1.8GHz 才能达到需求。

2,机器 M 的时钟频率为 200MHz,程序 P 在机器 M 上执行时间为 12S。将程序中的所有乘4的指令都换成 <<2 左位移两位的指令,得到程序 P'。在 M 中,乘法指令的 CPI 为 102,左移指令的 CPI 为 2,P 的执行时间为 P’ 的1.2 倍。则 P 中的乘法指令条数为?

在许多习题讲解中,是这样解答的:

P'的执行时间为10s,P的执行时间为P'的1.2倍,即为12s,多了2s,即多了200M×2=4×108个时钟周期,每条乘法指令比左移指令多100个时钟周期,即乘法指令数目为4×108/100=4×106。

笔者看了半天还是看不懂。

处理器性能优化的策略

影响CPU性能的三个方面:时钟频率、CPI、指令的条数。

减少指令的条数可以使得CPU更加简洁、使用较少的寄存器,系统代码也会别的更加简洁。例如 RISC-V。底层的指令减少,上层例如操作系统、汇编程序需要编写的代码亦会变多。

但是因为各种指令使用到的频率和周期内不同信息的访问次数,设计CPU是要考虑到优化指令的执行速度,优化高频访问的指令,分配更多的资源。例如X86。

浙公网安备 33010602011771号

浙公网安备 33010602011771号