【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART4--实验三

3.实验三:锁存器,触发器和寄存器

Part I :

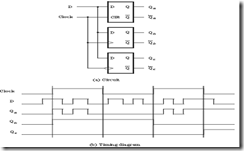

图3.1所示的电路由三部分不同的存储单元组成:一个D锁存器、一个上升沿触发的D触发器和一个下降沿触发的D触发器。

图3.1第四部分的电路与波形图

执行以下步骤:

1新建一个工程。

2编写一个包含了如上3个不同存储单元的VHDL实体。试写代码来实现如图3.1中所示的电路。

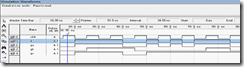

3编译并用逻辑单元映射结果来检测电路。并检测使用一个LUT实现的D锁存器和使用目标FPGA芯片提供的触发器来实现的D触发器。

4新建一个.vwf文件,并指定输入输出波形。画出如图3.1所示的波形。使用功能仿真来得到3个输出信号的波形。观察3个存储单元的不同特点。

Part 1代码:

d_latch:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY d_latch IS

6

7 PORT (

8

9 d : IN STD_LOGIC;

10

11 clk : IN STD_LOGIC;

12

13 q : OUT STD_LOGIC

14

15 );

16

17 END d_latch;

18

19 ARCHITECTURE trans OF d_latch IS

20

21 BEGIN

22

23 PROCESS (d, clk)

24

25 BEGIN

26

27 IF (clk = '1') THEN

28

29 q <= d;

30

31 END IF;

32

33 END PROCESS;

34

35 END trans;

dff_n:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY dff_n IS

6

7 PORT (

8

9 d : IN STD_LOGIC;

10

11 clk : IN STD_LOGIC;

12

13 q : OUT STD_LOGIC

14

15 );

16

17 END dff_n;

18

19 ARCHITECTURE trans OF dff_n IS

20

21 COMPONENT d_latch IS

22

23 PORT (

24

25 d : IN STD_LOGIC;

26

27 clk : IN STD_LOGIC;

28

29 q : OUT STD_LOGIC

30

31 );

32

33 END COMPONENT;

34

35 SIGNAL qm : STD_LOGIC;

36

37 SIGNAL qs : STD_LOGIC;

38

39 -- X-HDL generated signals

40

41 SIGNAL xhdl4 : STD_LOGIC;

42

43 BEGIN

44

45 um : d_latch

46

47 PORT MAP (

48

49 d,

50

51 clk,

52

53 qm

54

55 );

56

57 xhdl4 <= NOT(clk);

58

59 us : d_latch

60

61 PORT MAP (

62

63 qm,

64

65 xhdl4,

66

67 qs

68

69 );

70

71 q <= qs;

72

73 END trans;

dff_p:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY dff_p IS

6

7 PORT (

8

9 d : IN STD_LOGIC;

10

11 clk : IN STD_LOGIC;

12

13 q : OUT STD_LOGIC

14

15 );

16

17 END dff_p;

18

19 ARCHITECTURE trans OF dff_p IS

20

21 COMPONENT d_latch IS

22

23 PORT (

24

25 d : IN STD_LOGIC;

26

27 clk : IN STD_LOGIC;

28

29 q : OUT STD_LOGIC

30

31 );

32

33 END COMPONENT;

34

35 SIGNAL qm : STD_LOGIC;

36

37 SIGNAL qs : STD_LOGIC;

38

39 -- X-HDL generated signals

40

41 SIGNAL xhdl3 : STD_LOGIC;

42

43 BEGIN

44

45 xhdl3 <= NOT(clk);

46

47 um : d_latch

48

49 PORT MAP (

50

51 d,

52

53 xhdl3,

54

55 qm

56

57 );

58

59 us : d_latch

60

61 PORT MAP (

62

63 qm,

64

65 clk,

66

67 qs

68

69 );

70

71 q <= qs;

72

73 END trans;

顶层:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY su_3 IS

6

7 PORT (

8

9 d : IN STD_LOGIC;

10

11 clk : IN STD_LOGIC;

12

13 qa : OUT STD_LOGIC;

14

15 qb : OUT STD_LOGIC;

16

17 qc : OUT STD_LOGIC

18

19 );

20

21 END su_3;

22

23 ARCHITECTURE trans OF su_3 IS

24

25 COMPONENT d_latch IS

26

27 PORT (

28

29 d : IN STD_LOGIC;

30

31 clk : IN STD_LOGIC;

32

33 q : OUT STD_LOGIC

34

35 );

36

37 END COMPONENT;

38

39 COMPONENT dff_p IS

40

41 PORT (

42

43 d : IN STD_LOGIC;

44

45 clk : IN STD_LOGIC;

46

47 q : OUT STD_LOGIC

48

49 );

50

51 END COMPONENT;

52

53 COMPONENT dff_n IS

54

55 PORT (

56

57 d : IN STD_LOGIC;

58

59 clk : IN STD_LOGIC;

60

61 q : OUT STD_LOGIC

62

63 );

64

65 END COMPONENT;

66

67 -- Declare intermediate signals for referenced outputs

68

69 SIGNAL qa_xhdl0 : STD_LOGIC;

70

71 SIGNAL qb_xhdl1 : STD_LOGIC;

72

73 SIGNAL qc_xhdl2 : STD_LOGIC;

74

75 BEGIN

76

77 -- Drive referenced outputs

78

79 qa <= qa_xhdl0;

80

81 qb <= qb_xhdl1;

82

83 qc <= qc_xhdl2;

84

85 ul : d_latch

86

87 PORT MAP (

88

89 d,

90

91 clk,

92

93 qa_xhdl0

94

95 );

96

97 udp : dff_p

98

99 PORT MAP (

100

101 d,

102

103 clk,

104

105 qb_xhdl1

106

107 );

108

109 udn : dff_n

110

111 PORT MAP (

112

113 d,

114

115 clk,

116

117 qc_xhdl2

118

119 );

120

121 END trans;

Part II :思考题

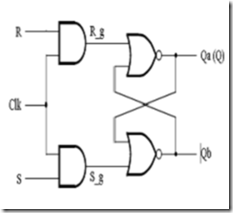

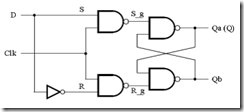

1)图3.2描述了一个RS锁存器电路。一个用VHDL逻辑表达式来描述这个电路的设计代码如图3.3所示。若是在一个有4输入查找表LUT的FPGA芯片中建立这个锁存器的话,仅需要一个LUT。

图3.2 RS锁存器 图3.3 RS锁存器的逻辑描述

尽管这样可以仅用一个LUT来实现设计,但是这样的锁存器不能观测其内部信号,如R_g和S_g,因为LUT不能将它们的输出。为了能够观测这些内部信号,有必要在代码中加入一个编译指令。如在图3.3中使用的一个VHDL属性声明语句中的keep指令,它使Quartus II编译器能够分别使用不同逻辑元素来编译信号R_g、S_g、Qa和Qb。编译后产生的电路如图3.4.b所示。

图3.4.b 编译后的电路

执行以下步骤:

1创建一个新的Quaryus II工程。

2使用图3.3中的代码来生成一个VHDL文件,并将其包含进工程中。

3编译工程,使用Quartus II RTL观测器来检查VHDL代码所生成的门级电路,并使用逻辑单元映射结果来证实该电路与图3.4中所示电路相同。

4创建一个矢量波形文件即可指定电路输入输出的.vwf文件。画出输入R、S的输入波形,并使用Quartua II 的仿真器来仿真,观测相应信号如R_g、S_g的波形。通过功能仿真和时序仿真来证实该锁存器正常工作。

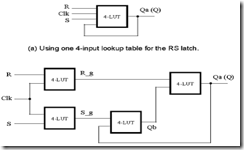

2.)图3.5所示的是一个D锁存器的电路。

图3.5 D锁存器

执行以下步骤:

1创建一个新的Quaryus II工程。使用类似图3.3中的代码来写一个D锁存器的VHDL代码。使用keep指令来使不同逻辑元素分离来观测R_g、S_g、Qa和Qb。

2编译代码,使用技术观测器来检测电路。

3通过功能仿真和时序仿真来证实该锁存器正常工作。

4新建一个工程,用来在DE2-115开发板上实现D锁存器。这个工程应该包含一个具有合适输入输出端口的顶层文件。例如,使用开关SW0与D连接,SW1与CLK连接,而输出Q连接至LEDR0。

5重新编译工程并下载至DE2-115上。

6通过拨动开关改变D和CLK的值并观察LED的变化来测试电路功能。

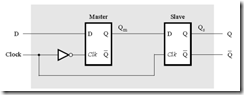

3)图3.6所示的是一个主从D触发器的电路图。

图3.6主从触发的D触发器

执行以下步骤:

1新建一个Quartus II 工程,新建一个VHDL文件,使用两个第二部分中D锁存器来构建主从触发器。

2分配合适的输入输出,如使用开关SW0与D连接,SW1与CLK连接,而输出Q连接至LEDR0。

3编译工程。

4使用技术观测器来测试该电路的功能,并进行仿真来验证。

5将其下载至DE2-115中,通过拨动开关改变D和CLK的值并观察LED的变化来测试电路功能。

浙公网安备 33010602011771号

浙公网安备 33010602011771号