【原创】Quartus II 实验流程说明书

[原创]Quartus II 实验流程说明书

Abstract

本说明书详细介绍了如何使用Quartus II进行建立工程、HDL文件输入、编译、仿真、引脚锁定、配置FPGA等实验流程。并且就学生在实验过程中的一些常见问题给出详细的解决方法。

1 建立工程

(1)首先打开 Quartus II 开发平台(笔者此处使用的是 Quartus II 9.1 版本),如图1-1所示。

图1-1 Quartus II 窗口

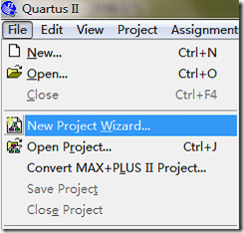

(2)新建工程,点击File,在弹出菜单中选择 New Project Wizard…,如图1-2所示。

图1-2 新建工程

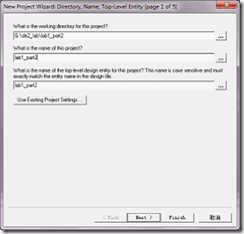

(3)随后弹出新建工程引导窗口,如图1-3所示。根据提示填写工程目录(工程目录路径中不能包含中文,不能建立在桌面上)和工程名(以英文字母开头),第三栏默认与工程名相同即可。随后点击NEXT。

(4)随后进入添加文件窗口,如图1-4所示。在此处可将已经编写好的文件添加入新建的工程中,也可以略过,在工程建立好以后另行添加。添加完毕后点击NEXT。

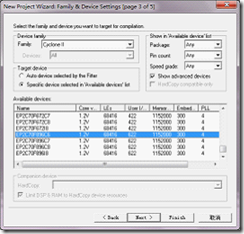

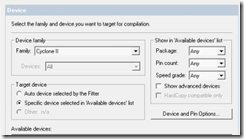

(5)在如图1-5所示的器件选择窗口中,选择与开发板上芯片型号对应的器件。选择完毕后点击NEXT。

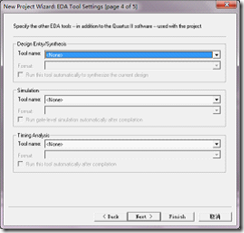

(6)进入第三方EDA工具选择窗口,如图1-6所示,在此可以选择使用第三方的EDA工具,如一些布局布线、综合、仿真软件。实验中我们使用Quartus II软件自带的综合、仿真软件,故略过该步骤点击NEXT。

(7)如图1-7所示,这是工程概况窗口,在此处可以查看刚刚新建工程的一些基本信息。随后点击完成按钮,完成工程的创建。

图1-3 新建工程引导窗口 图1-4 添加文件窗口

图1-5 器件选择窗口 图1-6 EDA工具选择窗口

图1-7 工程概况窗口

2 编译工程

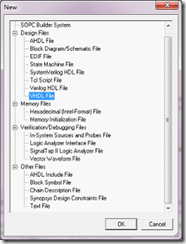

(1)首先 编写HDL文件,点击FILE--NEW选择VHDL File如图2-1所示。或将已有HDL文件加入工程(此步骤可在新建工程时完成)。

(2)设置顶层文件,在Quartus II 软件窗口的左上方的project navigator 窗口中点击File选项卡,如图2-1所示。在此进行设置顶层文件。

(3)对需要设置的文件点击右键,选择set as top-level entity,如图2-3所示。

图2-1 新建 VHDL文件 图2-2 project navigator file 窗口

图2-3 设置顶层文件

图2-4 Quartus II 工具栏

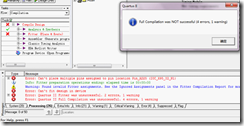

(4)编译工程,在Quartus II 的工具栏(如图2-4所示)选择紫色箭头即编译快捷键,进行编译。编译结束后,即可看到如图2-5所示的编译成功界面。

3 仿真

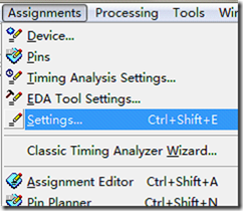

(1)首先使用功能仿真来检查电路逻辑是否正确。在Assignment中选择 settings…,如图3-1所示。

图3-1 settings

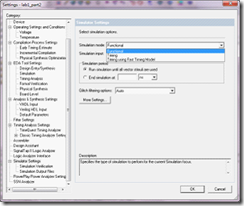

(2)在弹出的settings窗口中,在左侧选择simulation settings,在simulation mode中选择Functional模式,如图3-2所示。点击确定返回。

图3-2 simulation settings窗口 图3-3 新建窗口

(3)新建仿真波形文件,点击NEW,选择新建Vector Waveform File,如图3-3所示。

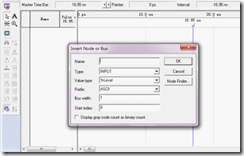

(4)在弹出窗口的左面空白区域双击鼠标左键,弹出Insert node or bus 窗口,如图3-4所示。

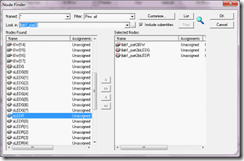

(5)点击Insert node or bus 窗口中的Node finder 按钮,弹出Node finder 窗口,如图3-5所示。

(6)点击Node finder 窗口中的List按钮,会弹出列有所有信号的窗口,如图3-6所示。在该窗口中选出所需观察的信号和需要添加激励的信号。双击信号名,或者点击“》》”按钮。随后点击确定返回。

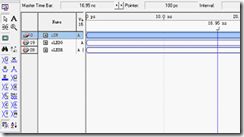

(7)随后便可以对信号添加激励,如图3-7所示。可以按照电路功能特点添加适当激励,以便检查电路功能是否正确。

(8)在编辑完后保存波形文件,如图3-8所示。注意若一个工程中存在多个波形激励文件,需要在设置中指定当前仿真所用的波形文件,如图3-9所示。

图3-4 Insert node or bus

图3-5 Node finder窗口

图3-6 信号列表窗口

图3-7 添加激励信号

图3-8 保存波形文件

图3-9 指定当前仿真所用波形激励文件

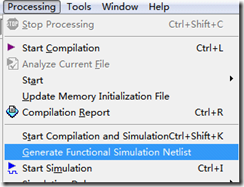

(9)以上准备就绪后,点击Processing 选择 Generate Functional Simulation Netlist 生成仿真网表,如图3-10所示。

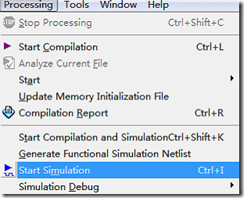

(10)随后点击 Start simulation 进行功能仿真,如图3-11所示。

图3-10 生成仿真网表

图3-11 开始功能仿真

4 引脚锁定

引脚锁定即是告知综合器,所生成的电路的输入输出应该与CPLD/FPGA芯片的哪个引脚相连接。

引脚锁定的方式有手动锁定和自动锁定两种,由于当工程中引脚数量众多时,使用手动锁定十分繁琐,故推荐学习使用自动锁定的方法。

自动引脚锁定有三种方法,限于篇幅在此不一一介绍,下面重点介绍的是导入CSV文件的方式进行引脚锁定。

(1)首先点击Assignments 选择Pins,打开pin planner界面,如图4-1所示。

(2)若使用手动锁定,则在此将窗口左侧的信号拖动至右侧芯片响应引脚上即可,或者在窗口下方双击信号的location栏来选择响应引脚进行锁定。

(3)点击Assignments 选择 Import Assignments…选项(如图4-2所示)将CSV文件导入,完成引脚锁定。 重新打开pin planner界面(如图4-3)可以看到所有引脚已经被锁定好了。

图4-1 pin planner界面

图4-2 选择 Import Assignments…选项

(4)引脚锁定完成后,需要重新进行全编译。点击编译。可能会出现类似如下错误提示:

Error: Can't place multiple pins assigned to pin location Pin_AD25 (IOC_X95_Y2_N1)

如图4-4所示。 此时需要点击Assignments打开device窗口,如图4-5所示。点击device and pin options 如图4-6所示。在弹出的窗口中选择Dual-purpose pins选项卡。将nCEO设置为普通IO口,如图4-7所示。

(5)重新编译无误后,即可下载配置FPGA了。

图4-3 引脚锁定完成

图 4-4 可能出现的错误

图4-5 打开device窗口

图4-6 点击device and pin options按钮

图4-7 Dual-purpose pins窗口

5下载配置

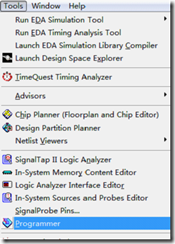

(1)点击Tools 选择 programmer 打开下载器界面,如图5-1,5-2所示。

图5-1 选择tools programmer

图 5-2 下载器界面

(2)选择hardware setup 进行硬件连接,如图5-3所示。

(3)点击Start 进行下载。

浙公网安备 33010602011771号

浙公网安备 33010602011771号