02dc_综合文件讲解

📚 Design Compiler (DC) 综合环境配置与实战指南

📋 目录

🔍 1. DC综合概述

Design Compiler (DC) 是Synopsys公司开发的业界标准RTL综合工具,它将RTL(Register Transfer Level)代码转换为门级网表。DC综合的核心任务是在满足时序、面积、功耗等设计约束的前提下,将高级硬件描述语言(如Verilog/VHDL)转换为具体工艺库中的标准单元组合。

🎯 1.1 DC综合的主要功能

DC综合工具在数字IC设计流程中扮演着至关重要的角色,其主要功能可以归纳为以下几个方面:

-

🔄 逻辑综合: 将RTL代码转换为逻辑门网表

- 自动推断寄存器、锁存器和组合逻辑

- 执行逻辑优化,消除冗余逻辑

- 支持复杂的控制结构和数据路径

-

🎯 工艺映射: 将逻辑门映射到具体工艺库的标准单元

- 根据时序约束选择合适的标准单元

- 平衡速度、功耗和面积之间的关系

- 支持多阈值电压和多驱动强度的单元选择

-

⏰ 时序优化: 满足设计的时序约束要求

- 建立时间(Setup Time)和保持时间(Hold Time)检查

- 关键路径优化和时序修复

- 时钟偏斜(Clock Skew)分析和优化

-

📊 面积优化: 在满足性能要求下最小化芯片面积

- 资源共享和逻辑共享

- 不使用的逻辑移除

- 层次化设计的扁平化优化

📁 1.2 DC综合的输入输出文件

DC综合过程涉及多种文件类型,理解这些文件的作用对于成功的综合至关重要:

📥 输入文件:

-

🔤 RTL代码(.v/.vhd): 设计的源代码文件

- Verilog/SystemVerilog文件

- VHDL文件

- 包含设计的功能描述和结构信息

-

📚 工艺库(.db): 标准单元库文件

- 包含单元的时序、功耗、面积信息

- 支持多个工艺角(Process Corner)

- 通常包括fast、typical、slow三种工艺条件

-

⏱️ 约束文件(.sdc): 时序和面积约束

- 时钟定义和时钟域约束

- 输入输出延迟约束

- 面积和功耗约束

📤 输出文件:

-

🔗 门级网表(.v): 综合后的门级描述

- 包含标准单元实例化

- 保持原始设计的功能等价性

- 适用于后端Place & Route工具

-

⏰ 时序信息(.sdf): 标准延迟格式文件

- 包含每个单元和连线的延迟信息

- 用于后仿真的时序验证

- 支持最小、典型、最大延迟值

-

💾 综合数据库(.ddc): DC专用数据库格式

- 包含完整的设计信息和约束

- 支持增量综合和设计重用

- 可用于后续的形式化验证

🏗️ 1.3 DC综合在IC设计流程中的位置

DC综合处于RTL设计和物理实现之间的关键环节,它将抽象的硬件描述转换为可以进行物理实现的门级网表,为后续的布局布线奠定基础。

⚙️ 2. 环境配置文件详解

🗂️ 2.1 .synopsys_dc.setup 文件简介

.synopsys_dc.setup 是DC的默认环境配置文件,这是一个隐藏文件,DC启动时会自动搜索并执行该文件。该文件的主要作用是配置DC工作所需的各种环境变量和库路径。

💡 小贴士: 该文件必须放置在DC启动目录或用户主目录下,文件名前的"."使其成为隐藏文件。

🔧 2.2 核心配置变量详解

DC环境配置主要涉及以下五个关键变量,这些变量构成了DC工作的基础环境:

🔍 2.2.1 search_path (搜索路径)

set search_path "$search_path mapped rtl libs cons"

- 🎯 作用: 定义DC搜索文件的路径顺序

- 📝 说明: DC会按照路径顺序查找RTL文件、库文件和脚本文件

- ⭐ 最佳实践: 将最常用的路径放在前面,提高搜索效率

- 🚨 注意事项:

- 路径中不要包含空格或特殊字符

- 使用绝对路径可以避免相对路径引起的问题

- "." 表示当前目录,应该始终包含在搜索路径中

🎯 2.2.2 target_library (目标工艺库)

set target_library "22nm.db"

- 🎯 作用: 指定综合时使用的主要工艺库文件

- 📝 说明: 这是DC进行逻辑到门级映射的基础库,通常选择worst-case (慢速)库

- ⚠️ 注意: 如果未设置会报错

Error: Could not read the following target libraries - 🔍 详细说明:

- 通常使用slow corner库进行综合,确保设计在最坏情况下也能满足时序要求

- 支持多库设置,用于多电压域设计

- 库的选择直接影响综合结果的质量和性能

🔗 2.2.3 link_library (链接库)

set link_library "* $target_library"

- 🎯 作用: 定义DC链接时可用的所有库文件

- 📝 说明:

*表示DC在内存中的所有已加载库- 包含target_library和其他IP库、宏单元库

- 用于解析设计中的所有单元引用

- 🔍 扩展配置:

set link_library "* $target_library dw_foundation.sldb memory_compiler.db"

🎨 2.2.4 symbol_library (符号库)

set symbol_library "22nm.sdb"

- 🎯 作用: 为Design Vision GUI提供图形化符号显示

- 📝 说明: .sdb文件包含标准单元的图形化表示

- 🖥️ GUI功能:

- 提供原理图级别的可视化

- 支持层次化设计浏览

- 便于调试和分析综合结果

⚡ 2.2.5 synthetic_library (综合库)

set synthetic_library "dw_foundation.sldb standard.sldb"

- 🎯 作用: 提供DesignWare IP组件库

- 📝 说明: 包含算术运算器、存储器等可综合IP模块

- 🧩 包含组件:

- 加法器、乘法器、除法器

- 比较器、编码器、解码器

- FIFO、RAM等存储器接口

- 数字信号处理(DSP)组件

📄 2.3 文件格式说明

📚 2.3.1 库文件格式对比

| 格式 | 描述 | 优点 | 缺点 | 用途 |

|---|---|---|---|---|

| 📖 .lib文件 | 人类可读的ASCII格式 | ✅ 可编辑 ✅ 易于调试 |

❌ 文件较大 ❌ 读取较慢 |

库开发和调试 |

| 💾 .db文件 | 二进制格式,DC专用 | ✅ 读取快速 ✅ 文件紧凑 |

❌ 不可编辑 ❌ 工具依赖 |

生产环境综合 |

🔄 转换方法: 使用Library Compiler将.lib文件转换为.db文件

lc_shell

read_lib your_library.lib

write_lib your_library -format db -output your_library.db

📥 2.3.2 设计文件读取策略

DC支持多种文件读取方式,选择合适的方式可以提高工作效率:

# 📝 方法1: 逐个读取文件 (适用于小型设计)

read_verilog top.v

read_verilog sub_module.v

# 📦 方法2: 批量读取(第一个文件作为顶层)

read_verilog {top.v sub_module.v}

# 🔬 方法3: 分析并详细配置 (推荐用于复杂设计)

analyze -format verilog {module_a.v module_b.v top.v}

elaborate TOP -parameters "WIDTH=8"

# 📋 方法4: 使用文件列表 (大型项目推荐)

analyze -format verilog -f design_files.list

elaborate TOP

🛡️ 2.4 安全配置建议

✅ 2.4.1 使用 set_app_var 命令的优势

# ✅ 推荐使用 set_app_var (更安全)

set_app_var target_library "slow.db"

# ❌ 避免使用 set (容易出错)

set target_library "slow.db"

🔒 set_app_var 的优势:

- 🔍 变量名检查: 如果变量名拼写错误会立即报错

- 🎯 类型检查: 确保赋值类型正确

- 🐛 更好的调试信息: 提供更详细的错误提示

- 📋 版本兼容性: 在不同DC版本间保持更好的兼容性

🗂️ 2.4.2 路径设置最佳实践

# 📁 使用变量提高可维护性

set PROJECT_ROOT "/home/user/my_project"

set RTL_PATH "${PROJECT_ROOT}/rtl"

set LIB_PATH "${PROJECT_ROOT}/libs"

# 🔄 动态路径获取(更灵活,推荐用于团队协作)

set SCRIPT_DIR [file dirname [file normalize [info script]]]

set PROJECT_ROOT [file dirname $SCRIPT_DIR]

# 🛡️ 路径验证和错误处理

if {![file exists $LIB_PATH]} {

puts "❌ Error: Library path $LIB_PATH does not exist!"

exit 1

}

📋 路径配置检查清单:

- 软件实际操作

- 首先创建以下目录

- syn 用来进行dc综合的文件夹

- rtl 用来保存rlt代码的文件夹

- sim 用来进行前仿的文件夹

- pt 用来进行静态时序检查的文件夹

- fm 用来进行形式化验证的文件夹

- doc 用来放置一些文档的文件夹

- 然后来到syn文件夹中创建一下的文件夹

- reports 放置后面产生的报告的文件夹 包括timing area等

- scripts 放置脚本文件的文件夹

- mapped 放置之后完成映射后的文件的文件夹

- unmapped 放置还没有完成映射但是已经可以进行保存的中间的文件 用来之后继续进行的文件夹

- rtl 放置rtl代码的文件夹

- work 进行工作的文件夹

- Makefile 放置makefile文件的文件夹

- config 项目设置所需要的文件夹

- 首先创建以下目录

- 前提准备

- pdk文件

- 使用的是tsmc90nm工艺库

- rtl代码

- 见附录

- .synopsys_dc.setup设置

- pdk文件

💼 3. .synopsys_dc.setup 配置实例

🏗️ 3.1 完整配置文件示例

以下是一个生产级的.synopsys_dc.setup配置文件,包含详细的注释和最佳实践。该配置文件经过实际项目验证,具有良好的可移植性和健壮性:

###############################################################################

# 🔧 Synopsys Design Compiler (DC) Setup Script

#

# Purpose: Configures environment variables and library paths for RTL synthesis.

# This script is automatically sourced by dc_shell/design_vision

# if named ".synopsys_dc.setup" and placed in the launch directory.

#

# Usage: Place this file as .synopsys_dc.setup in the project's root

# or synthesis launch directory.

#

# Rev: 3.0 (Enhanced with symbols and extended features)

# Author: IC Design Team

# Date: 2025-07-12

###############################################################################

# ===================== 🏗️ PROJECT ENVIRONMENT SETTINGS =====================

puts "🚀 Initializing Design Compiler Environment..."

# 🔄 动态获取项目根路径(推荐方式,提高可移植性)

set SCRIPT_DIR [file dirname [file normalize [info script]]]

set SYN_ROOT_PATH [file dirname $SCRIPT_DIR]

# 🔒 如果需要固定路径,可以使用以下方式:

# set SYN_ROOT_PATH "/usr/pro/IC_prjs/lab1"

# 📁 定义项目目录结构

set RTL_PATH "${SYN_ROOT_PATH}/syn/rtl/basic"

set CONFIG_PATH "${SYN_ROOT_PATH}/syn/config"

set SCRIPT_PATH "${SYN_ROOT_PATH}/syn/scripts"

set UNMAPPED_PATH "${SYN_ROOT_PATH}/syn/unmapped"

set MAPPED_PATH "${SYN_ROOT_PATH}/syn/mapped"

set REPORT_PATH "${SYN_ROOT_PATH}/syn/reports"

set WORK_PATH "${SYN_ROOT_PATH}/syn/work"

# ===================== 🛠️ TOOL INSTALLATION PATHS =====================

# Design Compiler安装路径(根据实际安装路径修改)

set DC_PATH "/usr/synopsys/syn/W-2024.09-SP1"

# 验证DC安装路径

if {![file exists $DC_PATH]} {

puts "⚠️ Warning: DC installation path $DC_PATH not found!"

puts " Please update DC_PATH variable in .synopsys_dc.setup"

}

# ===================== 📚 TECHNOLOGY LIBRARY PATHS =====================

# 工艺库路径配置(需要根据实际PDK路径修改)

set PDK_ROOT "/usr/pro/pdks/TSMC90"

set LIB_PATH "${PDK_ROOT}/aci/sc-x/synopsys"

set SYMBOL_PATH "${PDK_ROOT}/aci/sc-x/symbols/synopsys"

# 📋 验证关键路径存在性

foreach path_var {PDK_ROOT LIB_PATH SYMBOL_PATH} {

if {![file exists [set $path_var]]} {

puts "❌ Error: Path [set $path_var] does not exist!"

puts " Please check your PDK installation and update paths."

}

}

# ===================== ⚙️ DESIGN COMPILER CONFIGURATION =====================

# 🔍 检查并创建工作目录

if {![file exists $WORK_PATH]} {

puts "📁 Creating work directory: $WORK_PATH"

file mkdir $WORK_PATH

puts "✅ Work directory created successfully."

}

# 💾 定义工作库

define_design_lib WORK -path $WORK_PATH

# 🔍 配置搜索路径(按优先级排序)

set_app_var search_path [list \

. \

$search_path \

$RTL_PATH \

$LIB_PATH \

$SCRIPT_PATH \

$SYMBOL_PATH \

$CONFIG_PATH \

$DC_PATH/libraries/syn \

]

# ⚡ 配置综合库(DesignWare IP库)

set_app_var synthetic_library [list \

dw_foundation.sldb \

standard.sldb \

]

# 🎯 配置目标工艺库(通常使用worst-case库进行综合)

set_app_var target_library [list \

slow.db \

]

# 🔗 配置链接库(包含所有需要的库)

set_app_var link_library [list \

* \

${target_library} \

${synthetic_library} \

]

# 🎨 配置符号库(用于GUI显示)

set_app_var symbol_library [list \

tsmc090.sdb \

]

# ===================== 🔧 可选配置 =====================

# 📋 导入命名规则(如果存在)

set NAME_RULES_FILE "${CONFIG_PATH}/hs_name_rules.tcl"

if {[file exists $NAME_RULES_FILE]} {

puts "📜 Sourcing naming rules from $NAME_RULES_FILE"

source $NAME_RULES_FILE

puts "✅ Naming rules loaded successfully."

} else {

puts "⚠️ Warning: Naming rules file not found: $NAME_RULES_FILE"

puts " Consider creating naming rules for better netlist quality."

}

# ⚡ 设置默认的优化策略

set_app_var compile_ultra_ungroup_dw true

set_app_var hdlin_auto_save_templates true

set_app_var hdlin_check_no_latch true

# 🔧 其他有用的配置选项

set_app_var hdlin_translate_off_skip_text true

set_app_var verilogout_no_tri true

set_app_var verilogout_show_unconnected_pins true

# ===================== 🎉 初始化完成提示 =====================

puts "╔════════════════════════════════════════════════════════════╗"

puts "║ 🎉 Design Compiler Environment Initialized ║"

puts "╠════════════════════════════════════════════════════════════╣"

puts "║ 📂 Project Root: $SYN_ROOT_PATH"

puts "║ 💼 Working Directory: $WORK_PATH"

puts "║ 🎯 Target Library: [get_app_var target_library]"

puts "║ 🔍 Search Paths: [llength [get_app_var search_path]] paths configured"

puts "╠════════════════════════════════════════════════════════════╣"

puts "║ 💡 Tips:"

puts "║ • Use 'list_libs' to verify library loading"

puts "║ • Use 'report_lib [get_app_var target_library]' for lib info"

puts "║ • Use 'start_gui' to launch Design Vision"

puts "╚════════════════════════════════════════════════════════════╝"

🔧 3.2 配置文件关键特性说明

📁 3.2.1 智能路径管理策略

# 🔄 使用变量管理路径,提高可维护性

set RTL_PATH "${SYN_ROOT_PATH}/syn/rtl/basic"

set CONFIG_PATH "${SYN_ROOT_PATH}/syn/config"

# 🔍 路径验证机制

foreach check_path {RTL_PATH CONFIG_PATH SCRIPT_PATH} {

if {![file exists [set $check_path]]} {

puts "⚠️ Warning: Directory [set $check_path] does not exist!"

puts " Creating directory: [set $check_path]"

file mkdir [set $check_path]

}

}

- ✨ 优势: 统一路径管理,便于项目迁移

- 🔄 灵活性: 通过修改

SYN_ROOT_PATH即可适配不同环境 - 🛡️ 健壮性: 自动创建缺失的目录

🛡️ 3.2.2 安全性检查与错误处理

# 🔍 检查工作目录是否存在

if {![file exists $WORK_PATH]} {

puts "📁 Creating work directory: $WORK_PATH"

file mkdir $WORK_PATH

puts "✅ Work directory created successfully."

}

# 📚 验证库文件存在性

if {![file exists "${LIB_PATH}/slow.db"]} {

puts "❌ Critical Error: Target library slow.db not found!"

puts " Expected location: ${LIB_PATH}/slow.db"

puts " Please check your PDK installation."

exit 1

}

- 🎯 作用: 避免因缺失目录或文件导致的启动失败

- 🛡️ 健壮性: 提高脚本的错误容忍能力

- 🐛 调试: 提供清晰的错误信息和解决建议

🔧 3.2.3 条件加载与模块化配置

# 📋 有条件地加载可选配置文件

if {[file exists $NAME_RULES_FILE]} {

puts "📜 Loading naming rules..."

source $NAME_RULES_FILE

puts "✅ Naming rules applied successfully."

} else {

puts "ℹ️ Info: No custom naming rules found, using default."

}

# 🎛️ 根据项目类型加载不同配置

set PROJECT_TYPE [get_unix_variable "PROJECT_TYPE"]

if {$PROJECT_TYPE == "low_power"} {

source "${CONFIG_PATH}/low_power_settings.tcl"

puts "⚡ Low power optimization settings loaded."

}

- 🔧 灵活性: 支持可选组件的灵活配置

- 🔄 兼容性: 在不同项目间保持配置的通用性

- 📋 模块化: 将不同功能的配置分离到独立文件

📊 3.2.4 环境信息报告

# 📈 生成详细的环境配置报告

proc generate_env_report {} {

puts "\n📊 === Environment Configuration Report ==="

puts "🕐 Generated at: [clock format [clock seconds]]"

puts "\n📚 Library Configuration:"

puts " Target Library: [get_app_var target_library]"

puts " Link Library: [get_app_var link_library]"

puts " Symbol Library: [get_app_var symbol_library]"

puts "\n📁 Path Configuration:"

puts " Search Paths: [get_app_var search_path]"

puts "\n⚙️ Tool Settings:"

puts " DC Version: [get_app_var sh_product_version]"

puts " Host: [get_unix_variable HOSTNAME]"

puts " User: [get_unix_variable USER]"

puts "════════════════════════════════════════\n"

}

# 调用报告生成函数

generate_env_report

📁 4. 项目目录结构规范

🏗️ 4.1 标准目录结构

一个规范的数字IC设计项目应该具有清晰的目录层次结构。良好的目录组织不仅有助于项目管理,还能提高团队协作效率:

🏠 project_root/

├── 🔧 syn/ # 综合相关文件

│ ├── 💼 work/ # DC工作目录 (临时文件和数据库)

│ ├── 📜 scripts/ # 综合脚本 (TCL, SDC等)

│ ├── 📝 rtl/ # RTL源代码 (Verilog/VHDL)

│ ├── ✅ mapped/ # 综合后的网表

│ ├── 🔄 unmapped/ # 中间文件 (分析但未映射)

│ ├── 📊 reports/ # 综合报告 (时序、面积、功耗)

│ ├── ⚙️ config/ # 配置文件 (约束、规则)

│ └── 🛠️ Makefile # 自动化构建脚本

├── ⏰ pt/ # PrimeTime静态时序分析

├── ✔️ fm/ # 形式化验证 (Formality)

├── 🎮 sim/ # 仿真文件 (前仿、后仿)

├── 📝 rtl/ # 项目级RTL代码 (共享模块)

└── 📚 doc/ # 项目文档 (规格、设计文档)

🛠️ 4.2 目录创建命令

📋 4.2.1 自动化目录创建脚本

#!/bin/bash

# 🚀 IC项目目录结构创建脚本

echo "🏗️ Creating IC design project structure..."

# 📁 创建主要目录

mkdir -p syn pt fm rtl sim doc

echo "✅ Main directories created."

# 🔧 创建综合子目录

cd syn

mkdir -p work scripts rtl mapped unmapped reports config

echo "✅ Synthesis subdirectories created."

# 📊 创建报告子目录

cd reports

mkdir -p timing area power qor constraint

echo "✅ Report subdirectories created."

cd ../..

# 🎮 创建仿真子目录

cd sim

mkdir -p pre_syn post_syn testbench waveforms

echo "✅ Simulation subdirectories created."

cd ..

# 📚 创建文档目录

cd doc

mkdir -p specs design_docs user_guides

echo "🎉 Project structure created successfully!"

tree .

🏃♂️ 4.2.2 快速创建命令

# 🚀 一行命令创建完整目录结构

mkdir -p {syn/{work,scripts,rtl,mapped,unmapped,reports/{timing,area,power,qor,constraint},config},pt,fm,sim/{pre_syn,post_syn,testbench,waveforms},rtl,doc/{specs,design_docs,user_guides}}

📋 4.3 各目录功能详解

| 目录 | 🎯 功能描述 | 📄 关键文件类型 | 📊 典型大小 | 🔄 更新频率 |

|---|---|---|---|---|

syn/work |

DC工作目录,存储临时和中间文件 | .svf, .ddc, .syn |

100MB-1GB | 每次综合 |

syn/scripts |

综合脚本和约束文件 | .tcl, .sdc, .upf |

1-10MB | 设计阶段 |

syn/rtl |

综合专用的RTL代码 | .v, .sv, .vhd |

10-100MB | 开发阶段 |

syn/mapped |

综合后的门级网表 | _net.v, .ddc, .sdf |

50-500MB | 每次综合 |

syn/unmapped |

分析后但未映射的中间文件 | .ddc, .db |

10-50MB | 增量综合 |

syn/reports |

综合报告文件 | .rpt, .log, .html |

1-50MB | 每次综合 |

syn/config |

配置文件和约束规则 | .tcl, .sdc, .rules |

1-5MB | 项目初期 |

📄 4.4 文件命名规范建议

🏷️ 4.4.1 网表文件命名规范

# 📝 基本命名模式

${TOP_MODULE}_${CORNER}_${VERSION}.${EXTENSION}

# 🎯 具体示例

cpu_core_slow_v1.0_net.v # 综合后的Verilog网表

cpu_core_fast_v1.0_mapped.ddc # 综合后的DDC数据库

cpu_core_typical_v1.0_unmapped.ddc # 综合前的DDC数据库

cpu_core_slow_v1.0.sdf # 时序信息文件

# 📊 报告文件命名

${TOP_MODULE}_${ANALYSIS_TYPE}_${DATE}.rpt

cpu_core_area_20250712.rpt # 面积报告

cpu_core_timing_20250712.rpt # 时序报告

cpu_core_power_20250712.rpt # 功耗报告

cpu_core_constraint_20250712.rpt # 约束报告

📋 4.4.2 脚本文件命名规范

# 🔧 综合脚本命名

run_synthesis.tcl # 主综合脚本

setup_environment.tcl # 环境配置脚本

apply_constraints.tcl # 约束应用脚本

generate_reports.tcl # 报告生成脚本

# ⏰ 约束文件命名

${TOP_MODULE}_timing.sdc # 时序约束

${TOP_MODULE}_physical.sdc # 物理约束

${TOP_MODULE}_power.upf # 功耗约束

${TOP_MODULE}_io.sdc # IO约束

🔧 4.5 命名规则配置文件

hs_name_rules.tcl 文件定义了综合过程中的命名规则,确保生成的网表符合后端工具的要求:

# 📚 Verilog保留字定义

set verilog_reserved {"always" "always_comb" "and" "assign" "automatic"

"begin" "buf" "bufif0" "bufif1" "case" "casex" "casez" "cell" "cmos" "config"

"deassign" "default" "defparam" "design" "disable" "edge" "else" "end" "endcase"

"endconfig" "endfunction" "endgenerate" "endmodule" "endprimitive" "endspecify"

"endtable" "endtask" "event" "for" "force" "forever" "fork" "function"

"generate" "genvar" "highz0" "highz1" "if" "ifnone" "incdir" "include" "initial"

"inout" "input" "instance" "integer" "join" "large" "liblist" "library"

"localparam" "macromodule" "medium" "module" "nand" "negedge" "nmos" "nor"

"noshowcancelled" "not" "notif0" "notif1" "or" "output" "parameter" "pmos"

"posedge" "primitive" "pull0" "pull1" "pulldown" "pullup" "pulsestyle_onevent"

"pulsestyle_ondetect" "rcmos" "real" "realtime" "reg" "release" "repeat" "rnmos"

"rpmos" "rtran" "rtranif0" "rtranif1" "scalared" "showcancelled" "signed"

"small" "specify" "specparam" "strong0" "strong1" "supply0" "supply1" "table"

"task" "time" "tran" "tranif0" "tranif1" "tri" "tri0" "tri1" "triand" "trior"

"trireg" "unsigned" "use" "vectored" "wait" "wand" "weak0" "weak1" "while"

"wire" "wor" "xnor" "xor"}

# 🏷️ 定义不同阶段的保留字

set dft_reserved {} # 🧪 DFT相关保留字

set cot_reserved {} # 🔧 COT相关保留字

set typ_reserved_words [concat $verilog_reserved $cot_reserved]

set frontend_reserved_words [concat $verilog_reserved $cot_reserved $dft_reserved]

set top_reserved_words [concat $verilog_reserved $cot_reserved]

set backend_reserved_words [concat $verilog_reserved $cot_reserved]

# 🎨 总线命名风格配置

set bus_range_separator_style ":" # 总线范围分隔符 [7:0]

set bus_multiple_separator_style "," # 多位总线分隔符

set gen_cell_pin_name_separator "_" # 单元管脚名分隔符

# 📐 定义命名规则集合

define_name_rules hs_simple_rules \

-special verilog \

-first_restrict "0-9" \

-allow "a-z A-Z 0-9 _" \

-target_bus_naming_style {%s[%d]} \

-check_internal_net_name \

-equal_ports_nets -inout_ports_equal_nets \

-dummy_net_prefix "SYN_NC_%d" \

-case_insensitive

define_name_rules hs_backend_rules \

-special verilog \

-max_length 256 \

-first_restrict "0-9" \

-allow "a-z A-Z 0-9 _" \

-target_bus_naming_style {%s[%d]} \

-check_internal_net_name \

-equal_ports_nets -inout_ports_equal_nets \

-dummy_net_prefix "SYN_NC_%d" \

-case_insensitive \

-reserved_words $backend_reserved_words

# 🎯 高级命名规则(用于关键路径)

define_name_rules hs_critical_path_rules \

-special verilog \

-max_length 128 \

-first_restrict "0-9" \

-allow "a-z A-Z 0-9 _" \

-target_bus_naming_style {%s[%d]} \

-prefix_map {{"clk" "CLK"} {"rst" "RST"}} \

-suffix_map {{"_reg" "_REG"} {"_ff" "_FF"}} \

-case_insensitive \

-reserved_words $backend_reserved_words

🎯 命名规则的重要性:

- ✅ 兼容性保证: 确保网表在后端工具中的兼容性

- 🚫 关键字避免: 避免使用Verilog保留字作为信号名

- 🎨 风格统一: 统一总线和端口的命名风格

- 🔧 冲突处理: 自动处理冲突的信号名称

- 📏 长度限制: 控制信号名长度,避免工具限制

📊 4.6 目录管理最佳实践

🧹 4.6.1 目录清理策略

# 🗑️ 清理脚本示例

#!/bin/bash

echo "🧹 Cleaning synthesis directories..."

# 清理工作目录中的临时文件

rm -rf syn/work/*.svf

rm -rf syn/work/*.log

rm -rf syn/work/default.svf

# 清理旧的报告文件(保留最新5份)

find syn/reports -name "*.rpt" -type f -mtime +7 -delete

# 清理备份文件

find . -name "*~" -delete

find . -name "*.bak" -delete

echo "✅ Cleanup completed."

🔄 4.6.2 版本控制配置

# 📝 .gitignore 文件示例

# 🔧 综合工作文件

syn/work/*.svf

syn/work/*.log

syn/work/default.svf

syn/work/filenames.log

# 📊 临时报告文件

syn/reports/*.log

syn/reports/tmp_*

# 💾 备份文件

*.bak

*~

.#*

# 🗂️ 大型二进制文件

*.ddc

*.db

*.sdf

5. DC综合实战操作

5.1 环境准备与启动

5.1.1 项目目录创建

# 1. 创建项目主目录

mkdir -p /usr/pro/IC_prjs/lab1

cd /usr/pro/IC_prjs/lab1

# 2. 创建标准目录结构

mkdir -p syn/{work,scripts,rtl,mapped,unmapped,reports,config}

mkdir -p {pt,fm,rtl,sim,doc}

# 3. 进入工作目录

cd syn/work

5.1.2 配置文件准备

将前面介绍的.synopsys_dc.setup文件放置在syn/work目录下,并根据实际环境修改路径配置。

5.1.3 启动DC

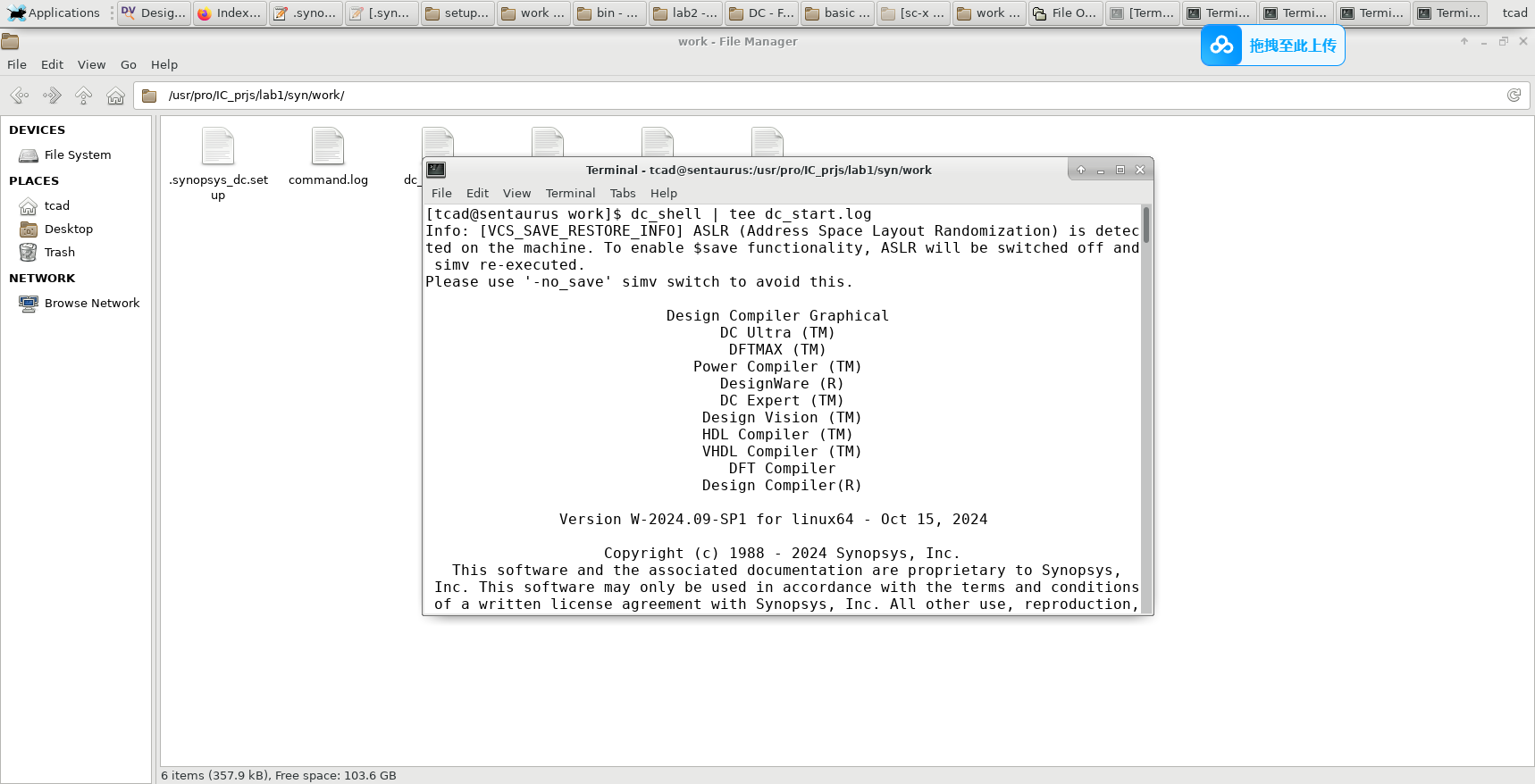

# 启动DC并记录日志

dc_shell | tee dc_start.log

成功启动后,您将看到DC的启动信息和环境配置确认。

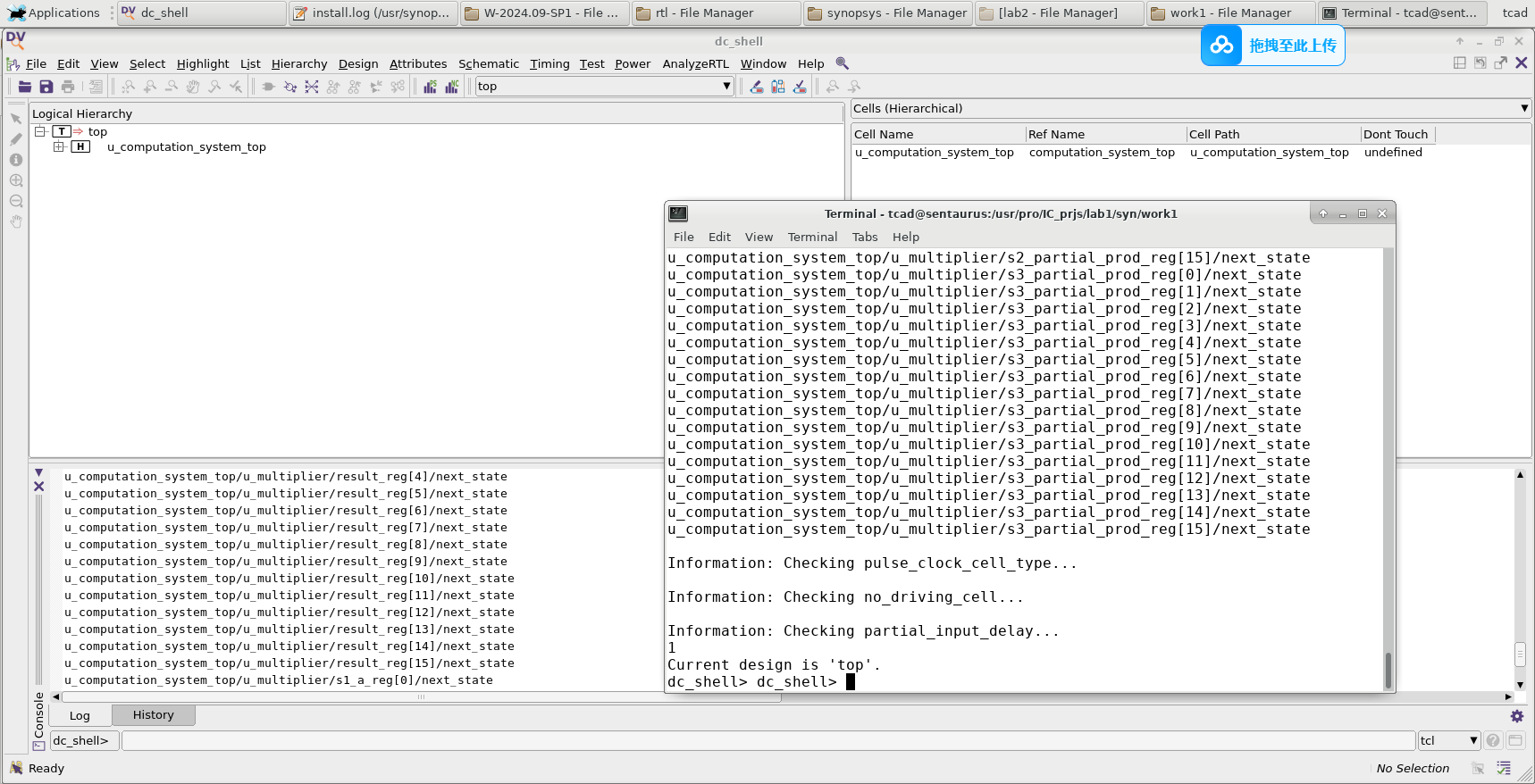

实际操作截图:

- 创建.synopsys_dc.setup文件,然后将配置内容写入该文件,注意工艺库和其他路径相关的内容要根据自己的设置进行修改

- 修改完成之后打开终端输入

dc_shell | tee dc_start.log

5.2 RTL代码读取与分析

5.2.1 基本读取方法

# 方法1: 直接读取单个文件

read_verilog top.v

# 方法2: 批量读取多个文件

read_verilog {top.v sub_module1.v sub_module2.v}

# 方法3: 使用analyze/elaborate流程(推荐)

analyze -format verilog {sub_module1.v sub_module2.v top.v}

elaborate top

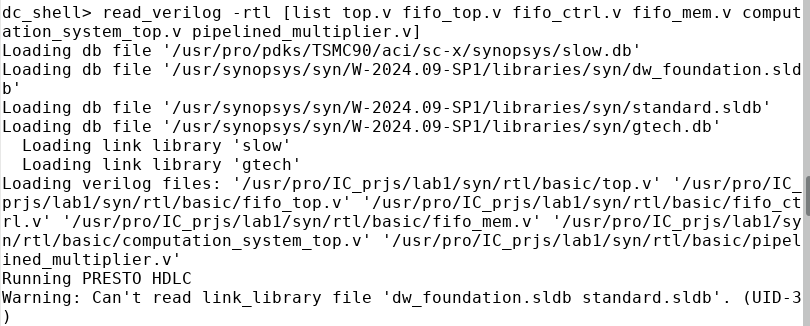

实际操作截图:

- 使用

analyze -format verilog [list ...]来将RTL代码进行读入

5.2.2 多文件读取策略

对于复杂设计,推荐使用文件列表方式:

# 创建文件列表 filelist.f

# top.v

# fifo_ctrl.v

# fifo_mem.v

# computation_system.v

# 使用文件列表读取

analyze -format verilog -f filelist.f

elaborate computation_system_top

5.2.3 设计链接与检查

# 链接设计

link

# 检查设计完整性

check_design

# 生成HTML格式的检查报告

check_design -html ../reports/check_design.html

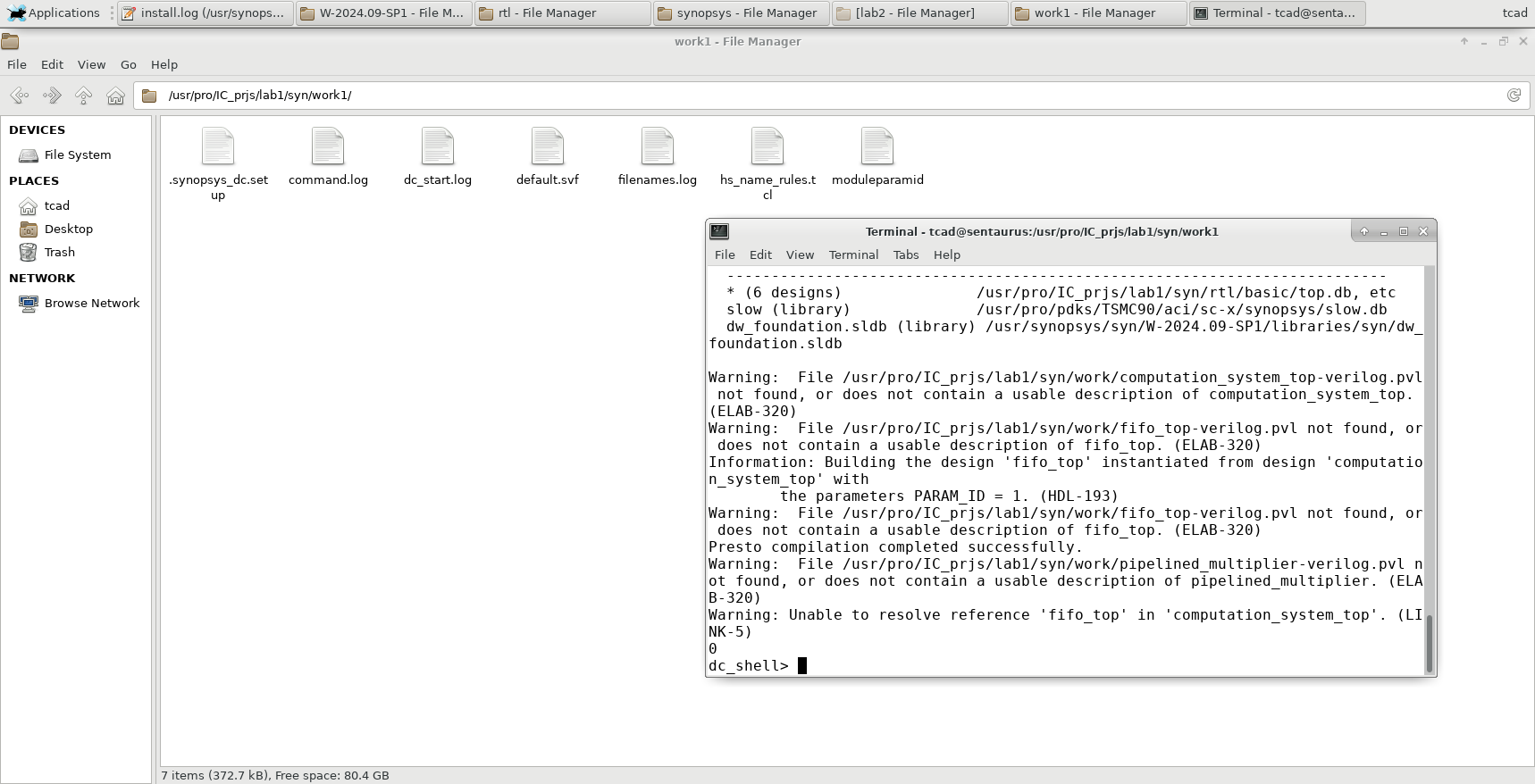

实际操作截图:

- 将RTL代码读入之后,通过使用

link命令来进行链接 - 发现出现错误,按照错误提示对问题进行处理

5.3 约束设置与时序检查

5.3.1 基本约束加载

# 加载SDC约束文件

source ../scripts/design_constraints.sdc

# 或者手动设置基本约束

create_clock -name clk -period 10 [get_ports clk]

set_input_delay -clock clk 2 [all_inputs]

set_output_delay -clock clk 2 [all_outputs]

5.3.2 时序检查

# 检查时序约束覆盖率

check_timing

# 检查约束是否合理

report_constraint -all_violators

实际操作截图:

- 通过使用

check_timing命令来查看是否代码存在问题

5.4 综合执行

5.4.1 综合选项配置

# 设置综合选项

set_app_var compile_ultra_ungroup_dw true

set_app_var hdlin_auto_save_templates true

# 可选: 设置扁平化

# set_flatten true

5.4.2 执行综合

# 执行高级综合

compile_ultra

# 或者使用基本综合

# compile

5.4.3 后处理清理

# 移除未连接的端口

remove_unconnected_ports [find -hierarchy cell "*"]

remove_unconnected_ports -blast_buses [find -hierarchy cell "*"]

# 应用Verilog命名规则

change_names -rule verilog -hier

5.5 结果输出与报告生成

5.5.1 生成综合报告

# 生成各类报告

report_constraint -all_violators > ../reports/violation_report.rpt

report_area > ../reports/area_report.rpt

report_timing > ../reports/timing_report.rpt

report_power > ../reports/power_report.rpt

report_qor > ../reports/qor_report.rpt

report_design > ../reports/design_report.rpt

5.5.2 保存综合结果

# 保存网表文件

write -format verilog -hier -out ../mapped/design_net.v

# 保存DDC数据库

write -format ddc -hier -out ../mapped/design.ddc

# 保存SDC约束

write_sdc ../mapped/design.sdc

# 保存SDF时序信息

write_sdf ../mapped/design.sdf

5.6 GUI界面使用

5.6.1 启动图形界面

# 启动Design Vision GUI

start_gui

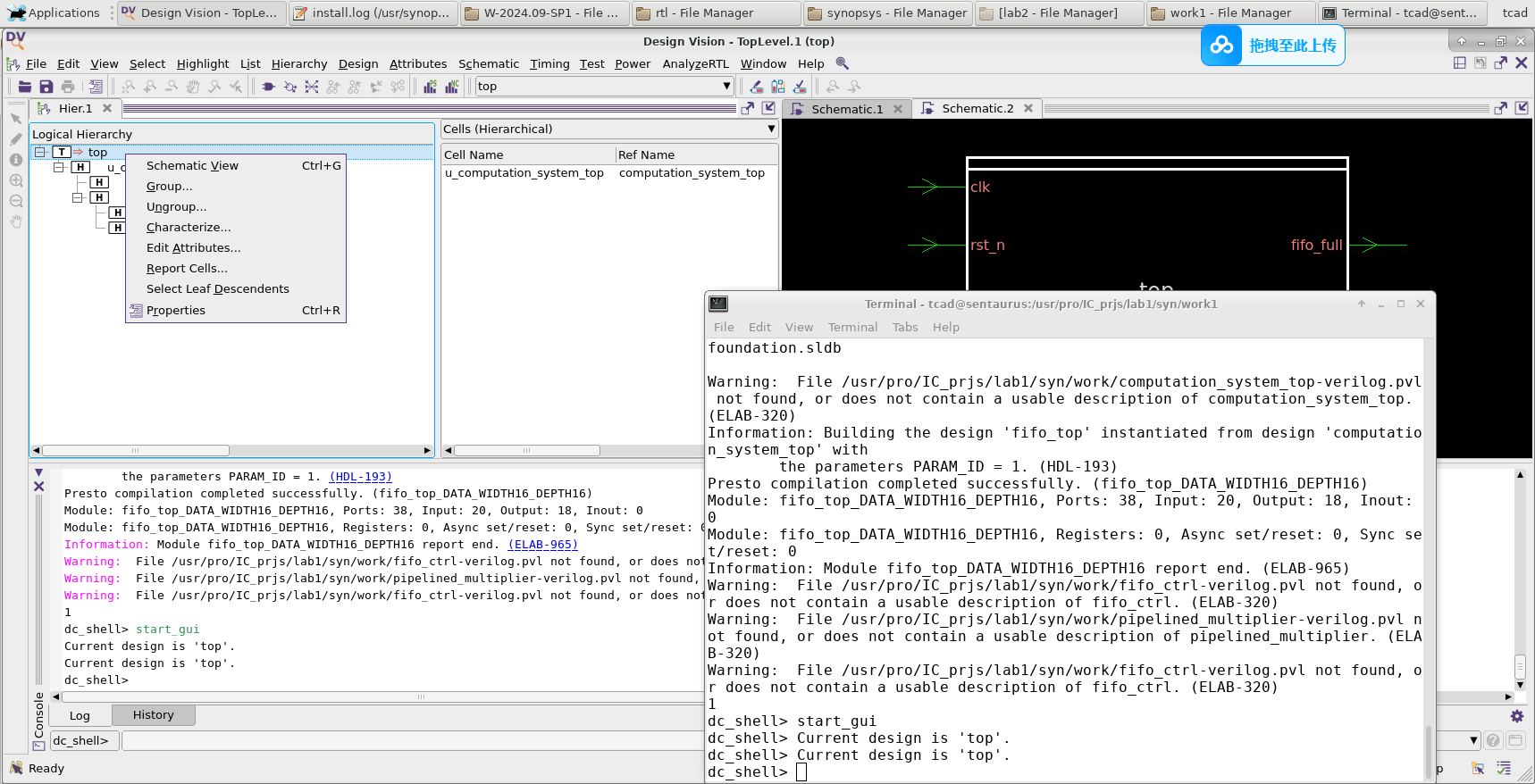

实际操作截图:

- 可以通过使用GUI界面来进行查看,命令是

start_gui

5.6.2 GUI功能特点

- 原理图查看: 可视化设计的层次结构

- 时序路径分析: 图形化显示关键路径

- 面积分析: 各模块的面积占比统计

- 约束管理: 图形化约束设置和验证

6. 常见问题与解决方案

6.1 库相关问题

6.1.1 目标库未找到

错误信息:

Error: Could not read the following target libraries: your_library.db

解决方案:

# 检查库路径设置

echo $LIB_PATH

# 验证库文件是否存在

ls $LIB_PATH/*.db

# 重新设置正确的库路径

set_app_var target_library "correct_path/slow.db"

6.1.2 链接库配置问题

症状: get_app_var显示库配置正确,但list_libs为空

分析: 配置变量已设置,但库文件未实际加载到内存

解决方案:

# 强制重新加载库

set_app_var link_library ""

set_app_var link_library "* slow.db dw_foundation.sldb"

# 验证库加载状态

list_libs

report_lib slow

6.2 RTL语法问题

6.2.1 语法解析错误

错误信息:

Error: Syntax error at or near token ';'. (VER-294)

常见原因:

always块缺少begin...end- 端口连接语法不标准

- 参数使用不当

解决方案:

// 错误写法

always @(posedge clk)

if (rst) a <= 0; b <= 1; // 多语句需要begin...end

// 正确写法

always @(posedge clk) begin

if (rst) begin

a <= 0;

b <= 1;

end

end

6.3 约束相关问题

6.3.1 时序约束不完整

检查命令:

check_timing

常见问题:

- 输入/输出延迟未设置

- 时钟定义缺失

- 异步路径未处理

解决方案:

# 完整的约束示例

create_clock -name clk -period 10 [get_ports clk]

set_input_delay -clock clk 2 [all_inputs]

set_output_delay -clock clk 2 [all_outputs]

set_false_path -from [get_ports rst_n]

6.4 综合质量问题

6.4.1 时序违规处理

检查方法:

report_timing -delay_type max -max_paths 10

report_constraint -all_violators

优化策略:

# 增加面积预算以满足时序

set_max_area 0

# 使用更高级的优化

compile_ultra -gate_clock

# 手动指导关键路径优化

group_path -name critical_path -from input_reg -to output_reg

set_path_group critical_path -weight 10

6.5 调试技巧

6.5.1 逐步验证方法

# 1. 验证环境配置

get_app_var target_library

list_libs

# 2. 验证RTL读取

analyze -format verilog design.v

elaborate top

# 3. 验证链接

link

check_design

# 4. 验证约束

check_timing

report_clock

# 5. 小规模综合测试

compile -map_effort medium

6.5.2 日志分析

# 查看详细错误信息

grep -i error dc_start.log

# 查看警告信息

grep -i warning dc_start.log

# 查看关键进度信息

grep -i "Info:" dc_start.log

🏁 总结

本文详细介绍了Design Compiler的环境配置和使用方法,涵盖了从基础概念到实际操作的完整流程。通过系统性的学习,您已经掌握了DC综合的核心知识和实践技能。

🎯 关键要点回顾

-

⚙️ 环境配置的重要性: 正确的

.synopsys_dc.setup配置是成功综合的基础- 🔧 五大核心变量的正确设置

- 🛡️ 使用

set_app_var确保配置安全性 - 📁 动态路径管理提高项目可移植性

-

📁 项目结构标准化: 清晰的目录结构有助于项目管理和团队协作

- 🏗️ 标准化的目录层次结构

- 📋 规范的文件命名约定

- 🔄 版本控制和备份策略

-

🔍 渐进式验证: 通过逐步检查可以快速定位和解决问题

- ✅ 环境配置验证流程

- 🔗 RTL读取和链接检查

- ⏰ 时序约束完整性验证

-

⭐ 最佳实践应用: 使用先进的方法和工具提高脚本的健壮性

- 📜 文件列表管理多文件项目

- 🎨 GUI工具辅助调试和分析

- 📊 自动化报告生成和分析

🚀 进阶学习路径

🎓 建议的学习顺序:

-

🔍 深入理解综合算法

- 逻辑优化算法原理

- 时序驱动的综合策略

- 面积与速度的权衡技巧

-

⚡ 高级综合技术

compile_ultra高级选项- 层次化综合策略

- 增量综合和ECO流程

-

🎯 专项技能提升

- 低功耗设计(UPF)集成

- 可测试性设计(DFT)

- 多时钟域处理

-

🔗 EDA工具链集成

- 与ICC/Innovus的接口

- PrimeTime静态时序分析

- Formality形式化验证

💡 实践建议

🛠️ 日常工作流程优化

-

📋 建立标准化流程

# 创建项目模板 cp -r $DC_TEMPLATE_DIR $NEW_PROJECT_DIR cd $NEW_PROJECT_DIR # 更新配置文件 sed -i "s/TEMPLATE_NAME/$PROJECT_NAME/g" syn/config/*.tcl # 初始化环境 source setup_project.sh -

🔍 持续验证和监控

# 设置检查点 proc synthesis_checkpoint {stage_name} { write -format ddc -hier -out "checkpoints/${stage_name}.ddc" report_qor > "reports/${stage_name}_qor.rpt" puts "✅ Checkpoint saved: $stage_name" } -

📊 结果分析自动化

# Python脚本自动分析综合结果 import pandas as pd import matplotlib.pyplot as plt def analyze_synthesis_results(report_dir): # 解析时序报告 timing_data = parse_timing_report(f"{report_dir}/timing_report.rpt") # 解析面积报告 area_data = parse_area_report(f"{report_dir}/area_report.rpt") # 生成趋势图 plot_qor_trends(timing_data, area_data)

🎯 质量保证措施

| 检查项 | 工具/方法 | 通过标准 | 🚨 关注点 |

|---|---|---|---|

| ⏰ 时序收敛 | report_timing |

WNS ≥ 0ns | 关键路径分析 |

| 📊 面积目标 | report_area |

≤ 目标面积×1.1 | 资源利用率 |

| ⚡ 功耗估算 | report_power |

≤ 功耗预算 | 动态/静态功耗 |

| 🔗 连接性检查 | check_design |

0 Error | 悬空端口/信号 |

| 📐 约束覆盖 | check_timing |

100%覆盖 | 未约束路径 |

🌟 成功案例启示

通过学习本文档,您应该能够:

- ✅ 快速搭建标准化的DC综合环境

- 🎯 高效处理各种规模的设计项目

- 🔍 准确定位和解决常见综合问题

- 📊 系统分析综合结果和优化方向

- 🚀 持续改进综合流程和脚本质量

🤝 社区资源

- 📚 官方文档: Synopsys SolvNet技术支持

- 💬 技术论坛: EDABoard, Reddit r/FPGA

- 🎓 在线课程: Coursera, edX相关课程

- 📖 推荐书籍:

- "Digital Integrated Circuits" by Jan Rabaey

- "CMOS VLSI Design" by Weste & Harris

🎉 恭喜您完成了DC综合环境配置与实战指南的学习!

掌握这些基础知识和技能,将为您在数字IC设计和优化工作中奠定坚实的基础。记住,综合是一个迭代优化的过程,持续的学习和实践是提高综合质量的关键。祝您在IC设计的道路上越走越远! 🚀✨

浙公网安备 33010602011771号

浙公网安备 33010602011771号