01windows环境配置

Windows Verilog开发环境配置指南

本指南将详细介绍如何在Windows系统上搭建完整的Verilog开发和仿真环境,包括iverilog、gtkwave、vvp和make工具的安装与配置。

目录

环境概述

本开发环境包含以下工具:

- Icarus Verilog (iverilog): Verilog编译器

- VVP: Verilog仿真器

- GTKWave: 波形查看器

- Make: 自动化构建工具

Icarus Verilog安装与配置

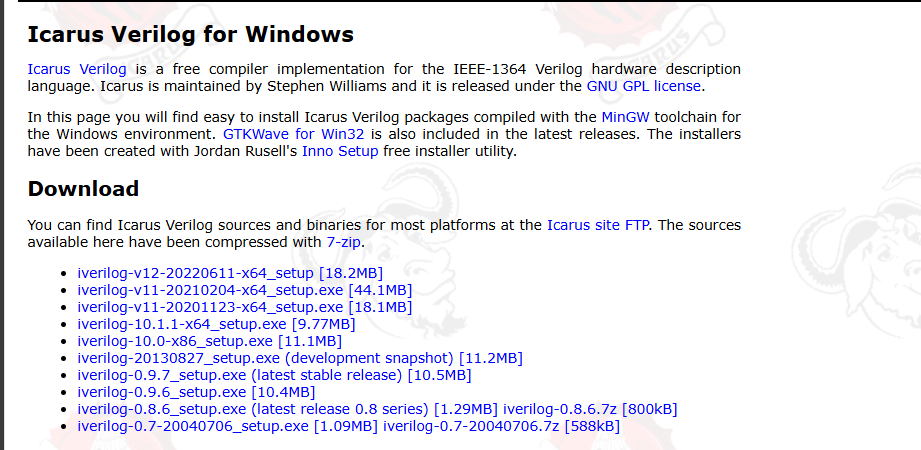

1. 下载Icarus Verilog

从官方下载地址下载iverilog软件包。

版本选择: 推荐使用v12版本,具有良好的稳定性和功能完整性。

2. 安装配置

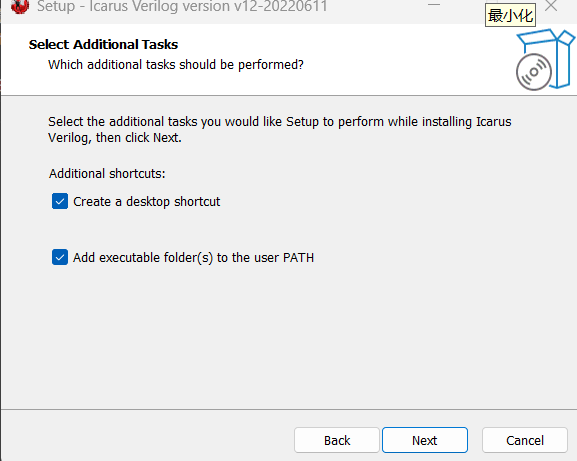

重要安装选项:

-

完整安装: 如果没有单独安装GTKWave,请选择"Full Installation"

-

环境变量配置: 安装时选择自动添加到环境变量

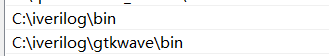

3. 手动配置环境变量(如需要)

如果安装时未自动配置环境变量,可以手动添加:

- 在Windows搜索框中搜索"环境变量"

- 将iverilog和gtkwave的可执行文件路径添加到系统PATH中

验证环境安装

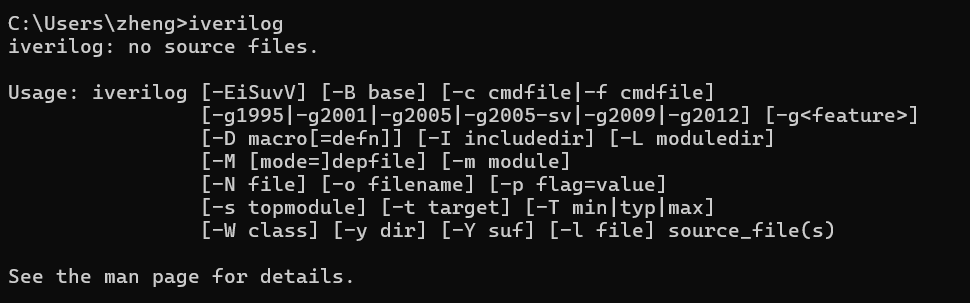

测试iverilog

在命令提示符中输入以下命令验证安装:

iverilog

正确安装后应显示如下信息:

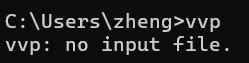

测试VVP仿真器

vvp

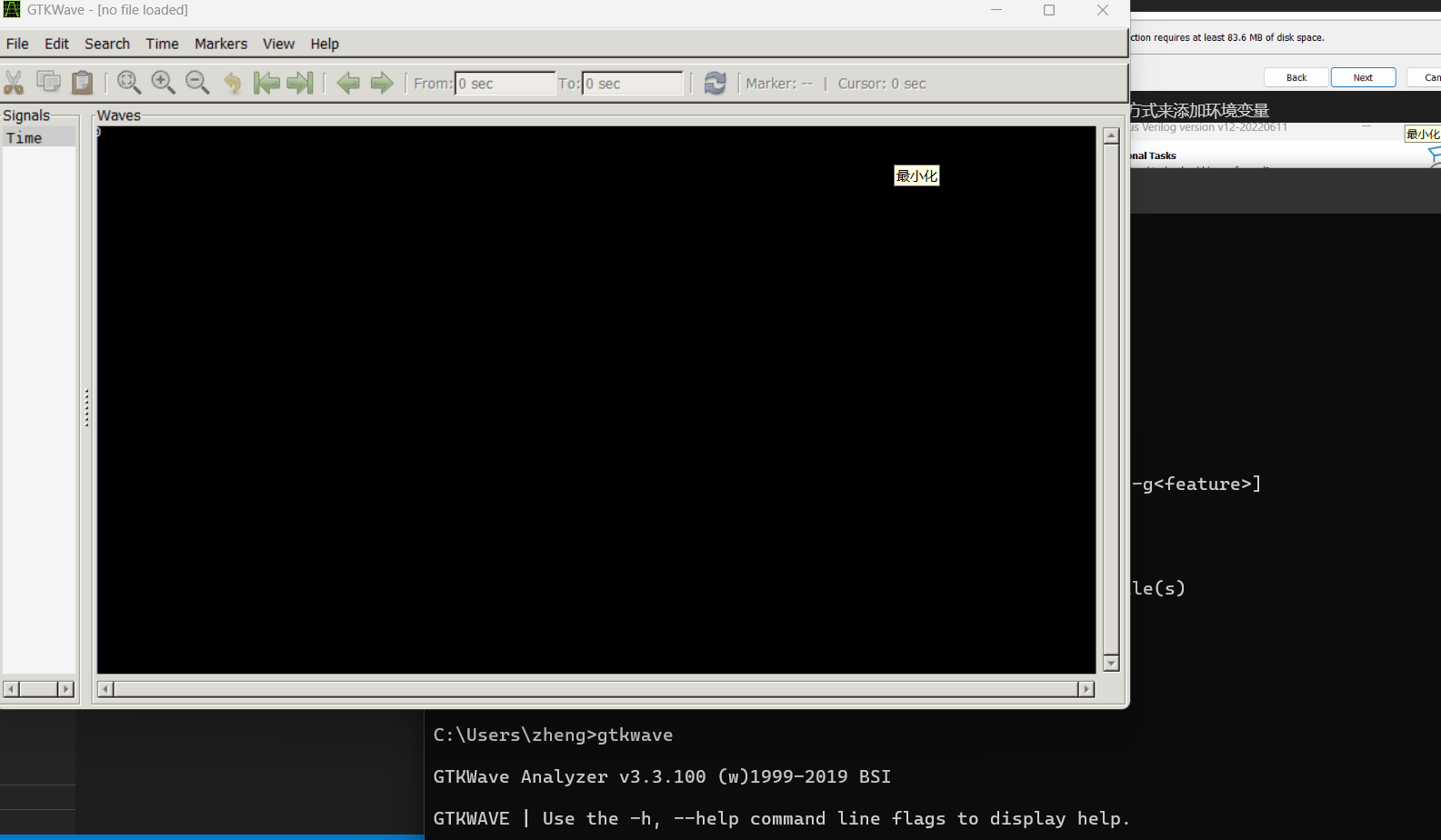

测试GTKWave

gtkwave

✅ 安装完成: 如果以上三个工具都能正常运行,恭喜您已成功搭建基础仿真环境!

实践示例

通过一个完整的计数器设计示例来演示整个开发流程。

设计模块 (counter.v)

module counter(

input wire clk,

input wire rstn,

output reg [2:0] cnt

);

always @(posedge clk or negedge rstn) begin

if(!rstn | cnt == 3'd5) begin

cnt = 3'b0;

end

else begin

cnt = cnt + 1'b1;

end

end

endmodule

测试平台 (counter_tb.v)

module counter_tb;

reg clk;

reg rstn;

wire [2:0] cnt;

// 实例化被测试模块

counter u_counter(

.clk(clk),

.rstn(rstn),

.cnt(cnt)

);

// 测试激励

initial begin

clk = 1'b0;

rstn = 1'b1;

#3 rstn = 1'b0;

#5 rstn = 1'b1;

#100 rstn = 1'b0;

#10 rstn = 1'b1;

#50;

$finish;

end

// 时钟信号生成

always #5 clk = ~clk;

// 波形文件生成

initial begin

$dumpfile("counter_tb.vcd");

$dumpvars(0, counter_tb);

end

endmodule

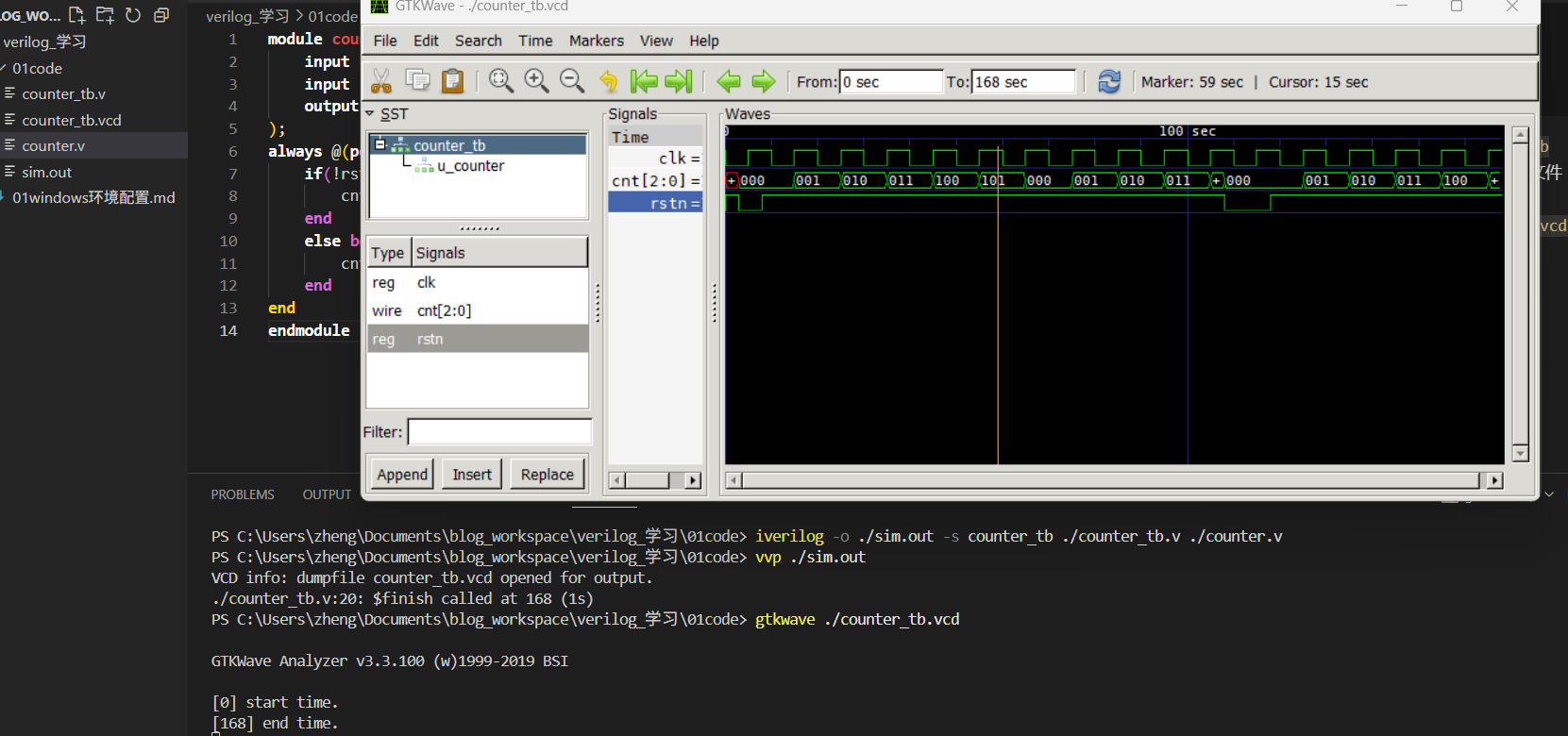

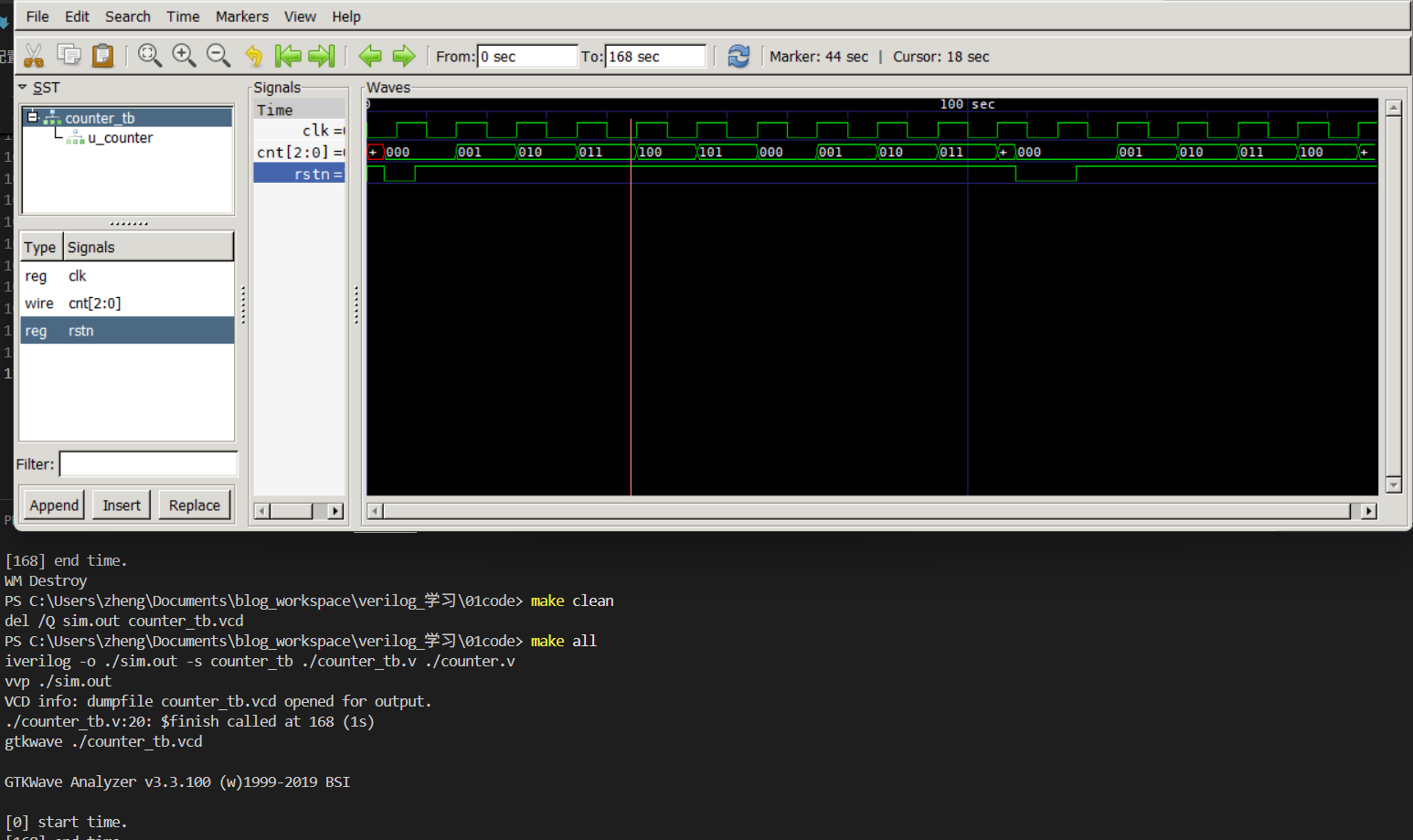

编译仿真流程

-

编译生成可执行文件

iverilog -o ./sim.out -s counter_tb ./counter_tb.v ./counter.v -

运行仿真

vvp ./sim.out -

查看波形

gtkwave ./counter_tb.vcd

运行结果

Make工具安装与使用

对于大型项目,重复输入编译命令会很繁琐。使用Make工具可以自动化整个构建和仿真流程。

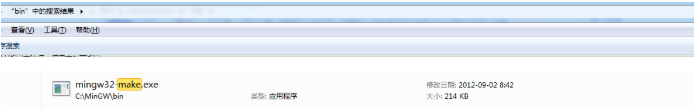

MinGW安装配置

1. 下载MinGW

从MinGW官方下载页面下载安装包。

2. 安装MinGW

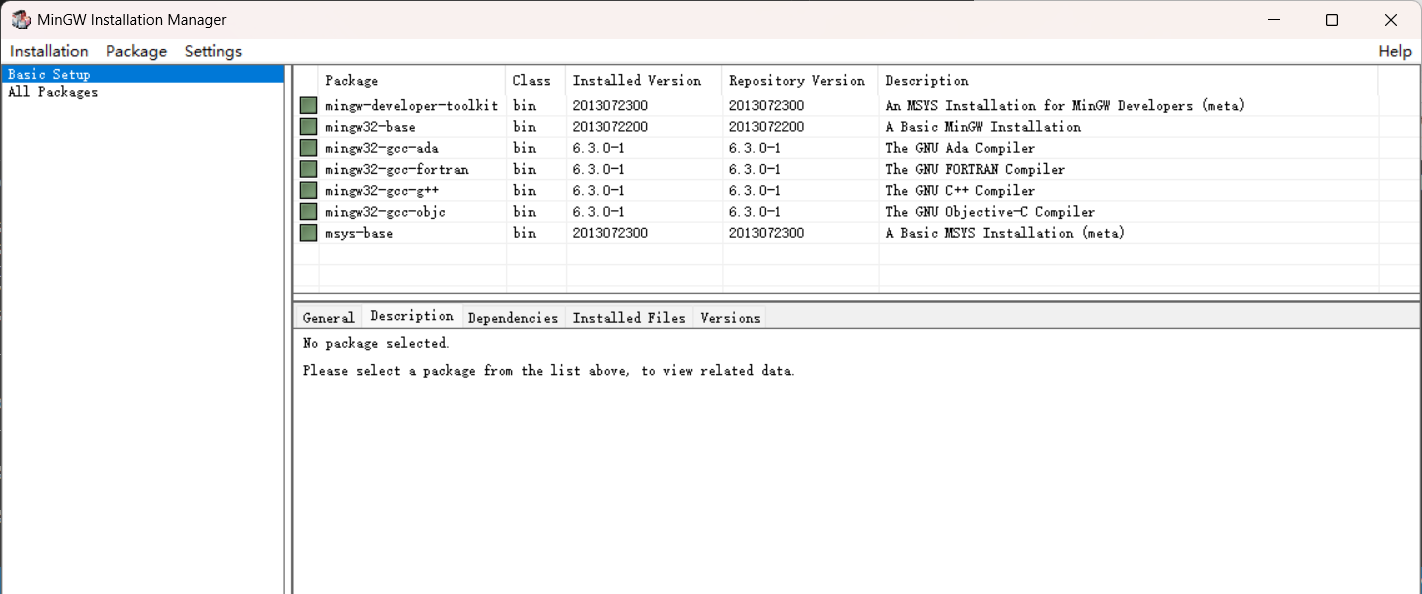

3. 选择安装包

在MinGW Installation Manager中选择需要的包:

推荐: 选择mingw32-base和mingw32-gcc-g++包。

4. 配置环境变量

-

找到MinGW安装目录下的bin文件夹

-

将该路径添加到系统环境变量PATH中

-

将

mingw32-make.exe重命名为make.exe

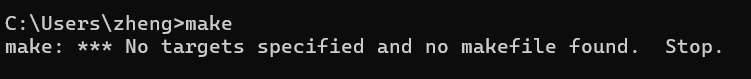

5. 验证安装

在命令提示符中测试make命令:

make

✅ 安装成功: 看到上述输出表示Make工具安装成功。

Makefile编写示例

创建Makefile文件来自动化构建流程:

# Makefile for Verilog simulation

all: iverilog_com vvp_sim gtk_wave

iverilog_com:

iverilog -o ./sim.out -s counter_tb ./counter_tb.v ./counter.v

vvp_sim:

vvp ./sim.out

gtk_wave:

gtkwave ./counter_tb.vcd

clean:

del /Q sim.out counter_tb.vcd

.PHONY: all iverilog_com vvp_sim gtk_wave clean

使用Makefile

创建Makefile后,在项目目录中运行:

make all

Make命令说明:

make all: 执行完整的编译、仿真、波形查看流程make clean: 清理生成的文件make iverilog_com: 仅执行编译make vvp_sim: 仅执行仿真make gtk_wave: 仅打开波形查看器

后续扩展

基础环境配置完成后,还可以继续扩展以下工具:

- VS Code插件: 提供语法高亮和智能提示

- ModelSim: 专业级仿真工具

- Vivado: Xilinx FPGA开发套件

说明: 这些高级工具的配置将在后续文档中详细介绍。

总结

通过以上步骤,您已经成功搭建了完整的Windows Verilog开发环境,包括:

✅ Icarus Verilog编译器

✅ VVP仿真器

✅ GTKWave波形查看器

✅ Make自动化构建工具

现在您可以开始愉快的Verilog设计之旅了!

浙公网安备 33010602011771号

浙公网安备 33010602011771号