计数器阶段三 - 练习四

题目:输入din 和din_vld均为1,输出dout_vld 为1位,dout为8位。复位后,第一次din_vld = 1时,将当前的din赋给dout[7] ,第二次赋给dout[6] ,

以此类推,第八次时赋给dout[0],同时产生dout_vld的脉冲。然后循环。

1 module test_cnt( 2 clk , 3 rst_n , 4 din_vld , 5 din , 6 dout , 7 dout_vld, 8 ); 9 10 input clk ; 11 input rst_n; 12 input din_vld; 13 input din; 14 output [7:0] dout; 15 output dout_vld; 16 17 wire add_cnt0; 18 wire end_cnt0; 19 20 reg dout_vld; 21 reg [7:0] dout ; 22 reg [3:0] cnt0 ; 23 24 always @(posedge clk or negedge rst_n)begin 25 if(!rst_n)begin 26 cnt0 <= 0; 27 end 28 else if(add_cnt0)begin 29 if(end_cnt0)begin 30 cnt0 <= 0; 31 end 32 else begin 33 cnt0 <= cnt0 + 1; 34 end 35 end 36 end 37 38 assign add_cnt0 = din_vld; //将din_vld作为计数器加1条件 39 assign end_cnt0 = add_cnt0 && cnt0 == 8 - 1; 40 41 reg [8-1:0] dout_temp; 42 always @(posedge clk or negedge rst_n)begin 43 if(!rst_n)begin 44 dout_temp <= 0; 45 end 46 else if(add_cnt0)begin //在din_vld = 1期间将din赋给dout 47 dout_temp[7 - cnt0] <= din; 48 end 49 end 50 51 always @(posedge clk or negedge rst_n)begin 52 if(!rst_n)begin 53 dout <= 0; 54 end 55 else if(end_cnt0)begin 56 dout <= dout_temp; //收完一个完整的8bit数据锁存 57 end 58 end 59 60 always @(posedge clk or negedge rst_n)begin 61 if(!rst_n)begin 62 dout_vld <= 0; 63 end 64 else if(end_cnt0)begin //产生一个有效信号,且只保留一个时钟周期 65 dout_vld <= 1; 66 end 67 else begin 68 dout_vld <= 0; 69 end 70 end 71 72 73 endmodule

测试文件:

1 module top_sim; 2 3 reg clk; 4 reg rst_n; 5 reg din_vld; 6 reg din; 7 8 wire dout_vld; 9 wire [7:0] dout; 10 11 `define CYCLE 20 12 13 initial begin 14 clk = 0; 15 forever 16 #(`CYCLE/2) clk = ~clk; 17 end 18 19 initial begin 20 #1; 21 rst_n = 0; 22 #(`CYCLE*5); 23 rst_n = 1; 24 end 25 26 initial begin 27 #1; 28 din_vld = 0; 29 repeat(100)begin 30 #(`CYCLE*3); 31 din_vld = $urandom_range(0,1); //$urandom_range(min,max)生成min到max范围内的随机无符号整数 32 //din = $signed($urandom_range(1,2))-1; 33 #(`CYCLE*$urandom_range(2,5)); 34 end 35 end 36 37 38 initial begin 39 #1; 40 din = 0; 41 repeat(100)begin 42 #(`CYCLE*1); 43 din = $urandom_range(0,1); //$urandom_range(min,max)生成min到max范围内的随机无符号整数 44 //din = $signed($urandom_range(1,2))-1; 45 #(`CYCLE*$urandom_range(1,8)); 46 end 47 end 48 49 test_cnt u1( 50 .clk (clk ), 51 .rst_n (rst_n ), 52 .din (din ), 53 .din_vld (din_vld ), 54 .dout (dout ), 55 .dout_vld (dout_vld ) 56 ); 57 58 endmodule

这里利用一个函数:

$urandom_range(min,max); 生成min到max范围内的随机无符号整数

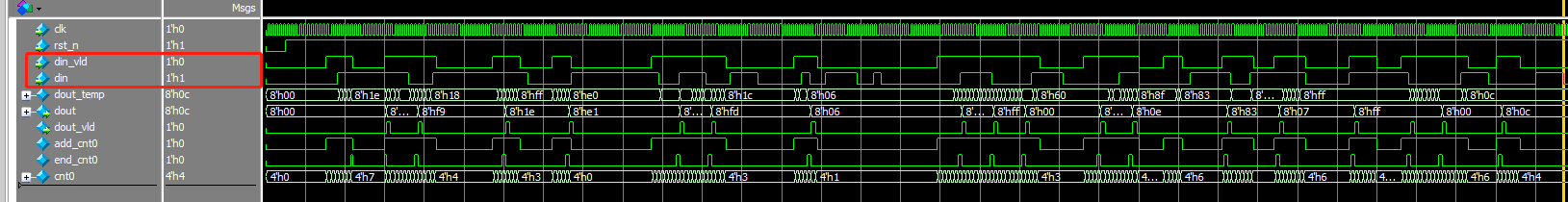

产生的随机波形:

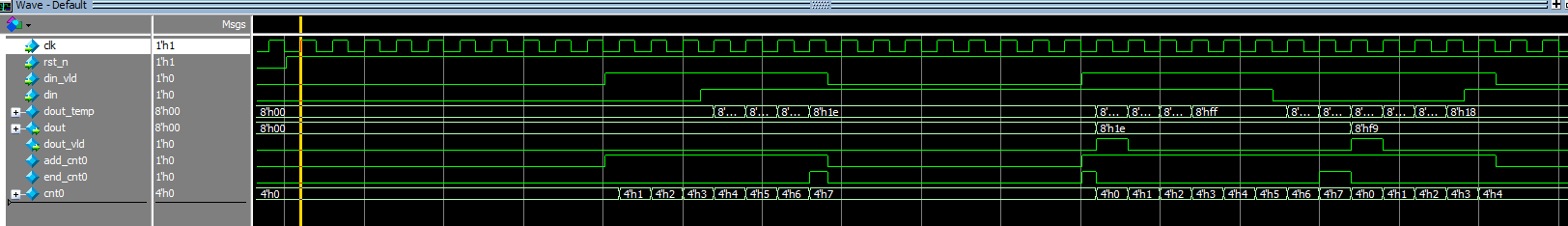

仿真波形:

浙公网安备 33010602011771号

浙公网安备 33010602011771号