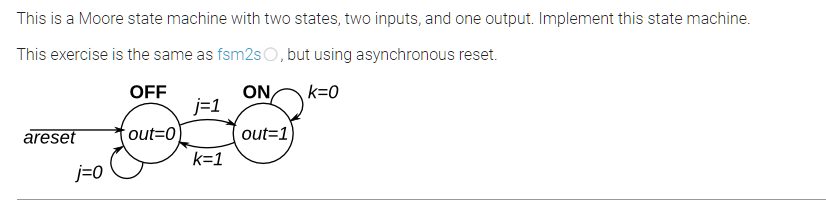

1 要求

![]()

2.1 异步

module top_module(

input clk,

input areset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

case (state)

OFF:begin

if (j==1'b1 )begin

next_state =ON;

end

else

next_state =OFF;

end

ON:begin

if( k==1'b1 )begin

next_state = OFF;

end

else begin

next_state = ON;

end

end

default:begin

next_state = OFF;

end

endcase

end

always @(posedge clk , posedge areset) begin

// State flip-flops with asynchronous reset

if(areset ==1'b1 )begin

state <= OFF;

end

else

state <= next_state;

end

// Output logic

// assign out = (state == ...);

assign out =(state == ON)?1'b1:1'b0;

endmodule

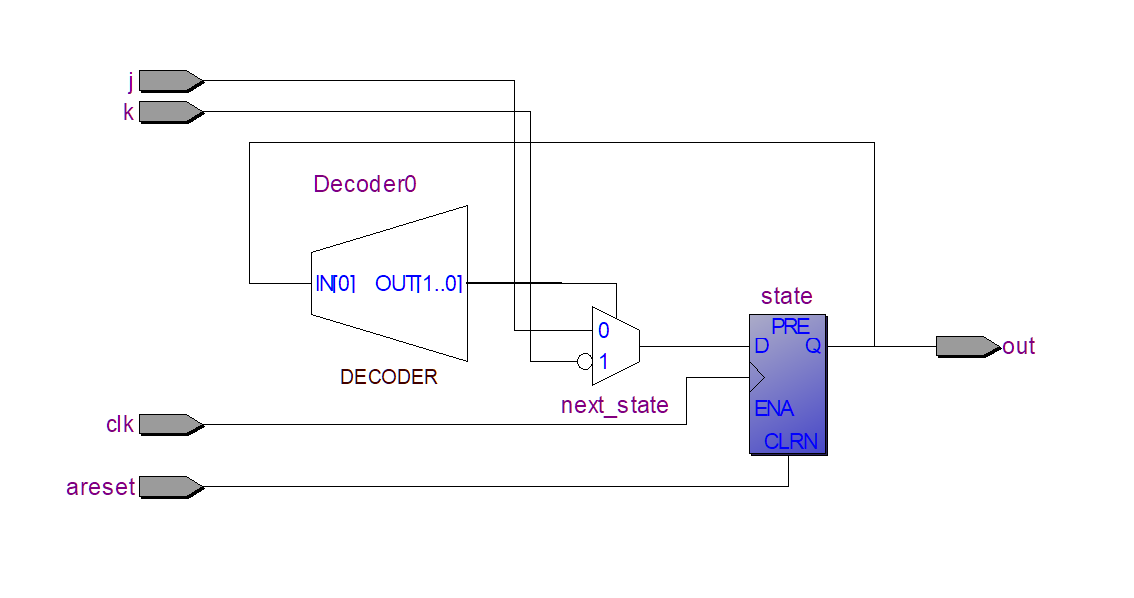

2.2 原理图

![]()

3.1 同步

module top_module(

input clk,

input reset, // Synchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

case(state)

OFF:begin

if(j==1'b1)begin

next_state = ON;end

else begin

next_state = OFF;

end

end

ON:begin

if (k==1'b1) begin

next_state = OFF;end

else begin

next_state = ON;

end

end

default:begin

next_state = OFF;

end

endcase

end

always @(posedge clk) begin

// State flip-flops with synchronous reset

if(reset==1'b1)begin

state <= OFF;

end

else begin

state <= next_state;

end

end

// Output logic

// assign out = (state == ...);

assign out = (state == ON)?1'b1:1'b0;

endmodule

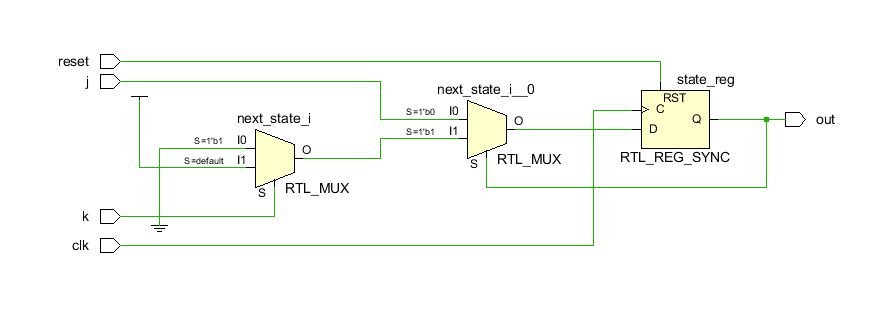

3.2 原理图

![]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号