使用FDATOOL生成xilinx中FIR滤波器IP核的系数

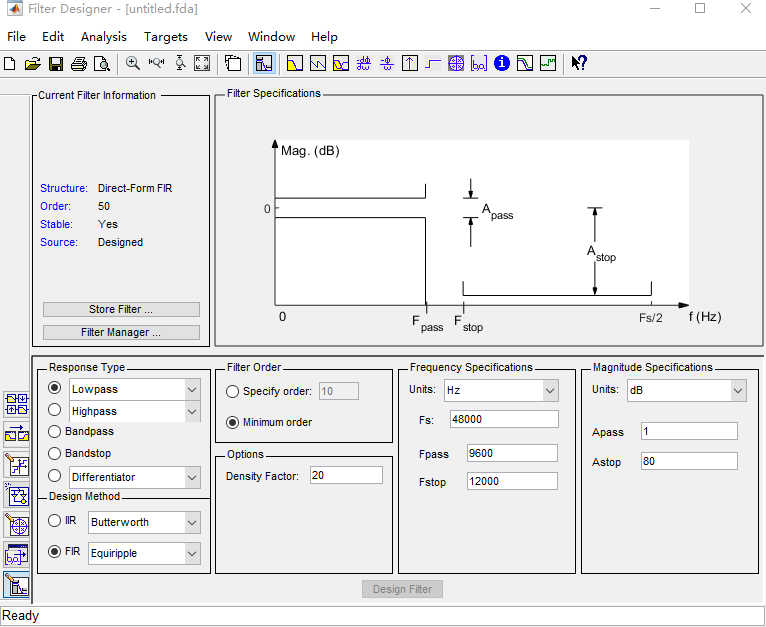

1、在MATLAB命令窗口输入fdatool后回车,打开“Filter Designer & Analysis Tool”工具界面:

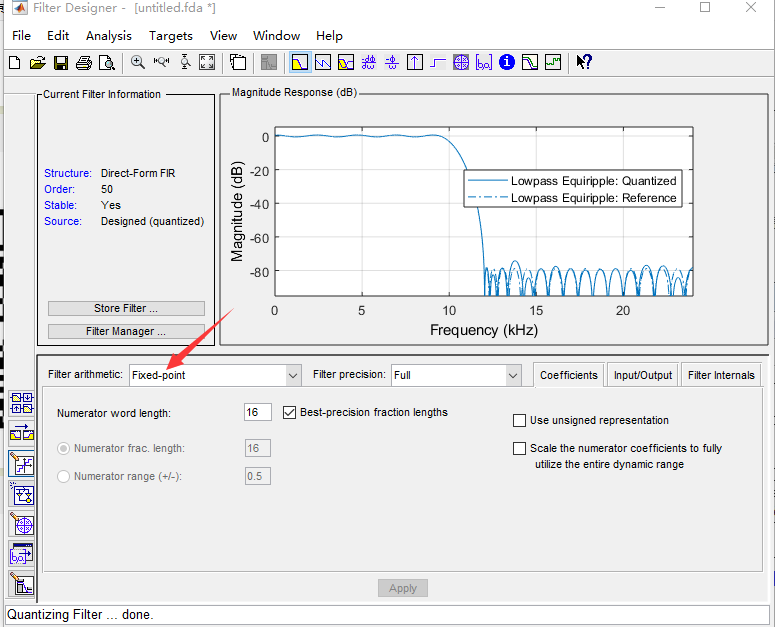

2、点击左下角的Set quantization parameter,设置Filter arithmetic为Fixed-point(定点,由于有些FPGA中是不能直接对浮点数进行操作的,只能采用定点数进行数值运算,参考http://blog.csdn.net/gsh_hello_world/article/details/78742769):

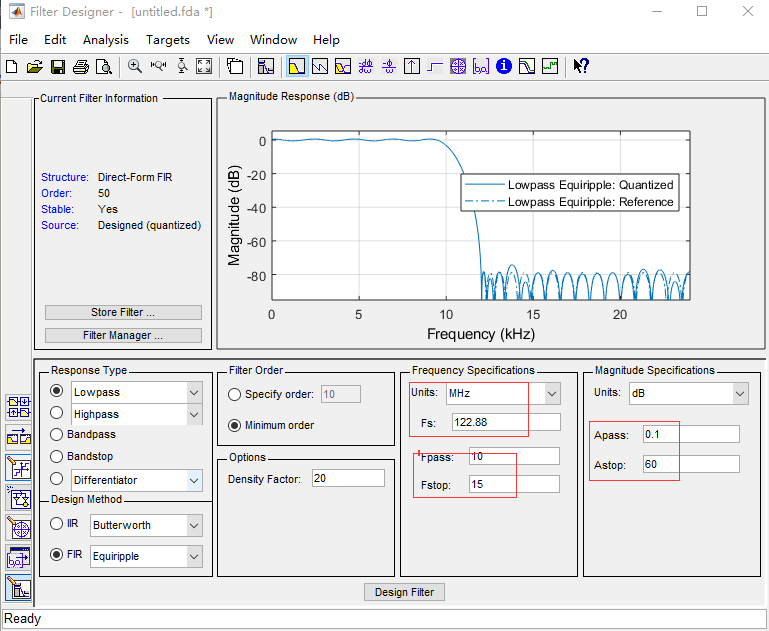

3、点击左下角的Design filter,进入滤波器参数设置页面,在其中设置采样频率(Fs)、通带频率(Fpass)、阻带频率(Fstop)、通带衰减(Apass)以及阻带衰减(Astop)等参数,并点击最下面的“Design Filter”按钮生成滤波器系数

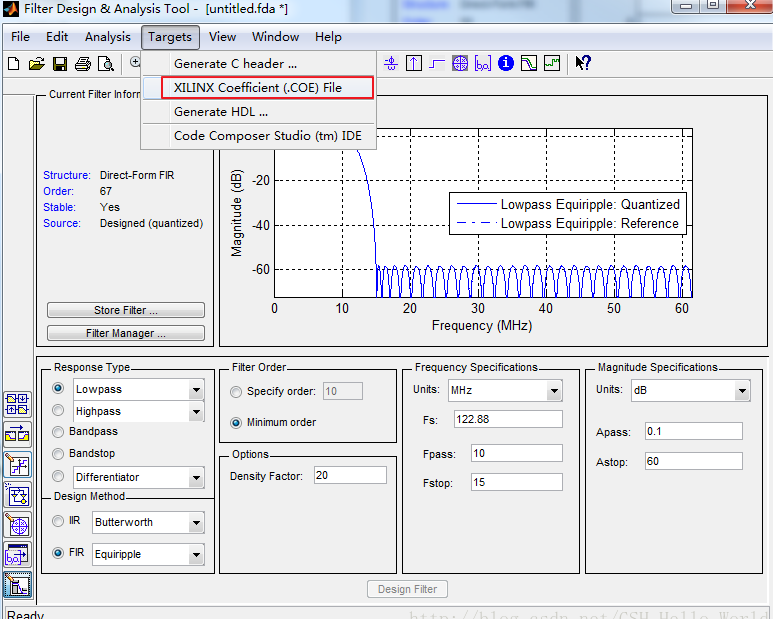

4、Targets —> XILINX Coefficient(.COE) File导出coe文件,此文件中的系数是以定点十六进制表示的,每个数据长度为16位(由Numerator word length决定),其为实际浮点数据左移17位(由Numerator frac. length决定)得到,例如实际浮点数据第一个系数为0.001,定点表示为0x0081((int)0.001 * 2 ^ 17 = 131 = 0x0081,即0.001左移17位):

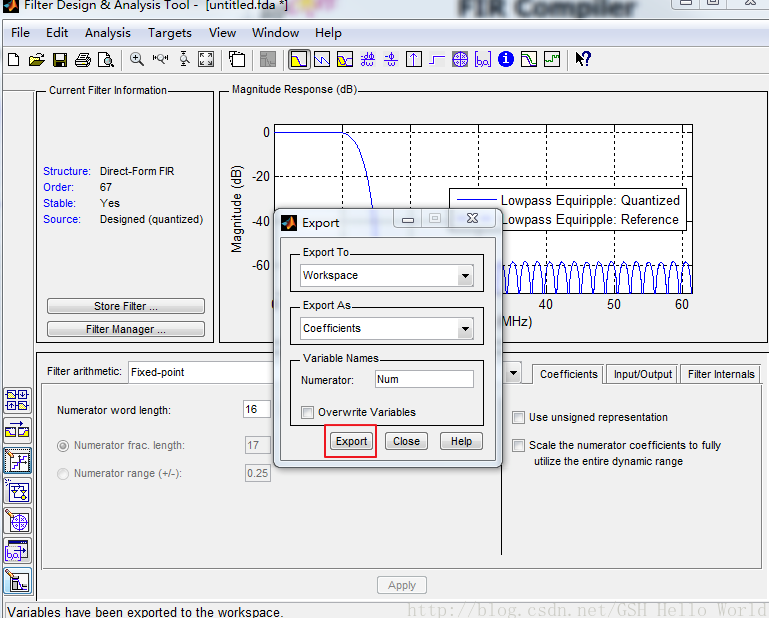

5、也可以点击File —> Export导出滤波器系数到matlab的工作区workspace,快捷键Ctrl+E,这种方式导出的是实际浮点数据:

6、之后生成IP核的步骤参考博客:http://blog.csdn.net/weiweiliulu/article/details/40151053

---------------------

作者:高世皓

来源:CSDN

原文:https://blog.csdn.net/GSH_Hello_World/article/details/78746054

版权声明:本文为博主原创文章,转载请附上博文链接!

浙公网安备 33010602011771号

浙公网安备 33010602011771号