以太网学习(二)——PHY芯片

PHY芯片的基本功能

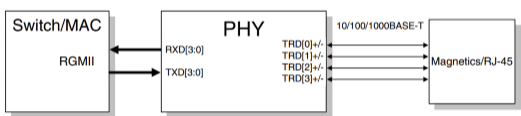

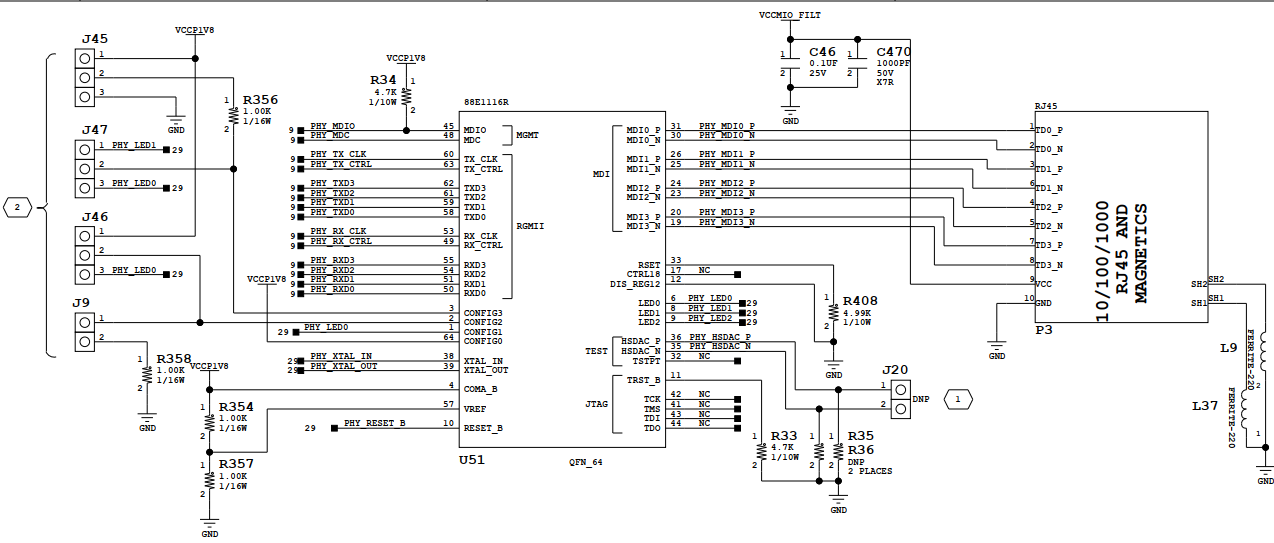

PHY和RJ45接口之间的连接就是学习一中提到的千兆以太网RJ45接口的那4对差分模拟信号线。通过PHY芯片实现了差分信号对到数字信号的转换,也就是图中的RXD和TXD。

除此之外PHY芯片还提供了通信速率自协商,驱动通信指示LED灯等功能。

PHY芯片数据手册(88E1116R芯片)

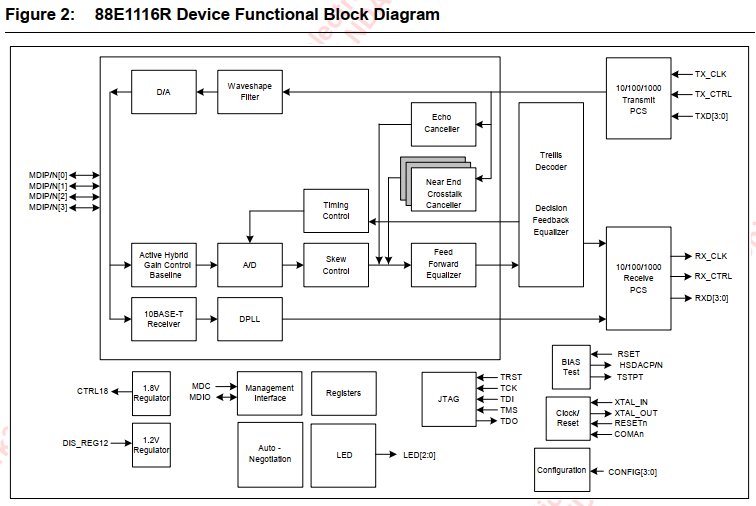

系统框图

右上角的TX_CLK, TX_CTRL和TXD[3:0]是来自FPGA的MAC层的将要发送的信号(RGMII接口),经过PCS(物理编码子层)编码,并且滤波之后,进行DAC,将数字信号转换成差分模拟信号对,通过4对差分信号对MDIO发送到RJ45接口。接收端同理,通过MDIO接收到的差分模拟信号经过AD变换成数字信号,然后均衡、解码之后发送给FPGA的MAC层。

同时图中下中部还有与RJ45接口交互的LED的驱动,以及与FPGA的MAC层交互的配置接口MDC, MDIO。

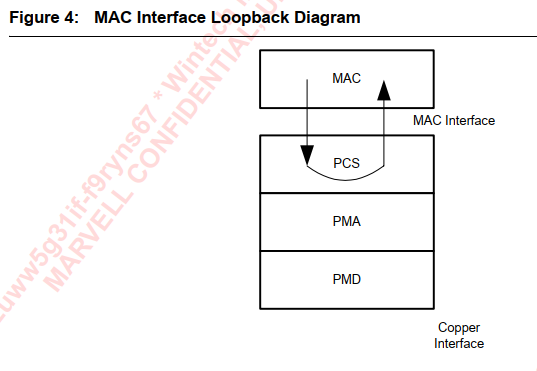

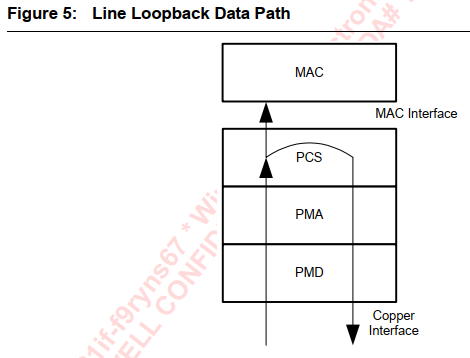

环回模式

MAC环回模式(内部环回):用于测试MAC层是否正常

Line环回模式:测试用于测试差分接口和RJ45是否是连通的

外部环回模式:

关键寄存器

- MII 控制寄存器(Table 37):包括复位,子贿赂模式,速度选择,自协商使能,隔离RGMII接口模式,重新开始自协商,双工模式,冲突测试使能等

- 状态寄存器(Table 52):自协商完成标志,连接状态,速度状态

ZC706开发板的PHY芯片原理图

参考:正点原子视频

浙公网安备 33010602011771号

浙公网安备 33010602011771号