这是一系列五个练习中的第三个部分,这些练习由几个较小的电路构建一个复杂的计数器。 请参阅 最终练习 。

作为用于控制移位寄存器的 FSM 的一部分,我们希望能够在检测到正确的位模式时启用移位寄存器恰好 4 个时钟周期。 中处理序列检测 Exams/review2015_fsmseq ,因此 FSM 的这一部分仅处理启用 4 个周期的移位寄存器。

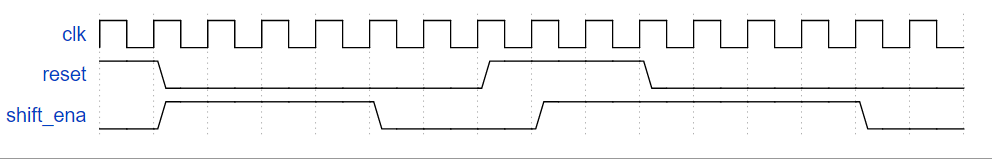

每当 FSM 复位时,将 shift_ena 4 个周期,然后永远为 0(直到复位)

module top_module (

input clk,

input reset, // Synchronous reset

output shift_ena);

reg [1:0]cnt;

always@(posedge clk)

if(reset)

cnt<=2'd0;

else if(cnt==2'd3)

cnt<=2'd3;

else

cnt<=cnt+1;

always@(posedge clk)

if(reset)

shift_ena<=1;

else if(cnt==2'd3)

shift_ena<=0;

else

shift_ena<=shift_ena;

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号