这是一系列五个练习中的第二个组成部分,这些练习由几个较小的电路构建一个复杂的计数器。 请参阅 最终练习 。

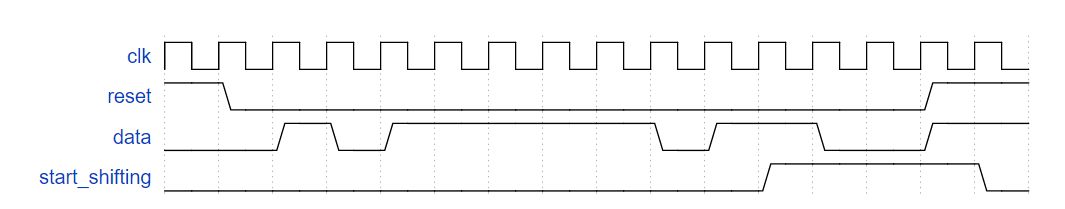

构建一个有限状态机,在输入比特流中搜索序列 1101。 找到序列后,应将 start_shifting 为 1,直到重置。 陷入最终状态旨在模拟在尚未实现的更大 FSM 中进入其他状态。 我们将在接下来的几个练习中扩展这个 FSM。

module top_module (

input clk,

input reset, // Synchronous reset

input data,

output start_shifting);

parameter IDLE=0,A=1,B=2,C=3,D=4,E=5,stop=6;

reg [2:0] state,nstate;

always@(posedge clk)

if(reset)

state<=A ;

else

state<=nstate;

always@(*)

case(state)

A:nstate=data?B:A;

B:nstate=data?C:A;

C:nstate=data?C:D;

D:nstate=data?D:A;

default:nstate=A;

endcase

always@(posedge clk )

if(reset)

start_shifting<=0;

else if(state==D&&data==1)

start_shifting<=1;

else

start_shifting<=start_shifting;

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号