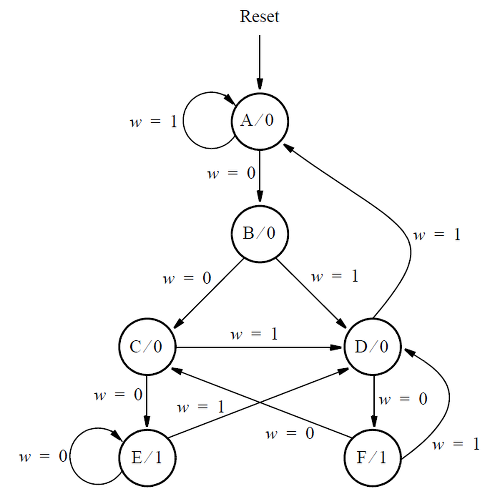

考虑如下所示的状态机,它有一个输入 w 和一个输出 z 。

实现状态机。 (这部分不在期中,但编写 FSM 是一种很好的做法)。

module top_module (

input clk,

input reset, // synchronous reset

input w,

output z);

parameter A=6'b000001,B=6'b000010,C=6'b000100,D=6'b001000,E=6'b010000,F=6'b100000;

wire [5:0] state,nstate;

always@(posedge clk)

if(reset)

state<=A;

else

state<=nstate;

always@(*)

case(state)

A:nstate=w?A:B;

B:nstate=w?D:C;

C:nstate=w?D:E;

D:nstate=w?A:F;

E:nstate=w?D:E;

F:nstate=w?D:C;

default:nstate=A;

endcase

assign z=state==E|state==F;

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号