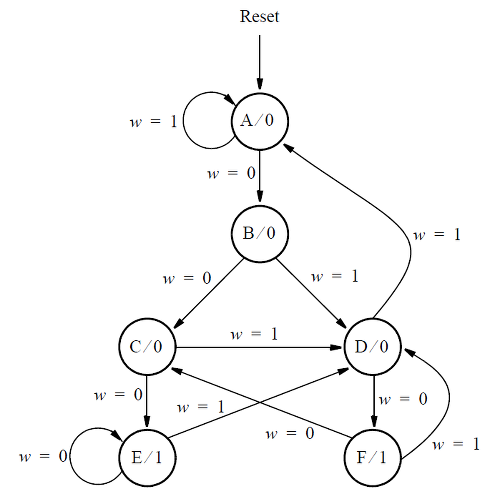

考虑如下所示的状态机,它有一个输入 w 和一个输出 z 。

对于这一部分,假设状态分配 'y[6:1] = 000001, 000010, 000100, 001000, 010000, 100000 分别用于状态 A、B、...、F 的 one-hot 代码。

为下一状态信号 Y2 和 Y4 编写逻辑表达式。 (通过假设 one-hot 编码的检查推导出逻辑方程。测试台将使用非 one hot 输入进行测试,以确保您不会尝试做更复杂的事情)。

module top_module (

input [6:1] y,

input w,

output Y2,

output Y4);

parameter A=6'b000001,B=6'b000010,C=6'b000100,D=6'b001000,E=6'b010000,F=6'b100000;

wire [6:1] nstate;

always@(*)

case(y)

A:nstate=w?A:B;

B:nstate=w?D:C;

C:nstate=w?D:E;

D:nstate=w?A:F;

E:nstate=w?D:E;

F:nstate=w?D:C;

default:nstate=A;

endcase

assign Y2=y[1] & ~w;

assign Y4=(y[2] & w) | (y[3] & w) | (y[5] & w) | (y[6] & w);

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号