module top_module(

input clk,

input in,

input reset, // Synchronous reset

output [7:0] out_byte,

output done

); //

parameter IDLE=5'b0001,

START=5'b00010,

DATA=5'b00100,

STOP=5'b01000,

ERROR=5'b10000;

reg [2:0] state,nstate;

reg [3:0] cnt;

reg [7:0] out;

wire odd;

always@(posedge clk)

if(reset)

state<=IDLE;

else

state<=nstate;

always@(posedge clk)

if(reset)

cnt<=4'd0;

else if(nstate==DATA||nstate==STOP)

cnt<=cnt+4'd1;

else

cnt<=cnt;

always@(*)

case(state)

IDLE:nstate=in?IDLE:START;

START:nstate=DATA;

DATA:nstate=(cnt==9)?(in?STOP:ERROR):DATA;

STOP:nstate=in?IDLE:START;

ERROR:nstate=in?IDLE:ERROR;

default:nstate<=IDLE;

endcase

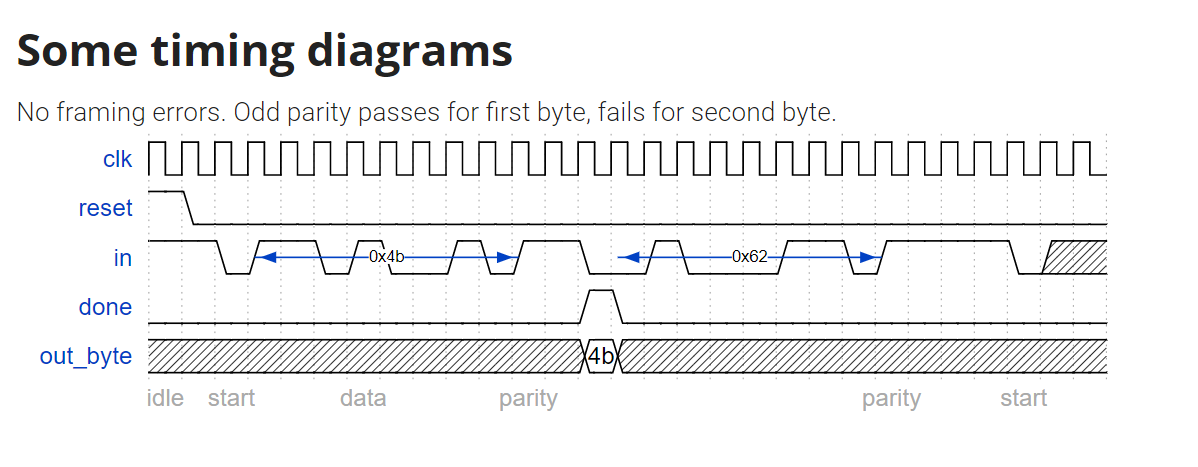

// Modify FSM and datapath from Fsm_serialdata

always@(posedge clk)

if(reset)

out<=8'd0;

else

out<={in,out[7:1]};

always@(posedge clk)

if(reset)

out_byte<=8'd0;

else if(cnt==4'd8)

out_byte<=out;

else

out_byte<=out_byte;

// New: Add parity checking.

parity parity_inst(clk,(state!==START),in,odd);

assign done=(state==STOP);

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号