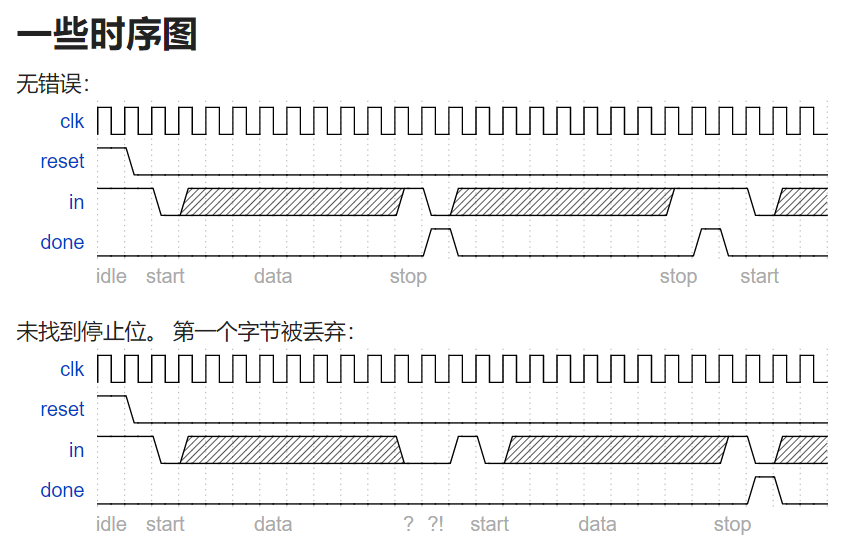

在许多(较旧的)串行通信协议中,每个数据字节都与一个起始位和一个停止位一起发送,以帮助接收器从位流中划定字节。 一种常见的方案是使用 1 个起始位 (0)、8 个数据位和 1 个停止位 (1)。 当没有传输任何内容(空闲)时,该线路也处于逻辑 1。

设计一个有限状态机,当给定比特流时,它将识别何时正确接收到字节。 它需要识别起始位,等待所有 8 个数据位,然后验证停止位是否正确。 如果停止位未按预期出现,则 FSM 必须等到找到停止位后再尝试接收下一个字节。

module top_module(

input clk,

input in,

input reset, // Synchronous reset

output done

);

reg [1:0] state,nstate;

parameter IDLE=4'd0,START=4'd1,D1=4'd2,D2=4'd3,D3=4'd4,D4=4'd5,D5=4'd6,D6=4'd7,D7=4'd8,D8=4'd9,STOP=4'd10,SEARCH=4'd11;

always@(*)

begin

case(state)

IDLE:nstate=in?IDLE:START;

START:nstate=D1;

D1:nstate=D2;

D2:nstate=D3;

D3:nstate=D4;

D4:nstate=D5;

D5:nstate=D6;

D6:nstate=D7;

D7:nstate=D8;

D8:nstate=in?STOP:SEARCH;

SEARCH:nstate=in?IDLE:SEARCH;

STOP:nstate=in?IDLE:START;

default:nstate=IDLE;

endcase

end

always@(posedge clk)

begin

if(reset)

state<=IDLE;

else

state<=nstate;

end

assign done=state==STOP;

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号