第四章 触发器

概述

1,触发器的基本特点和作用

Flip-Flop,简写FF,又称双稳态触发器。

1,基本特点

(1)具有两个能自我保持的稳定状态(稳态)

一般用Q状态表示触发器的状态

(2)在输入信号作用下,触发器的两个稳定状态可以相互转换(状态的翻转)

输入信号消失后,新状态可以保留下来

2,触发器的作用

触发器和门电路是构成数字电路的基本单元

触发器有记忆功能——时序逻辑电路,门电路无——组合逻辑电路

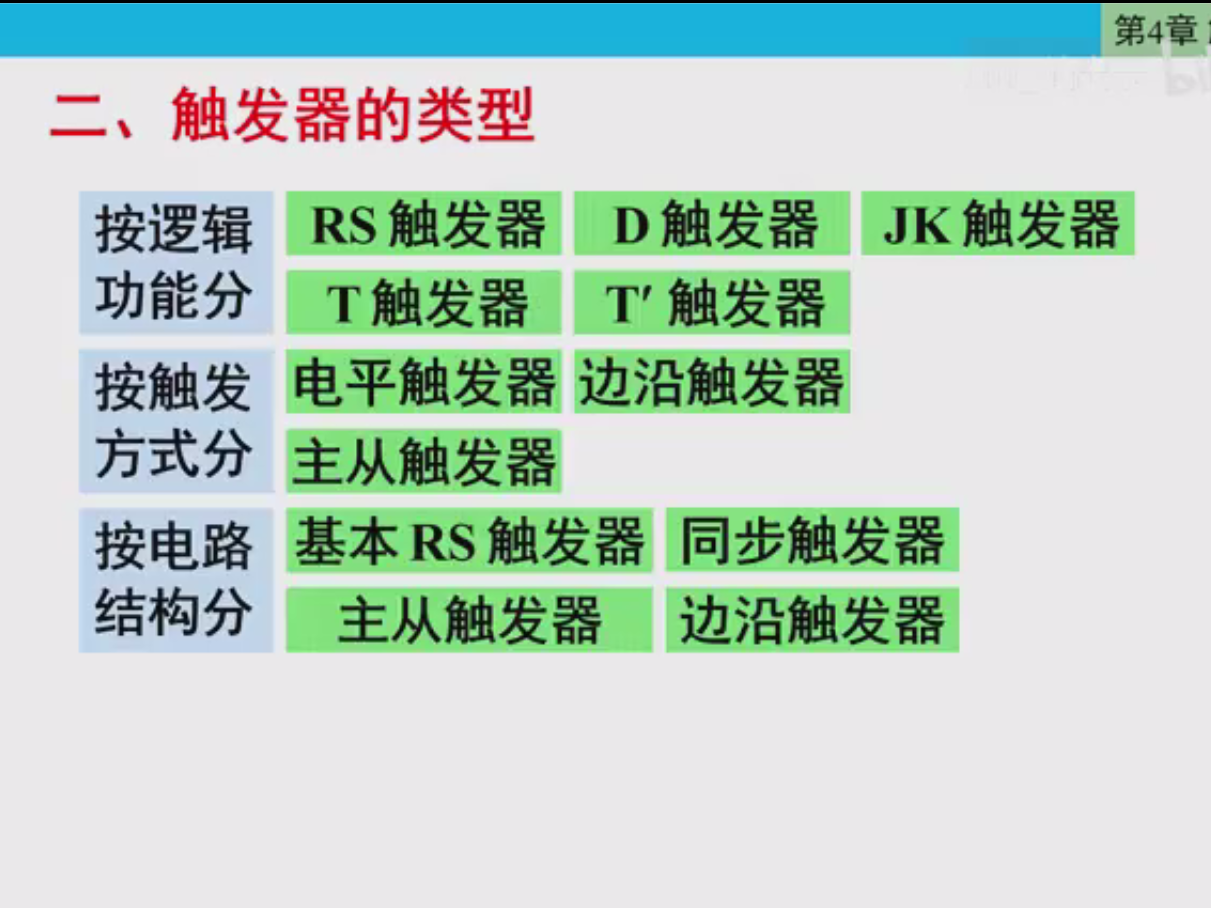

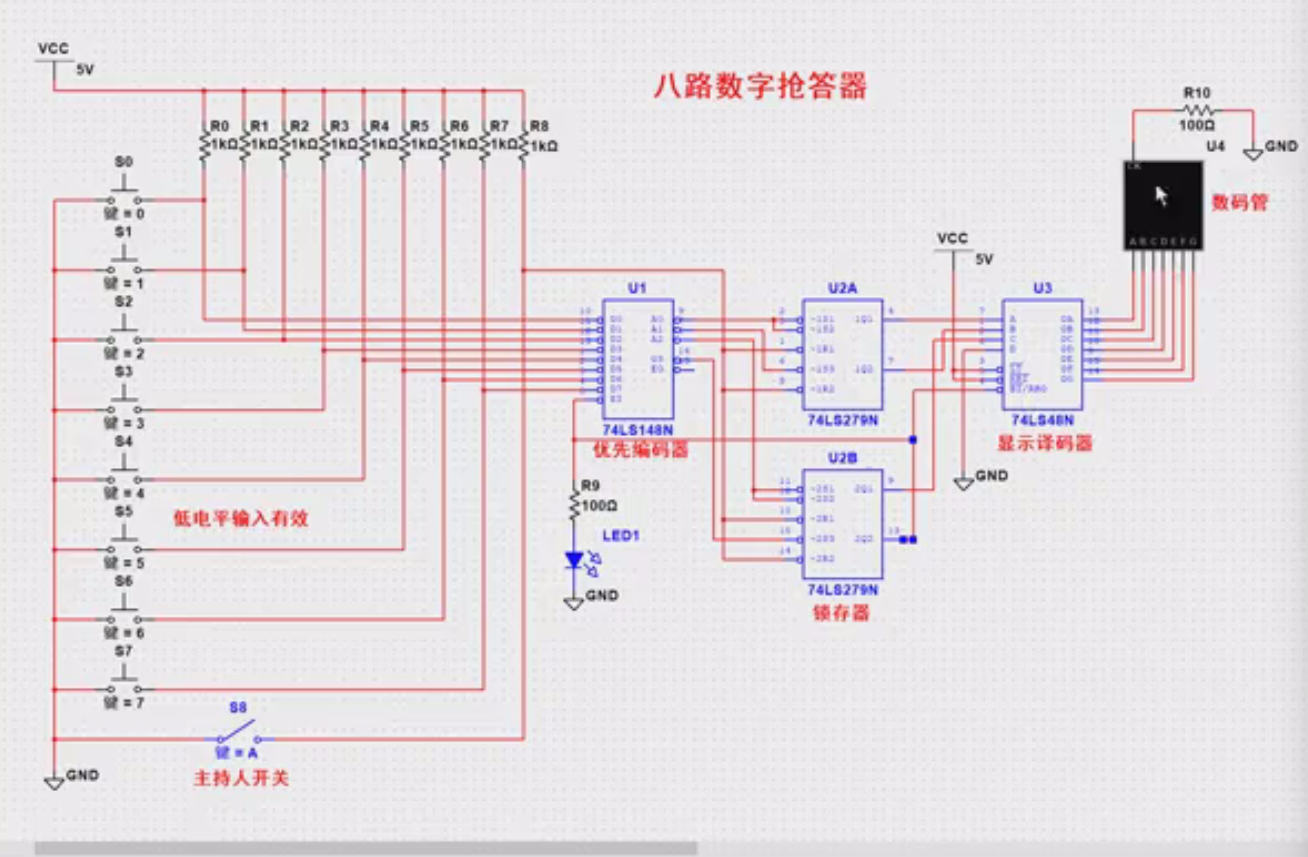

2,触发器的类型![img]()

3,触发器逻辑功能的描述方法

主要有特性表,特征方程,激励表(驱动表),状态转换图和波形图(时序图)等

4.1 基本触发器

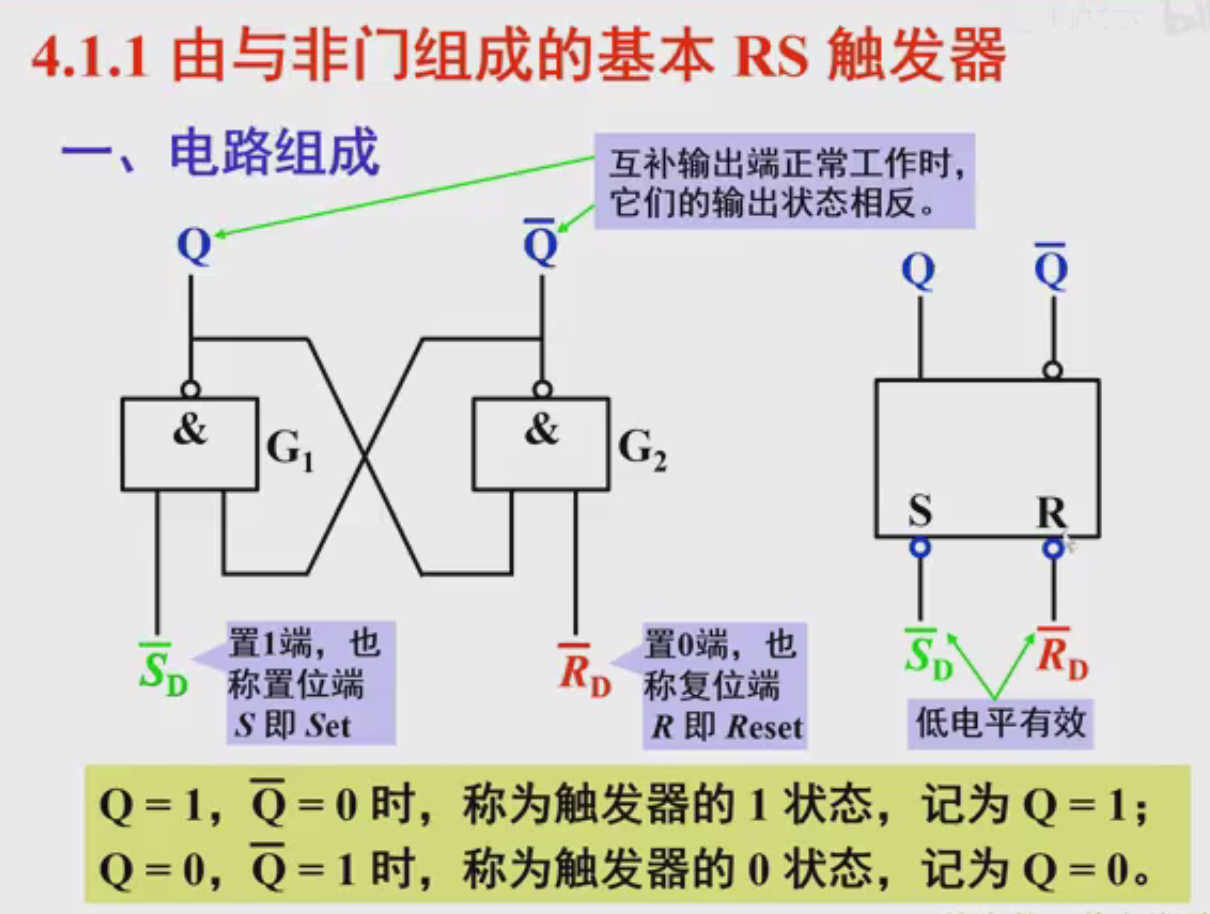

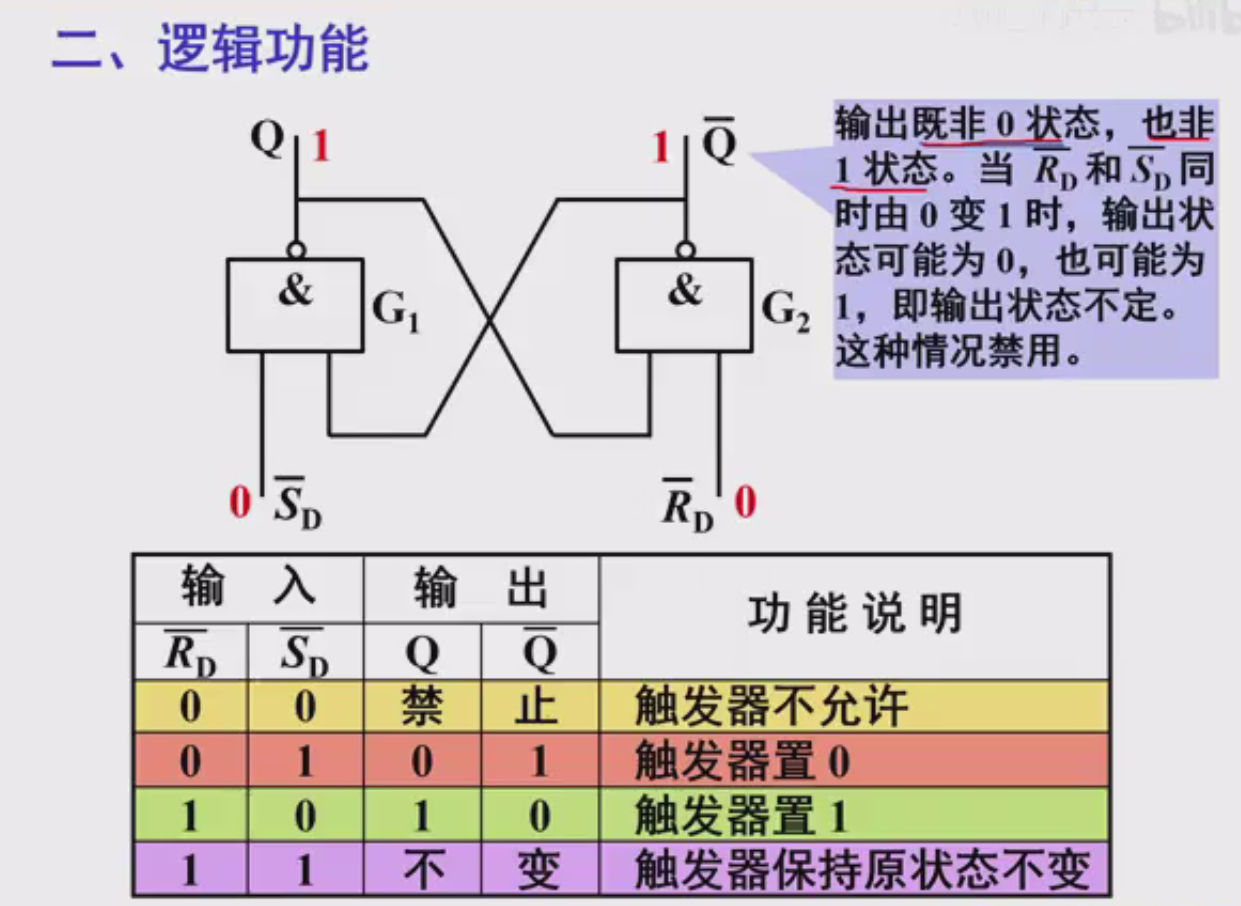

4.1.1由与非门组成的基本RS触发器

1,电路组成

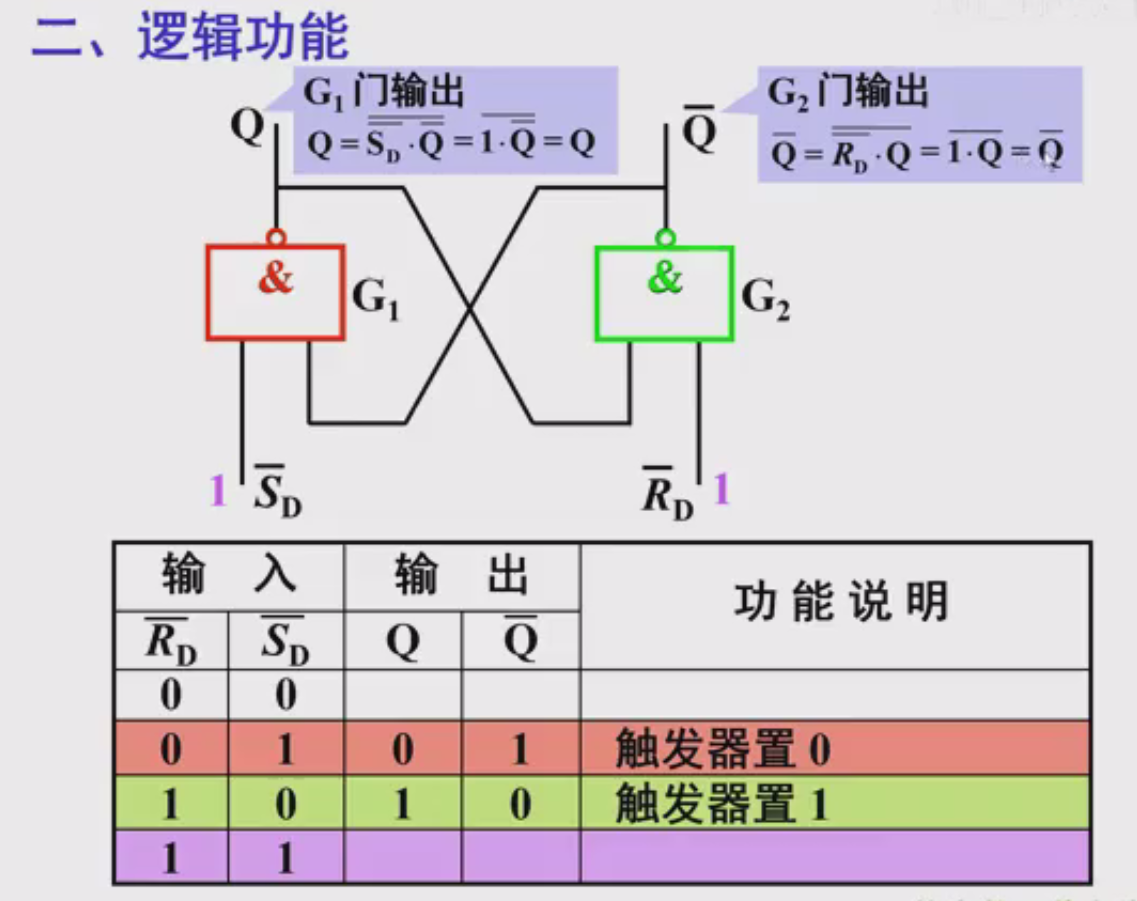

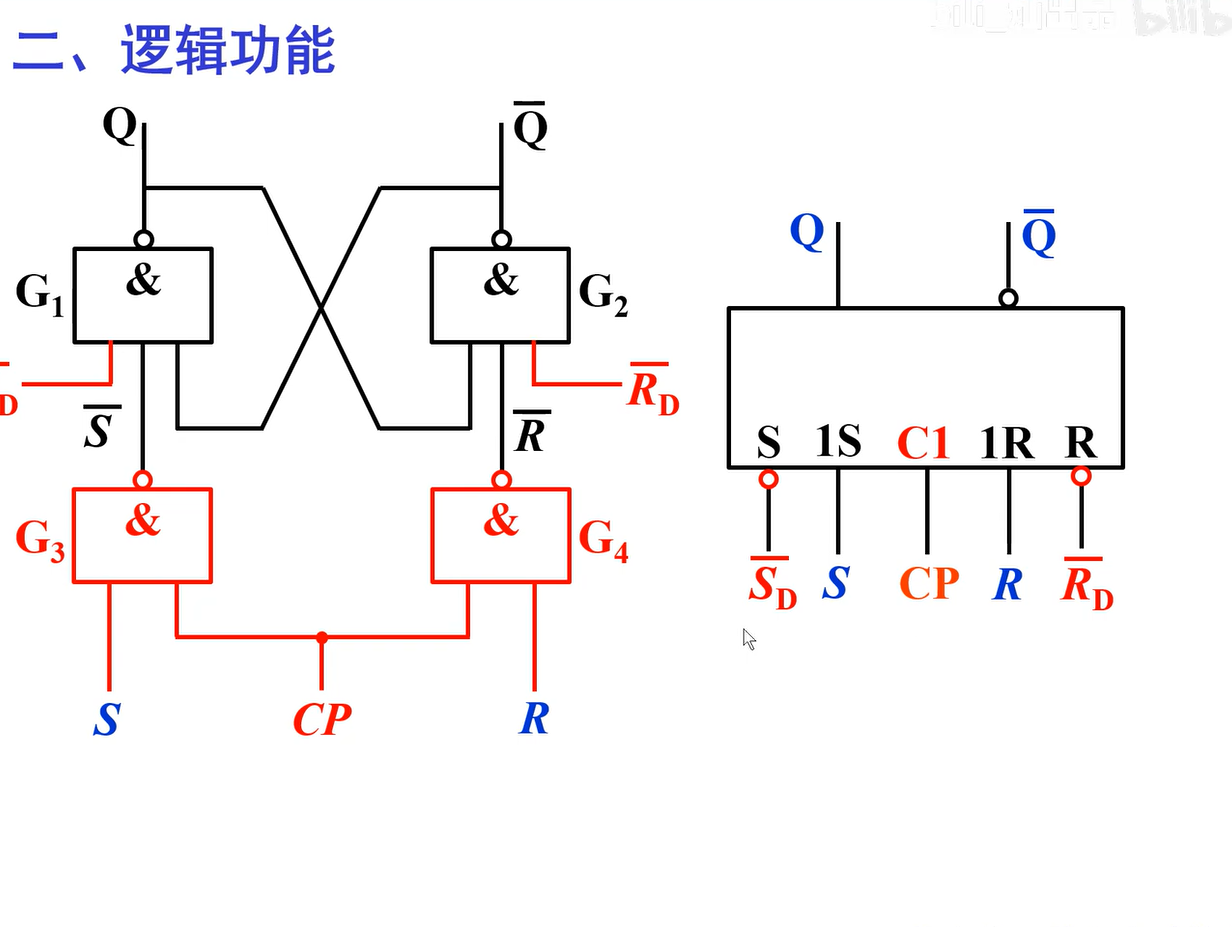

2,逻辑功能

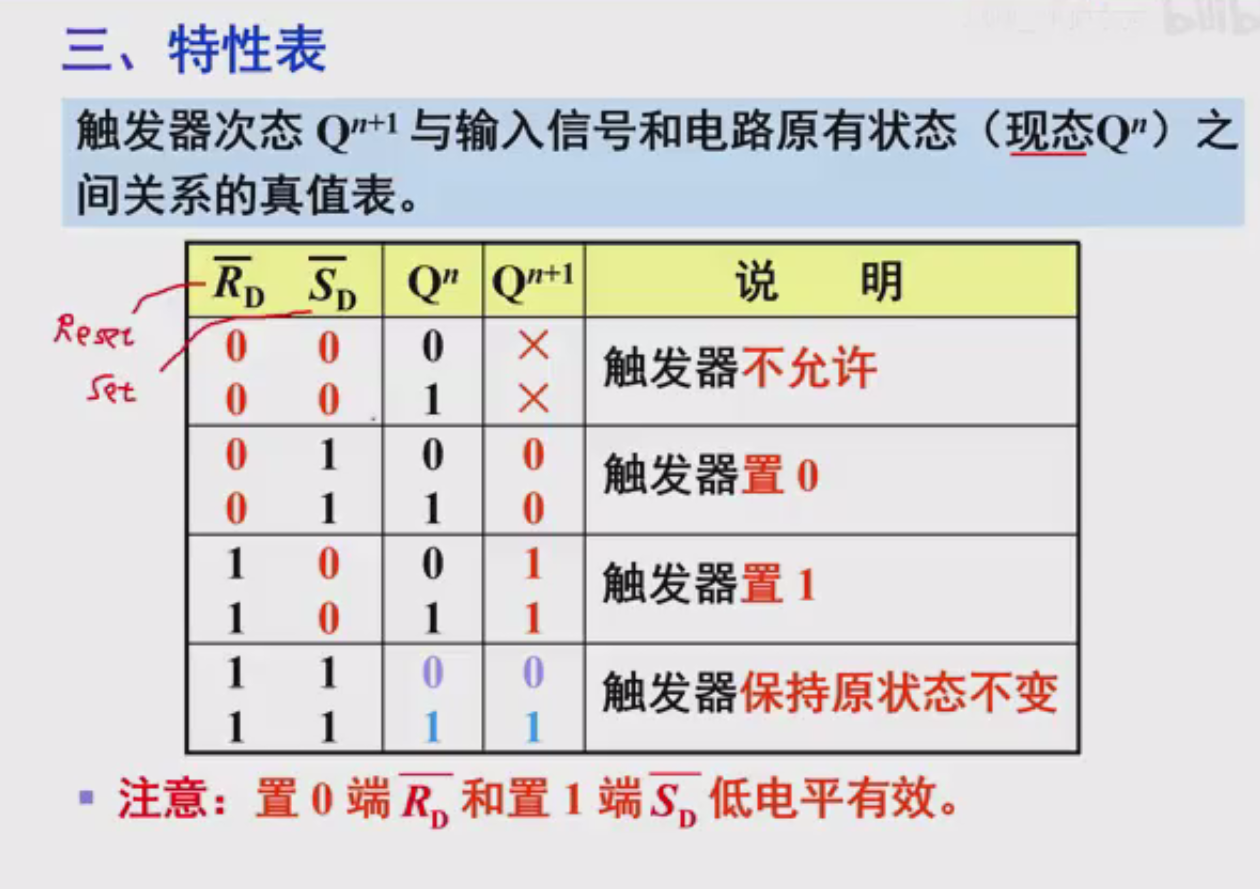

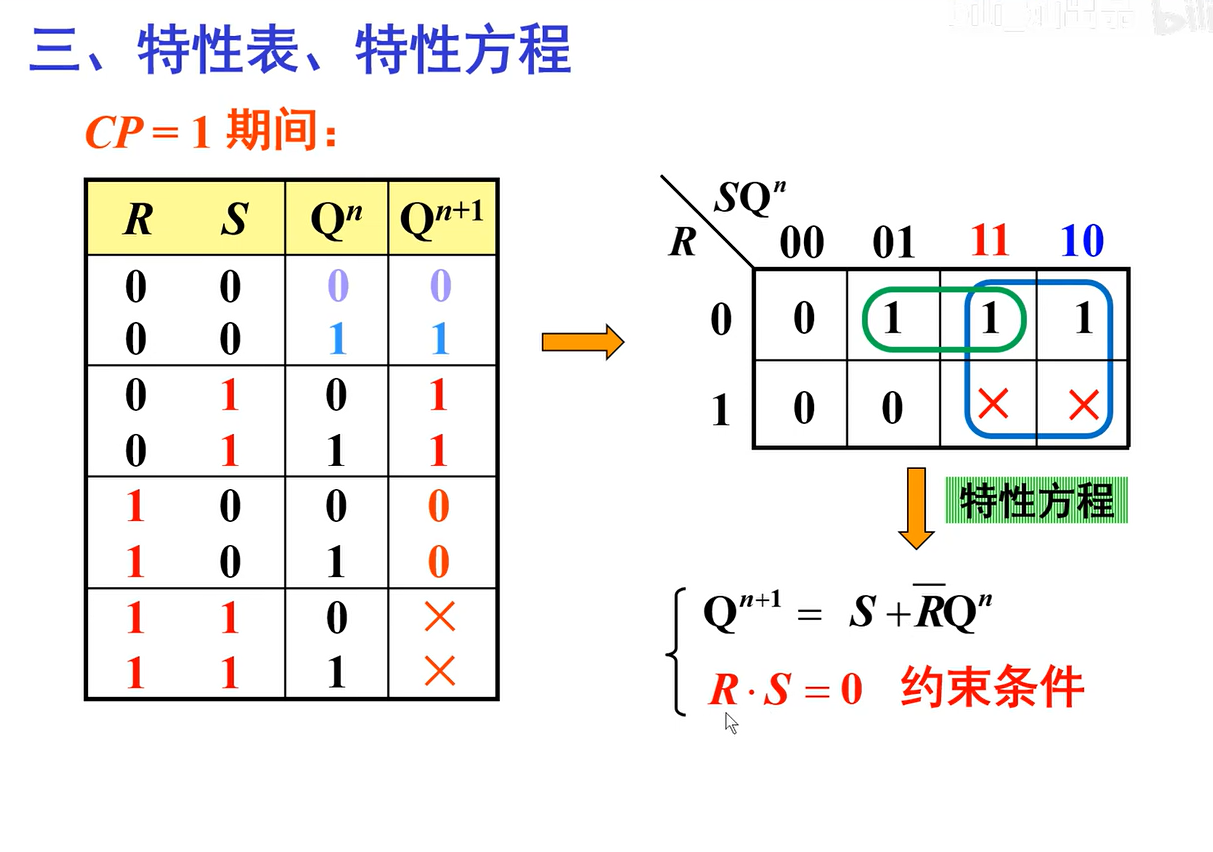

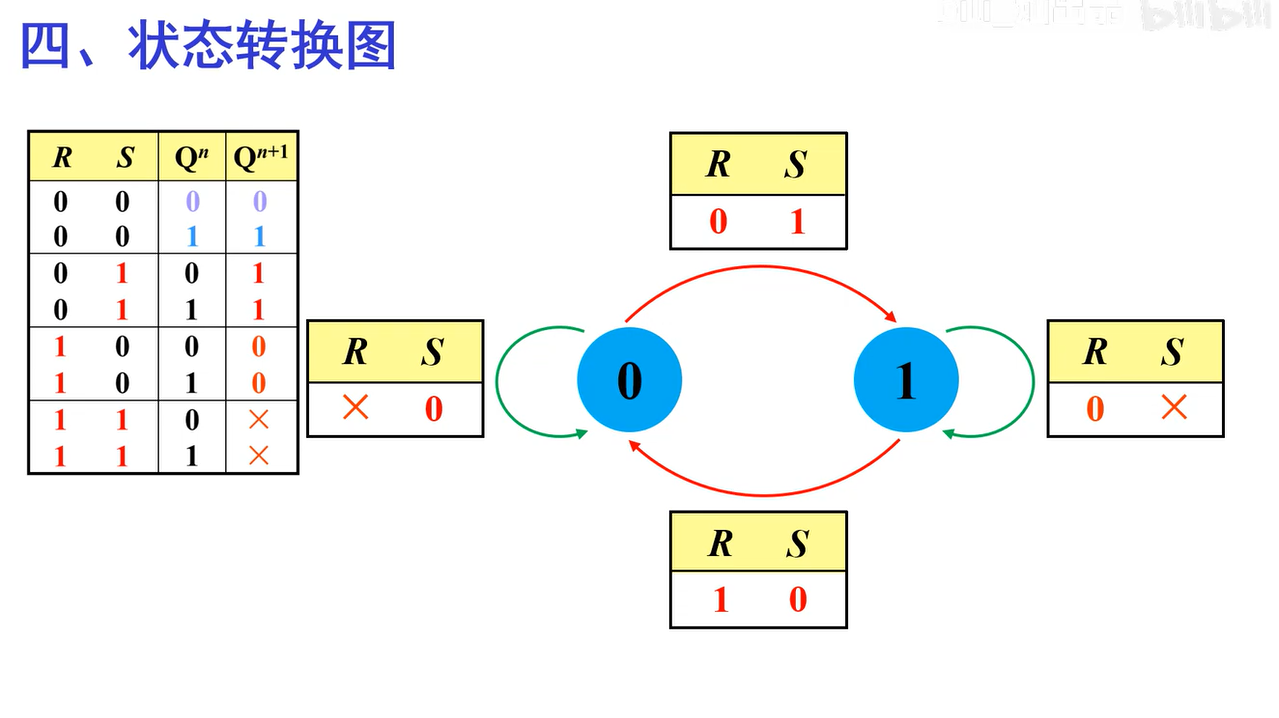

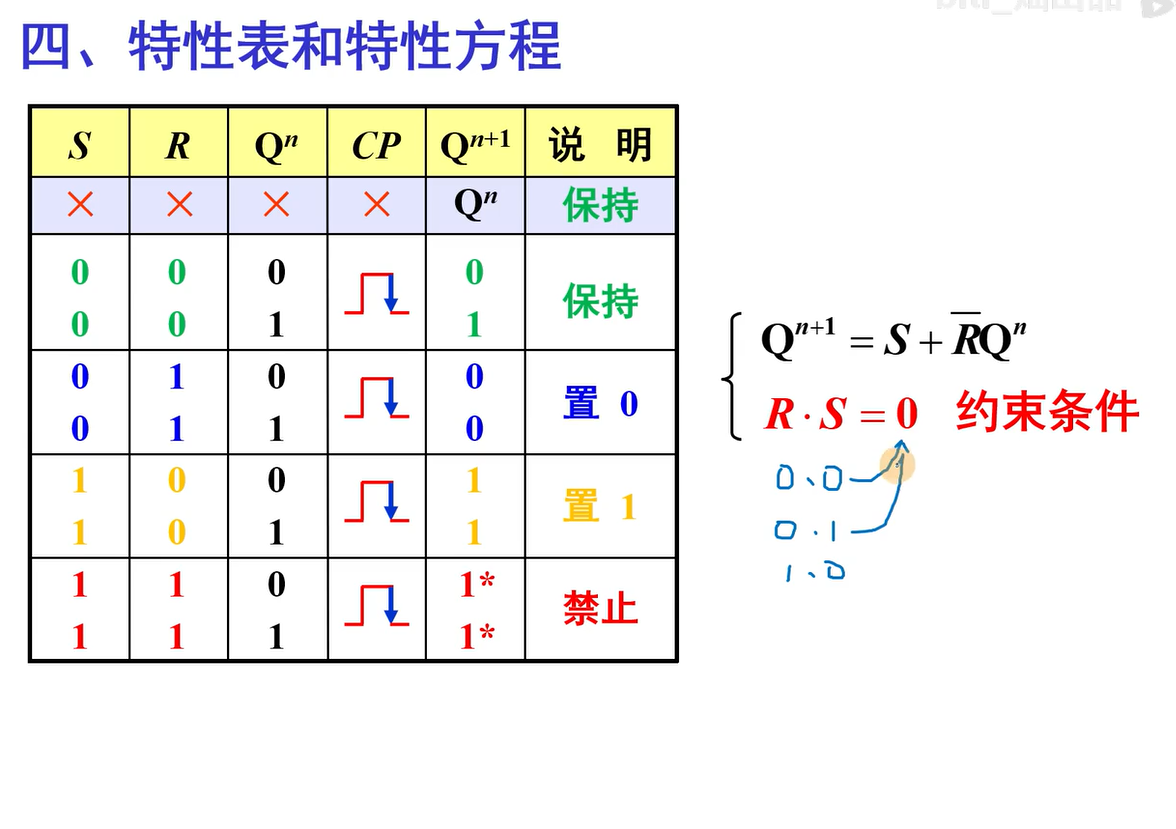

3,特性表

触发器次态Qn+1与输入信号和原有状态Qn之间关系的真值表

-Rs+-Rd=1——约束条件

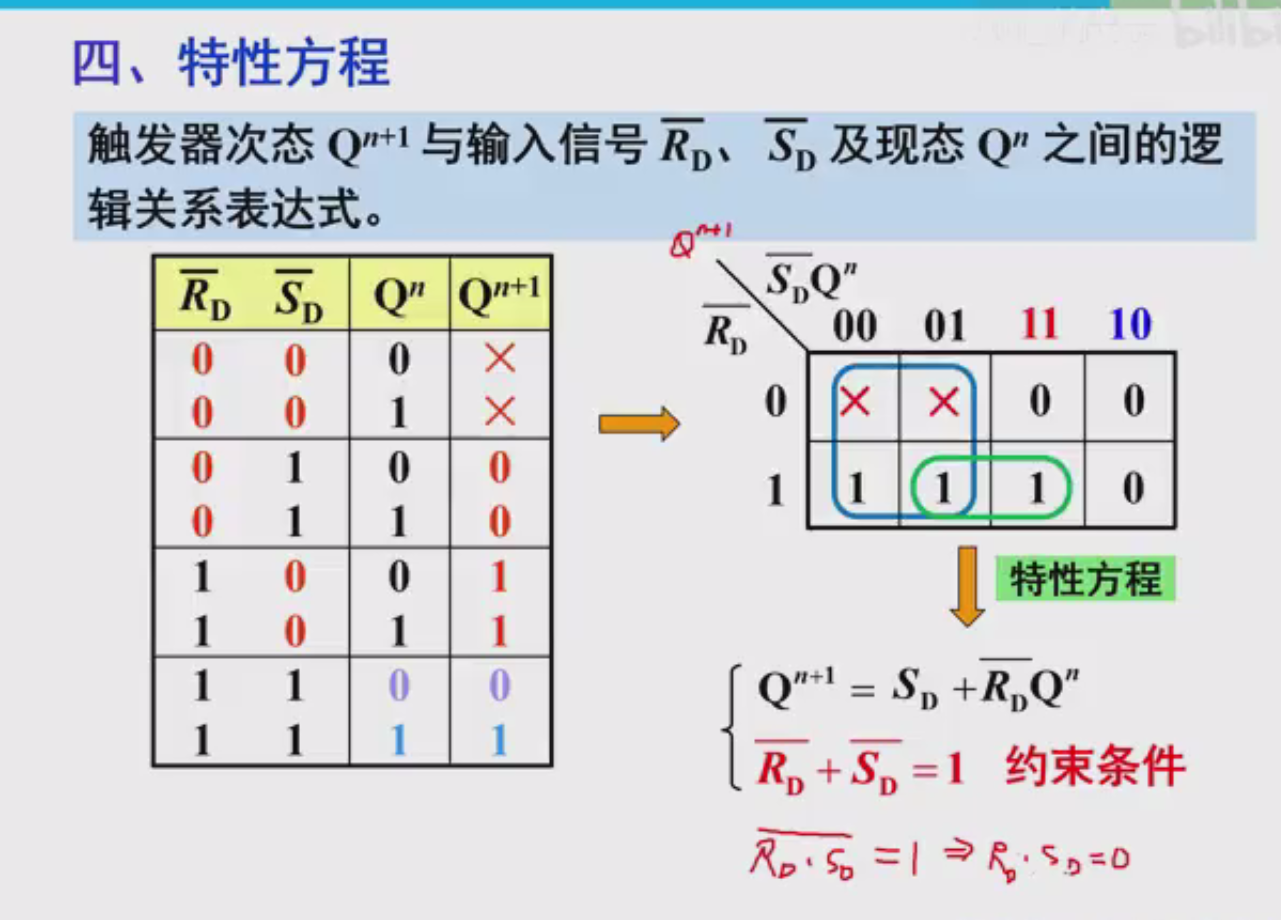

4,特性方程

5,状态转换图

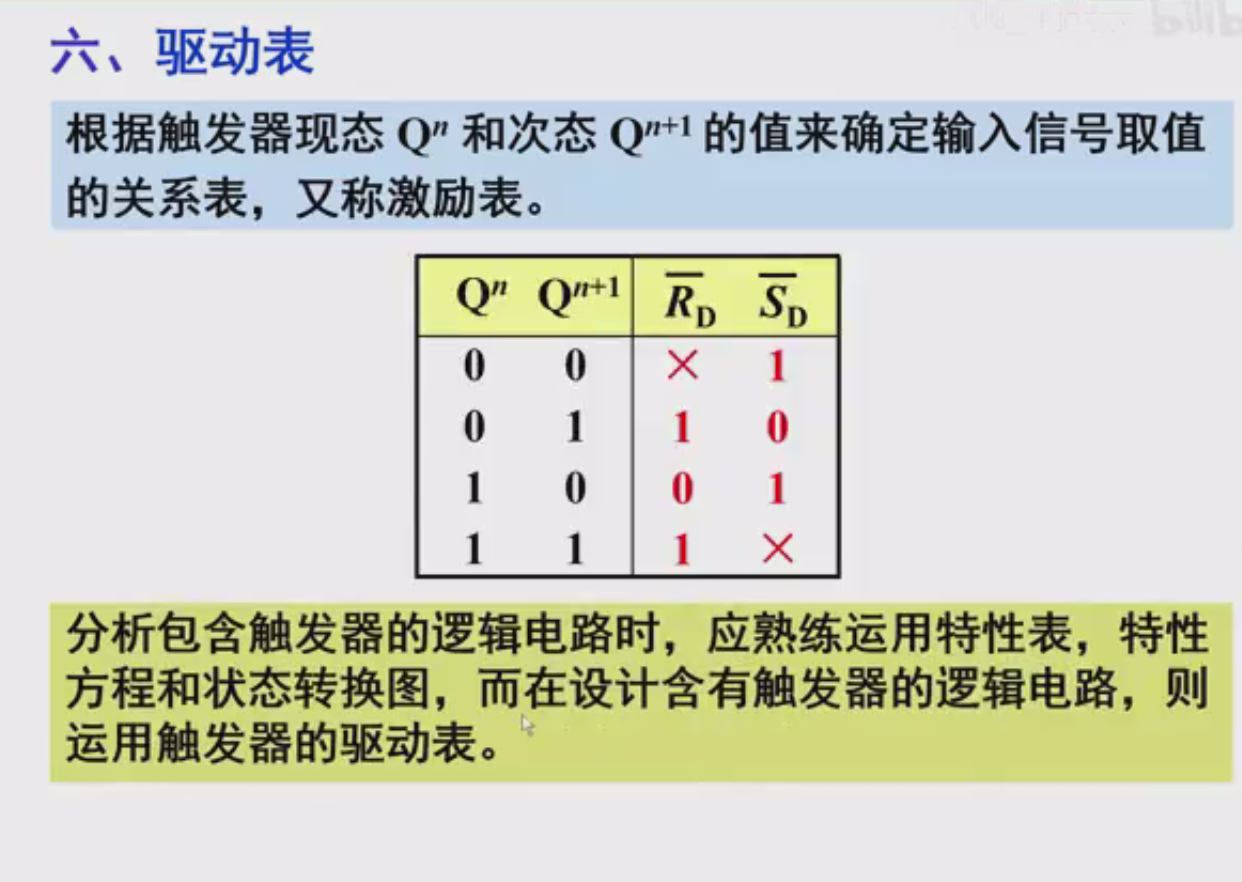

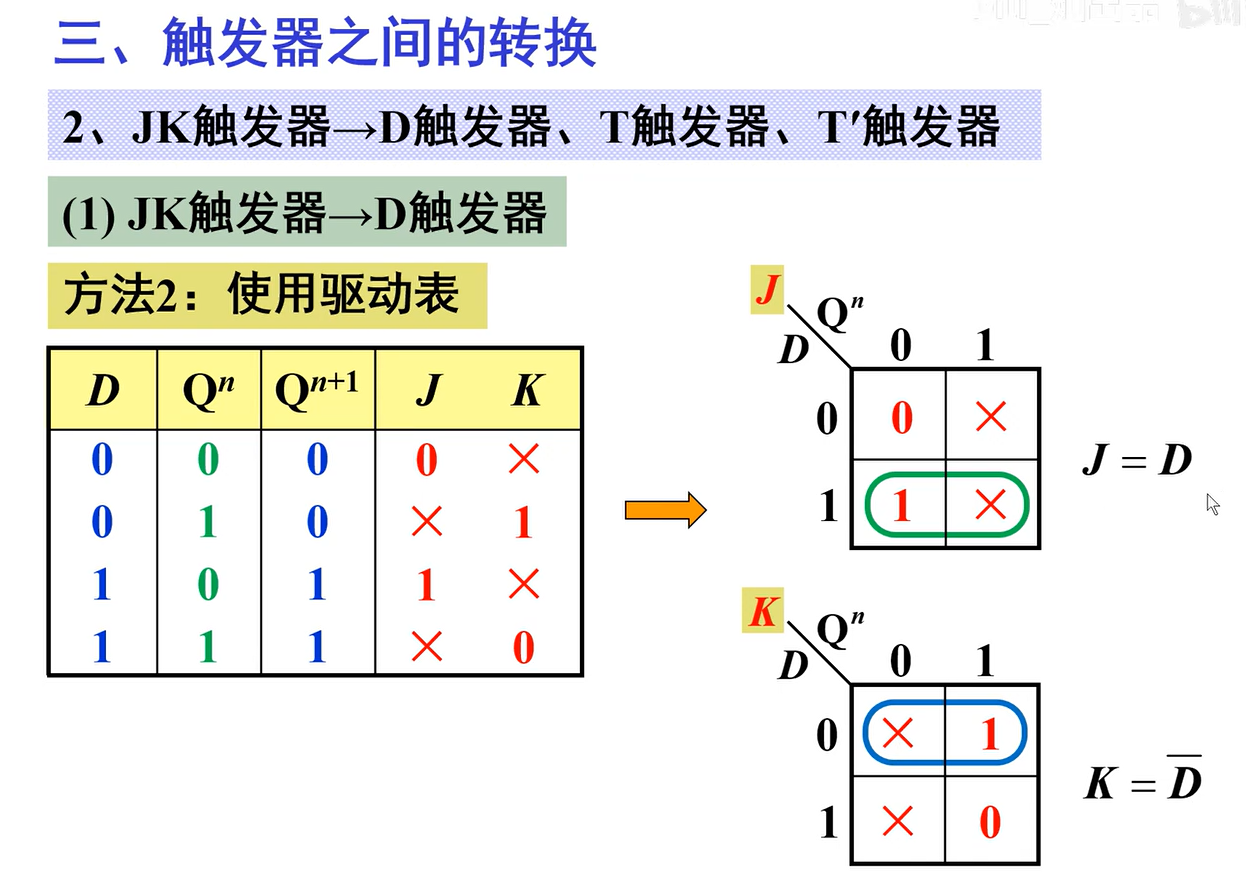

6,驱动表

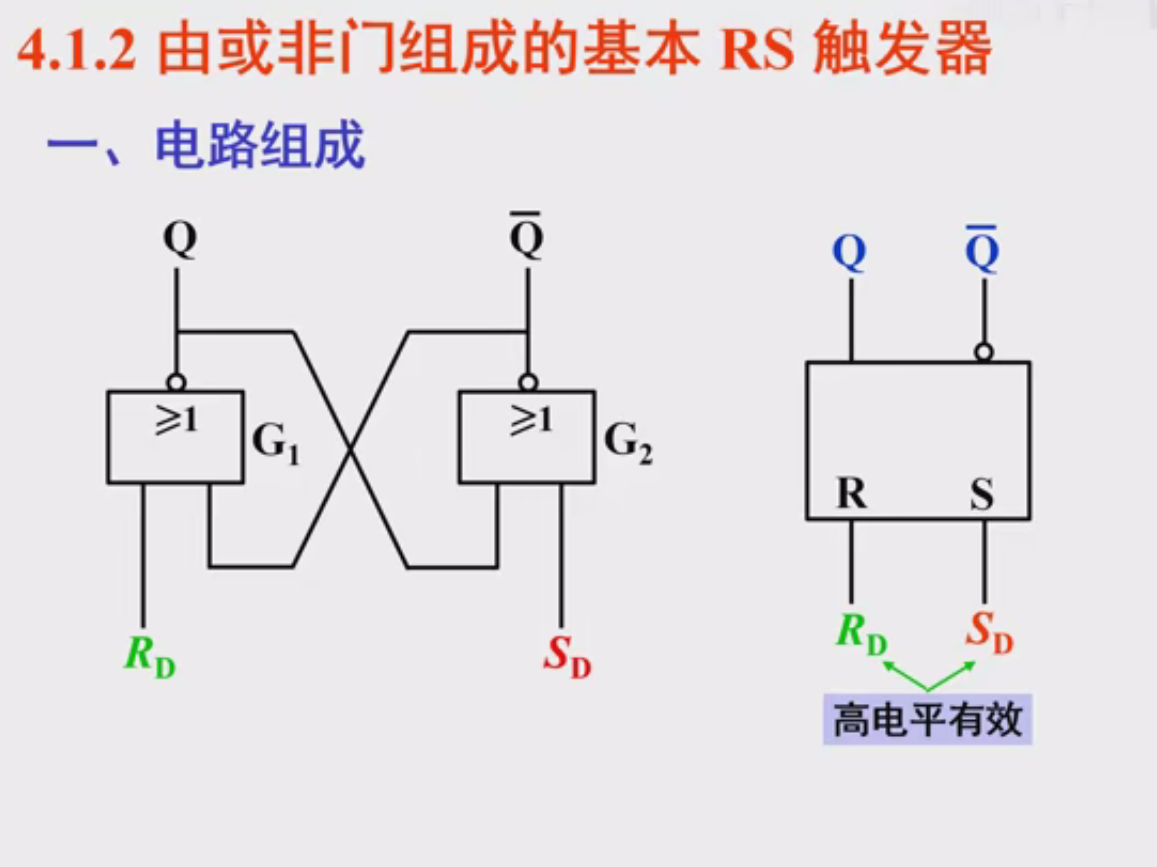

4.1.2有或非门组成的基本RS触发器

1,电路组成

2,逻辑功能

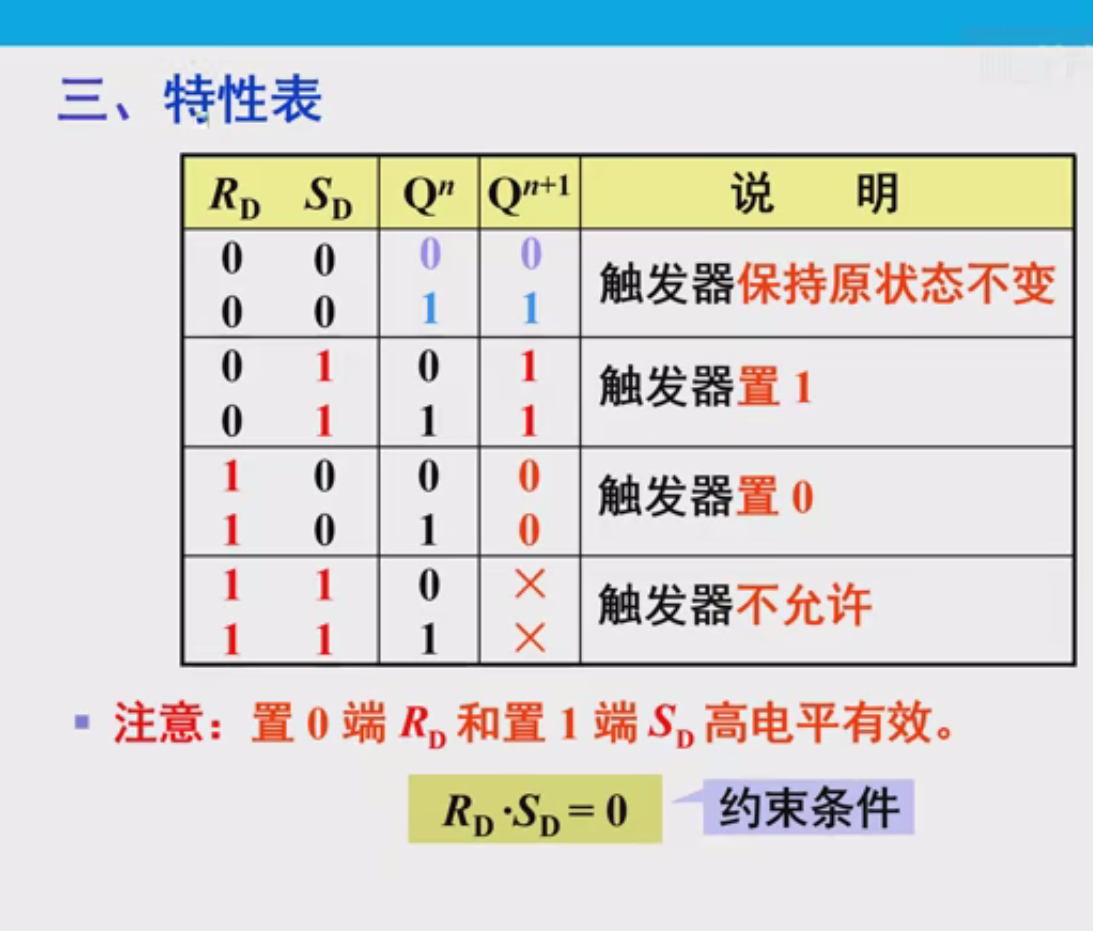

3,特性表

4,特性方程

s

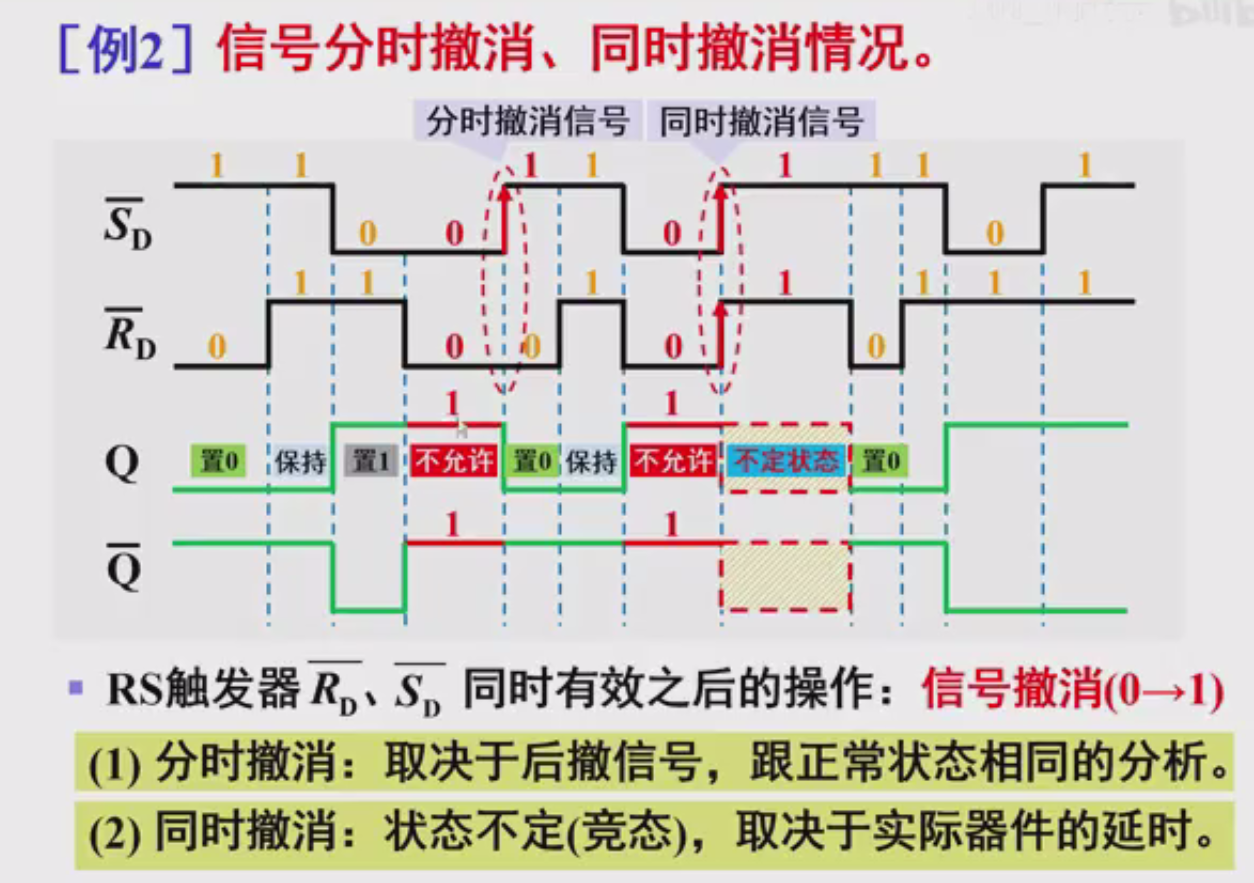

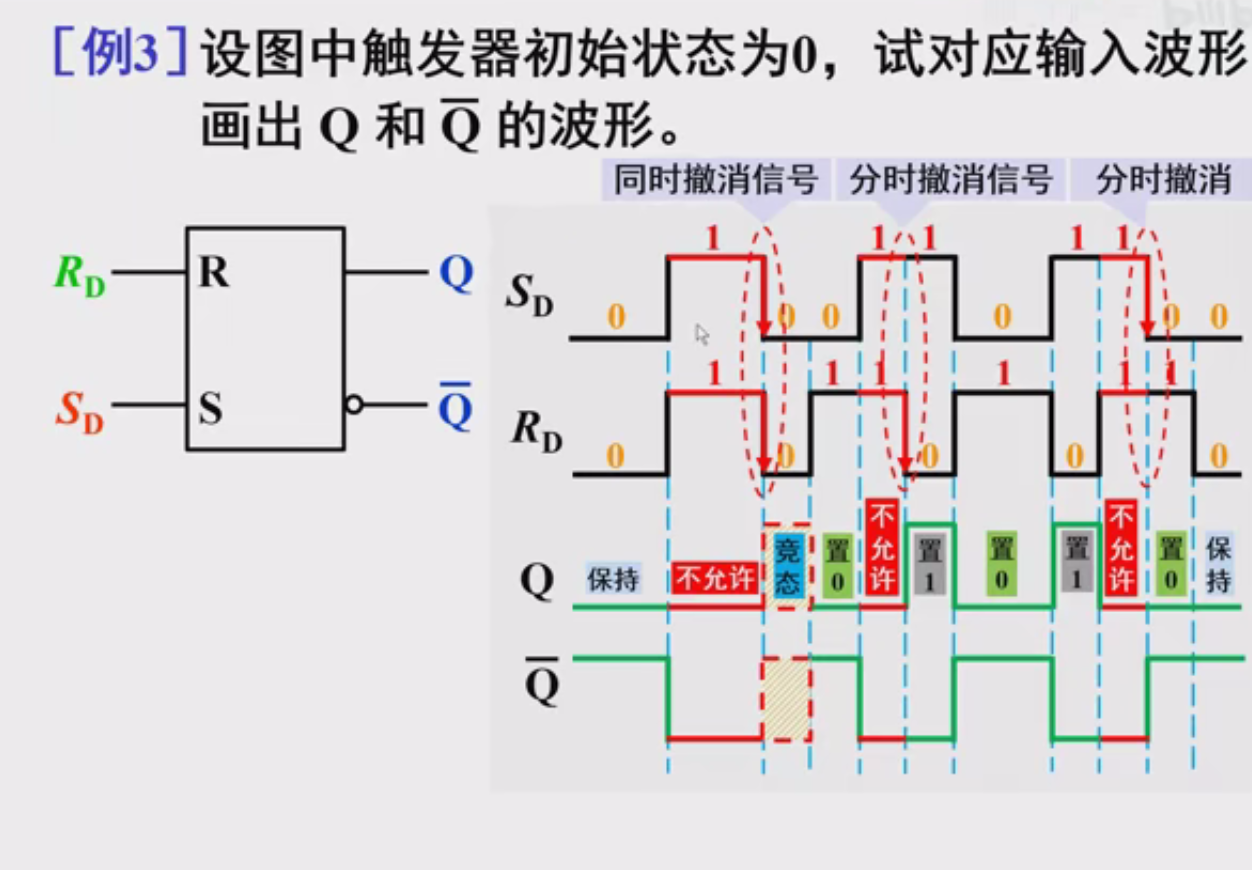

同时为1,撤销

同时撤销/分时撤销

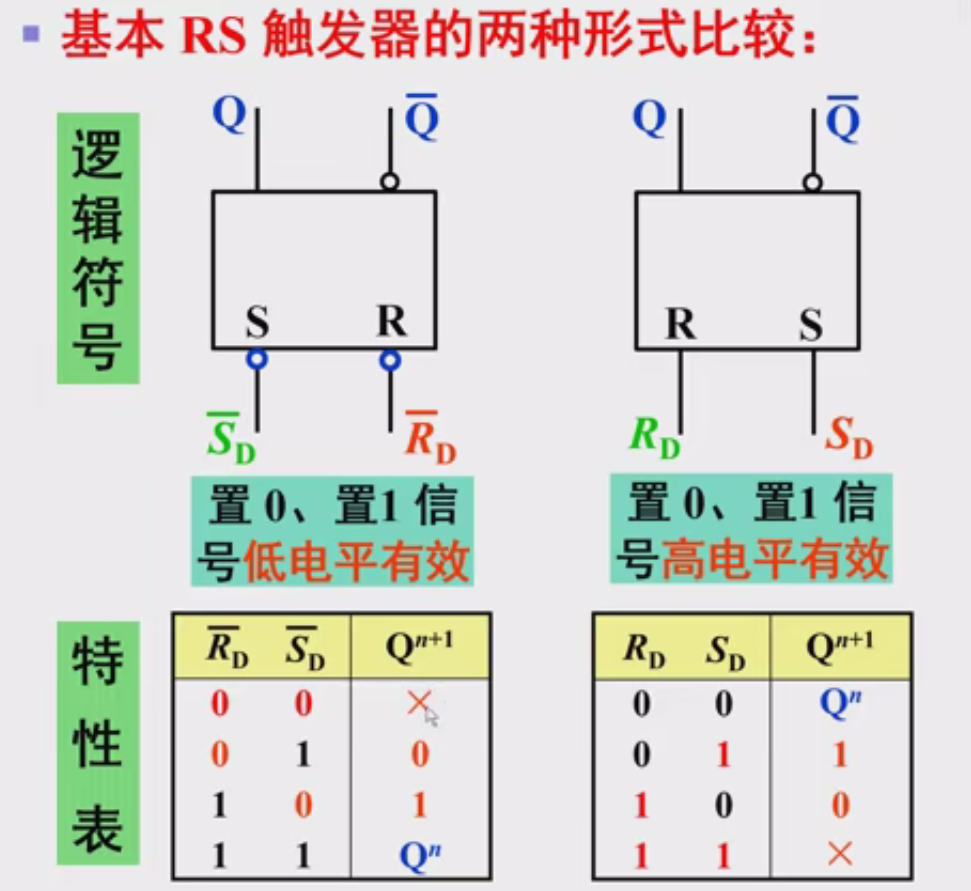

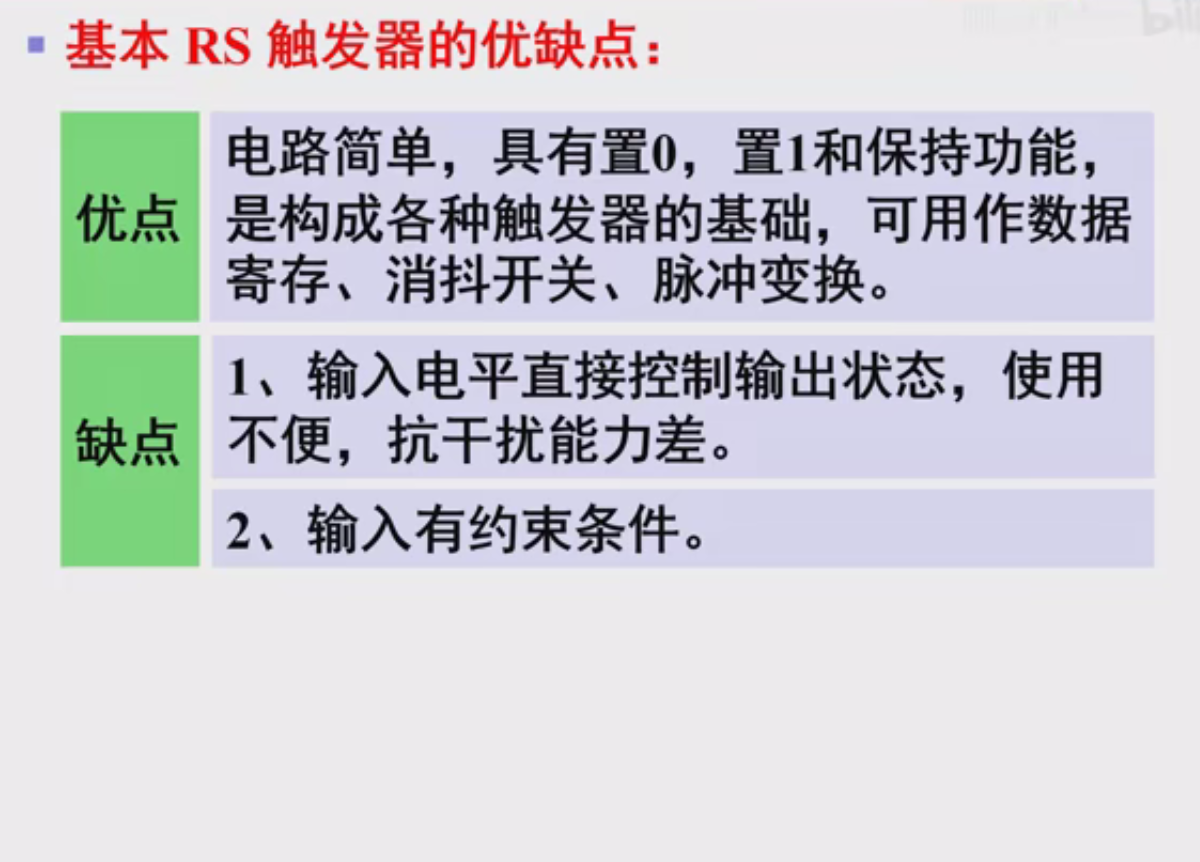

基本触发器的两种形式比较

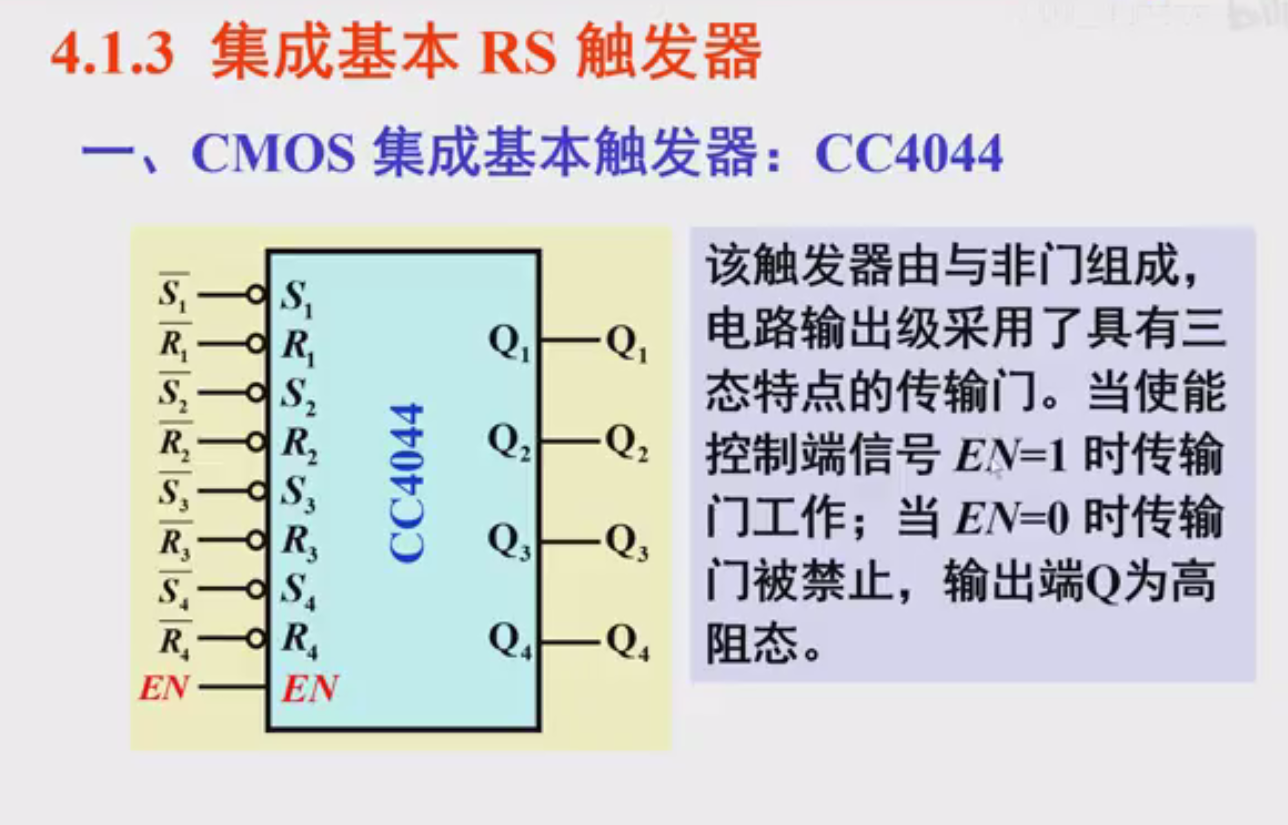

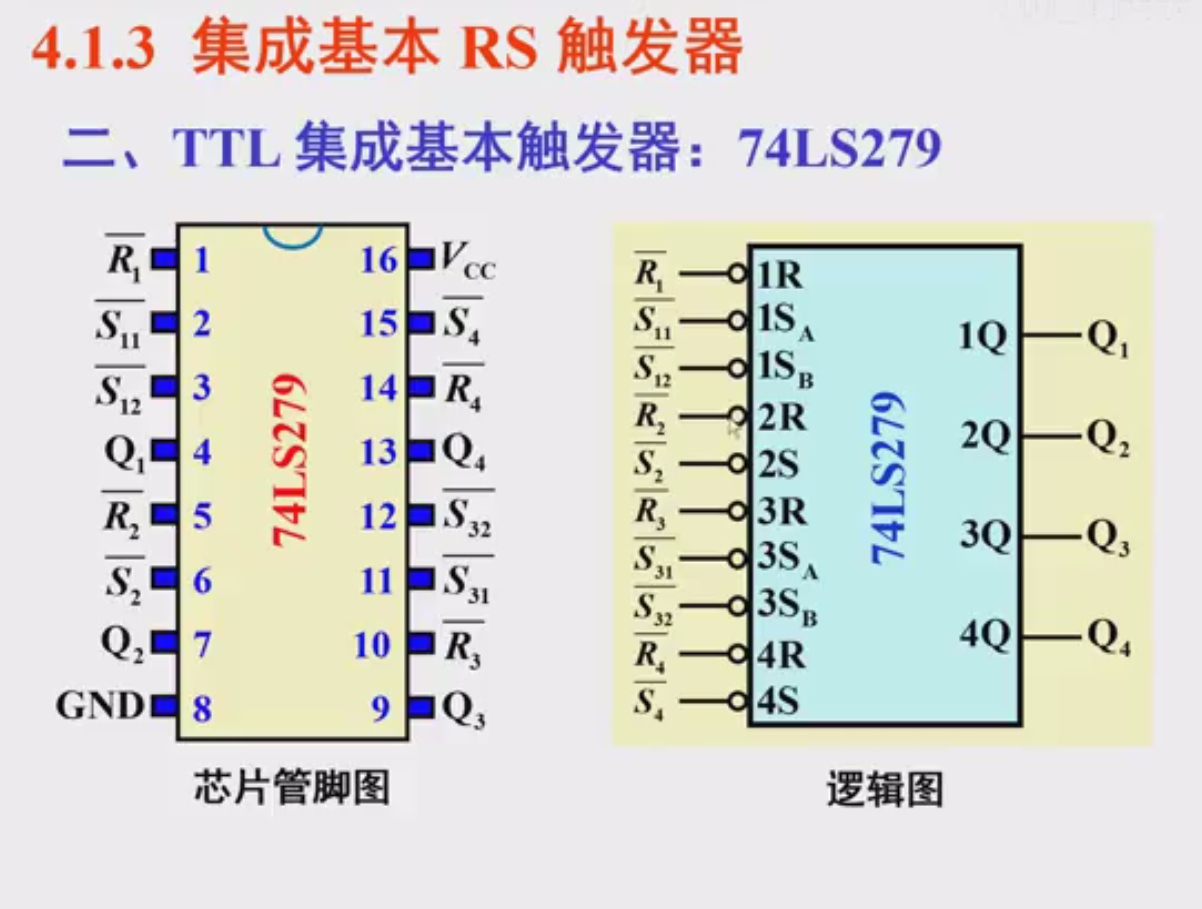

4.1.3集成基本RS触发器

1,CMOS集成基本触发器:CC4044

2,TTL集成基本触发器:74LS279

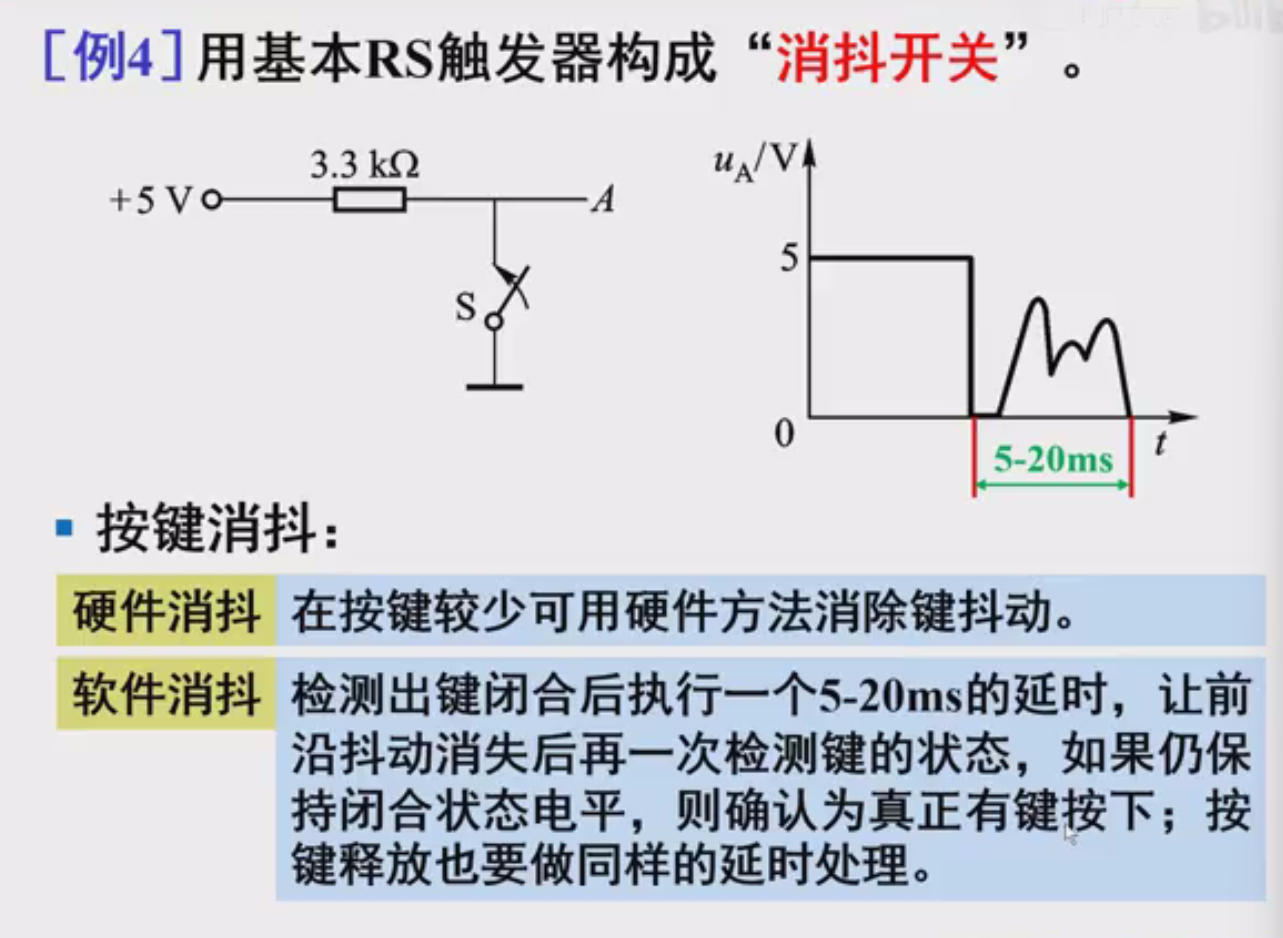

消抖开关

按键一般是机械弹性开关,当触点断开,闭合时,由于弹性作用,抖动导致实际产生的“按下”有多次

按键消抖:

抖动时间由其机械特性决定,在做按键检测时都要加一个消抖操作

硬件消抖:/软件消抖

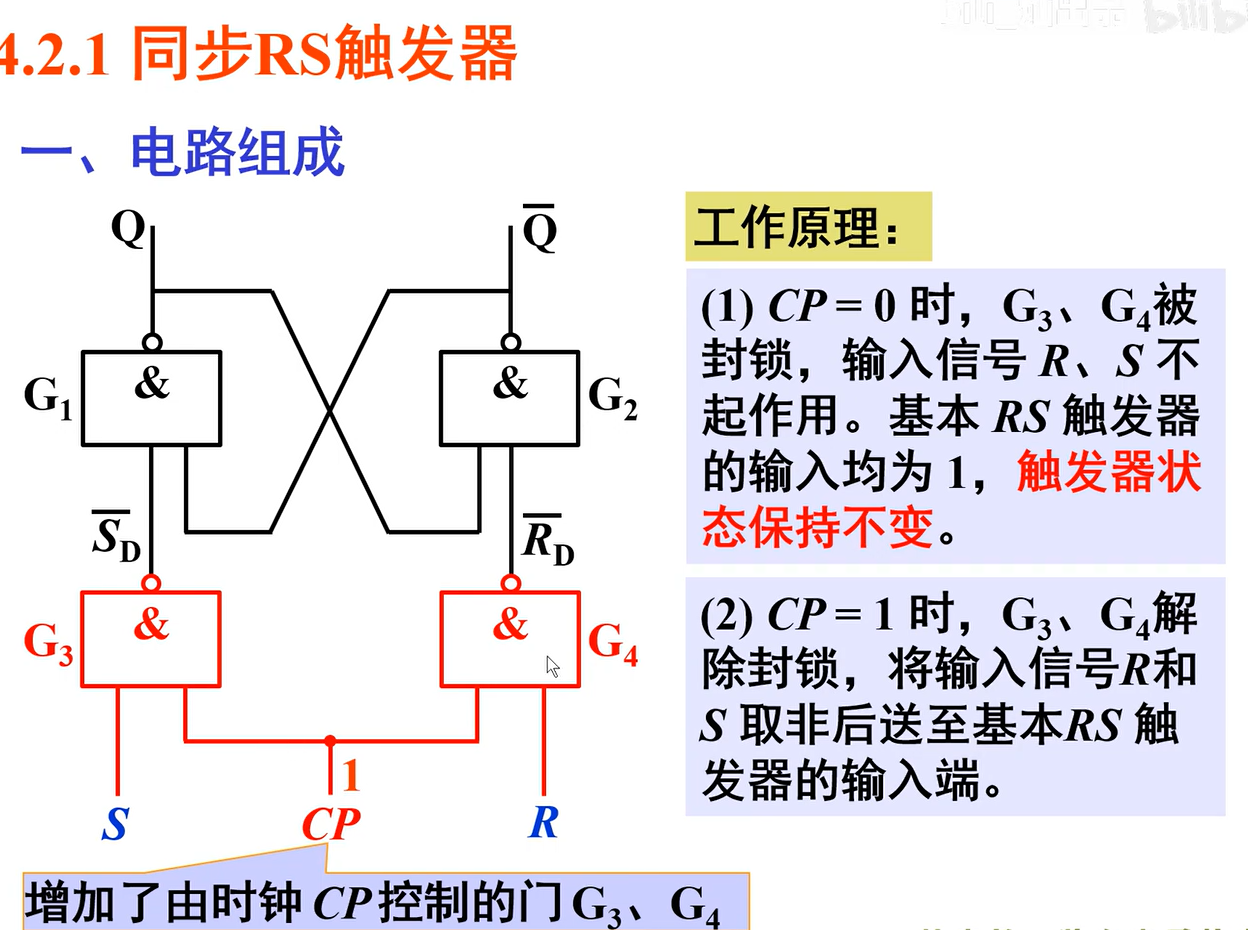

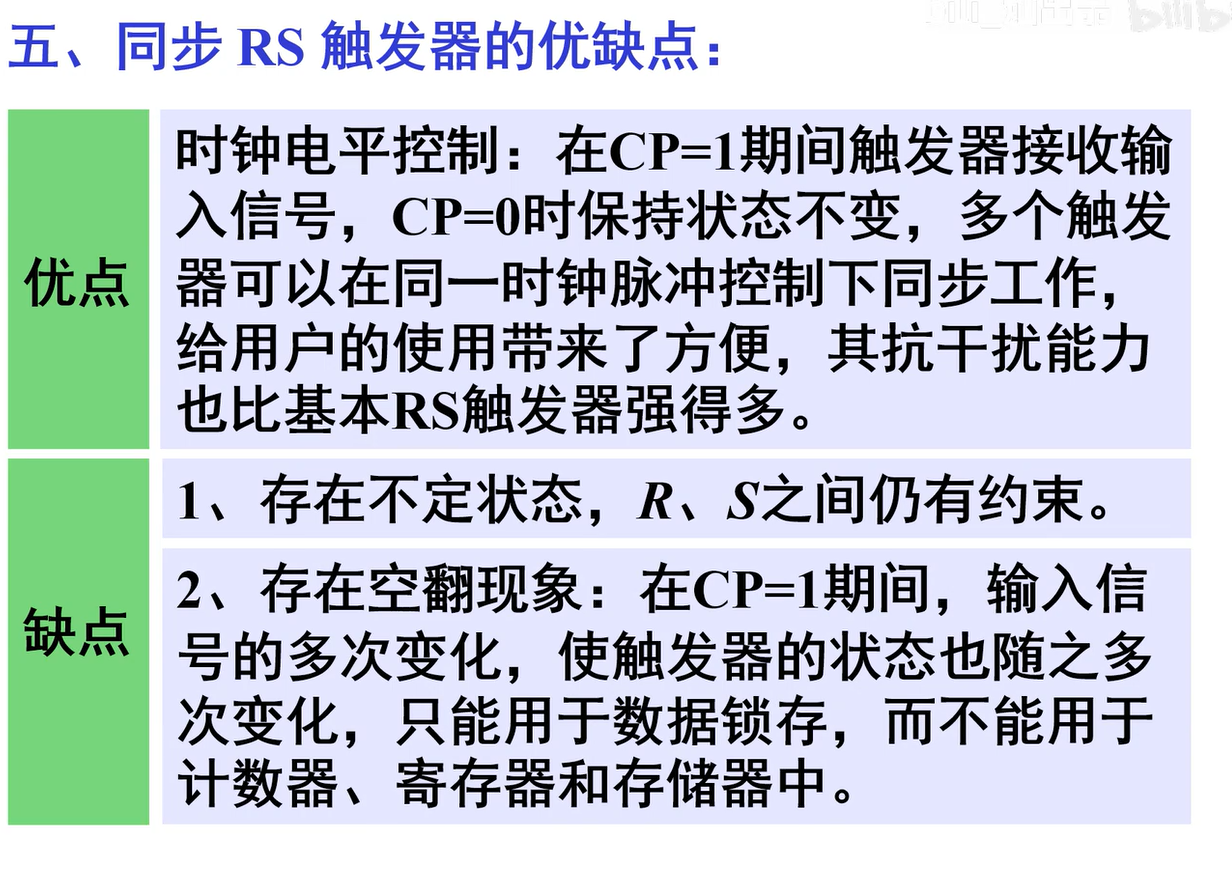

4.2 同步触发器

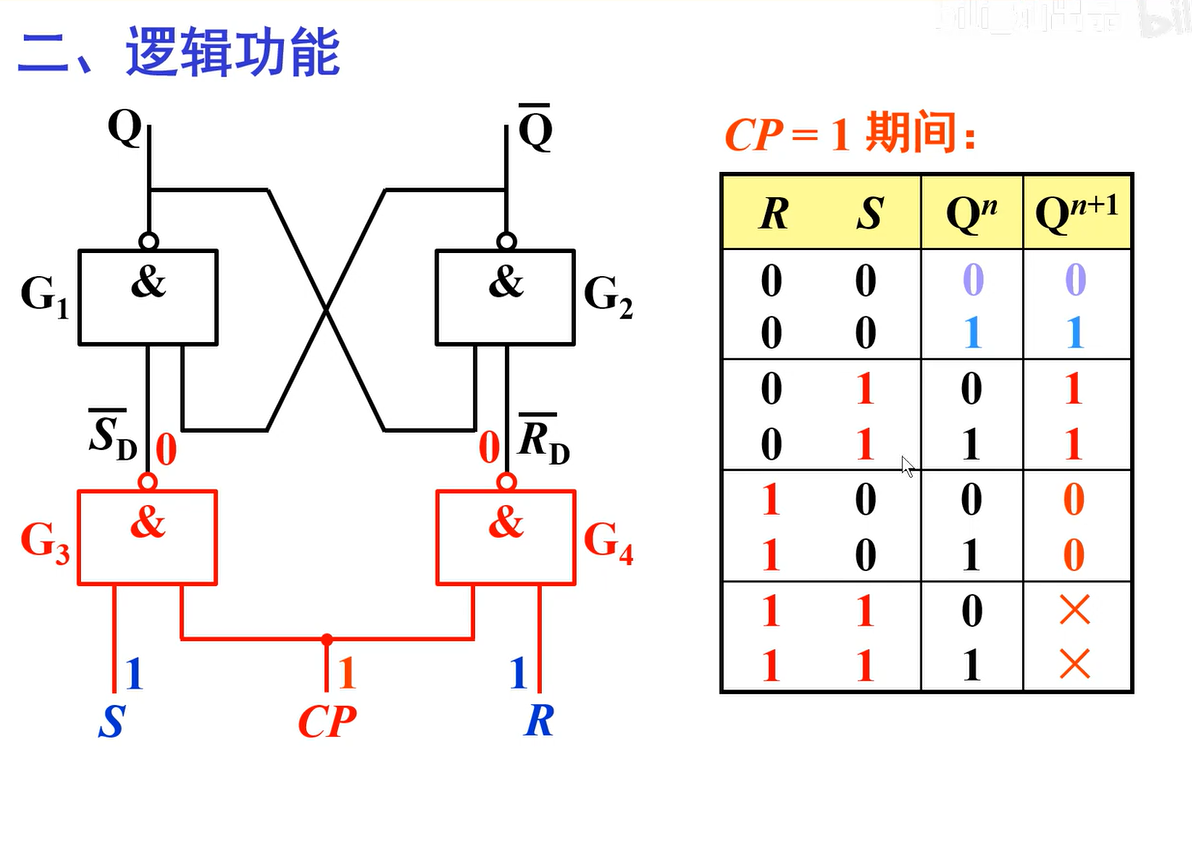

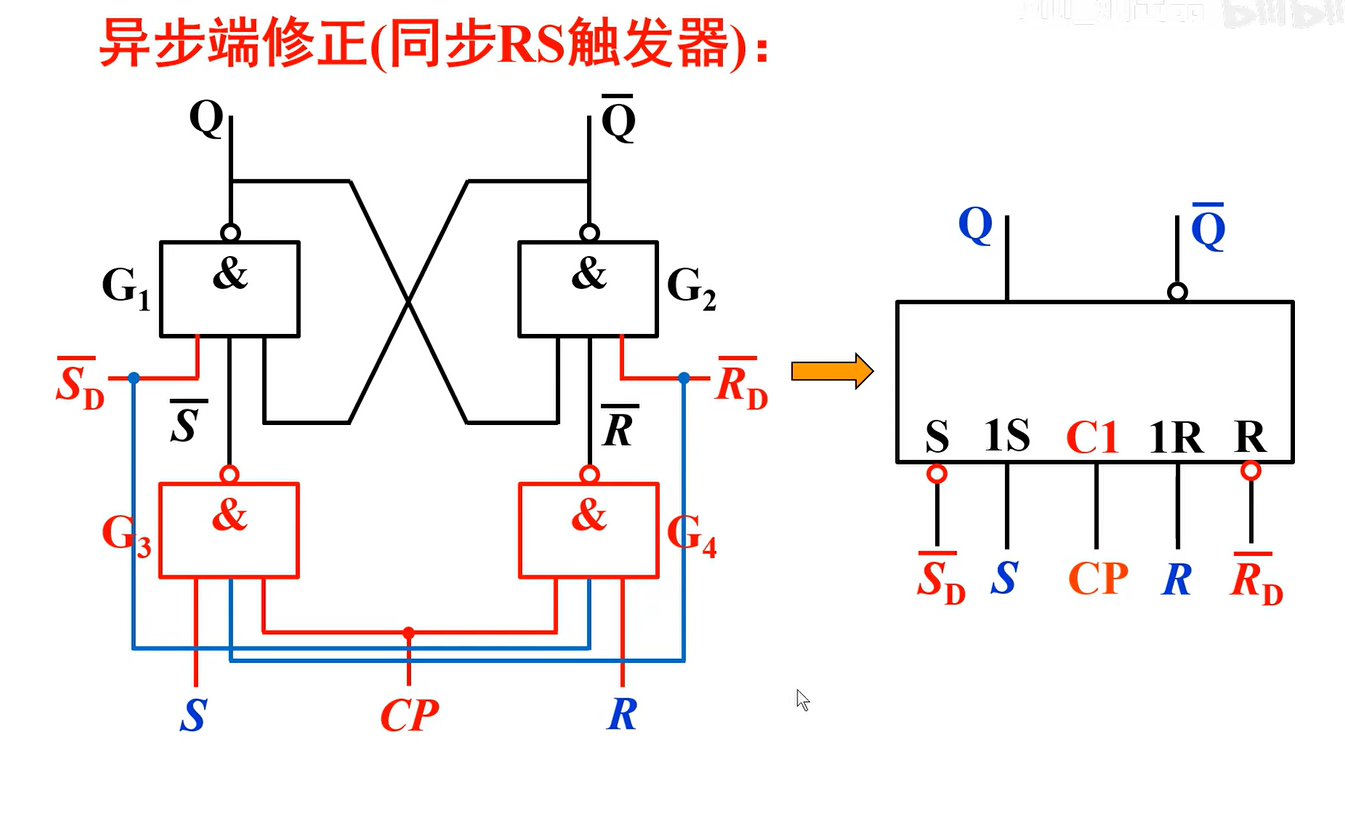

4.2.1 同步RS触发器

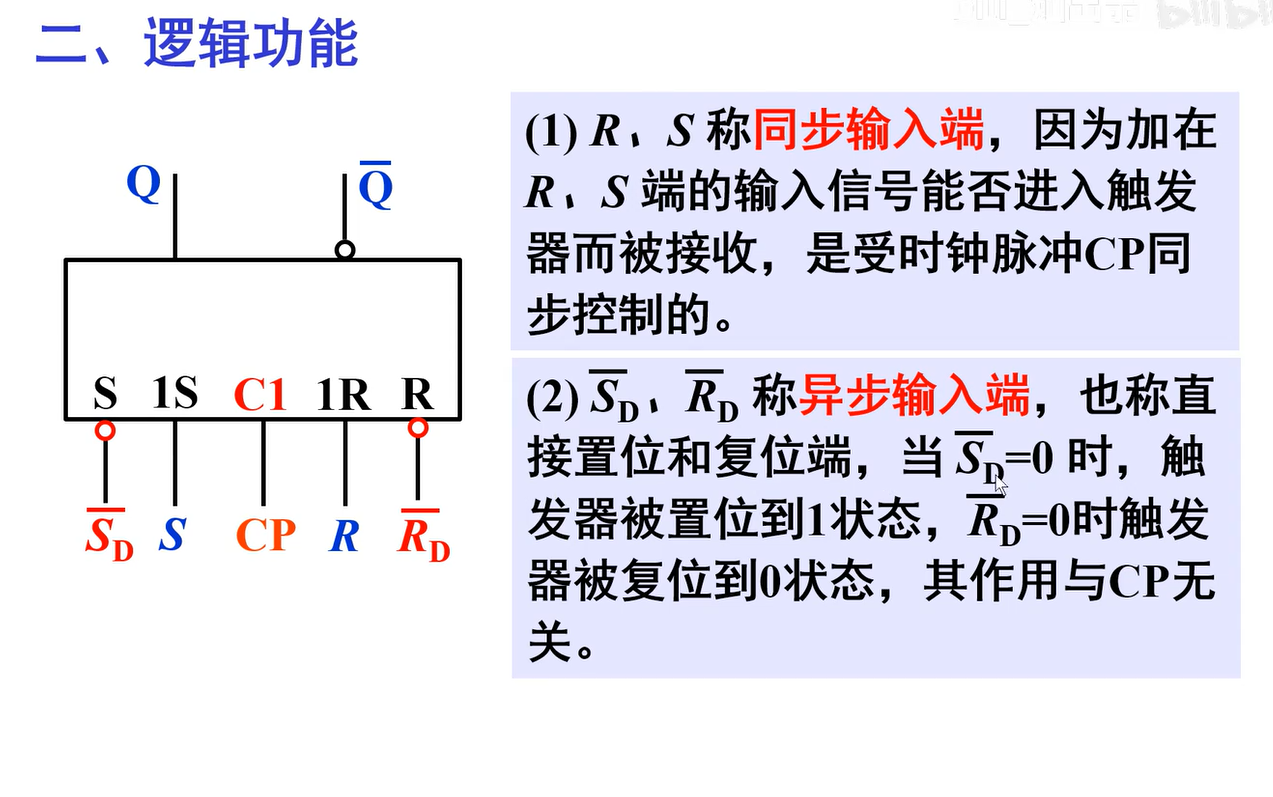

逻辑功能:

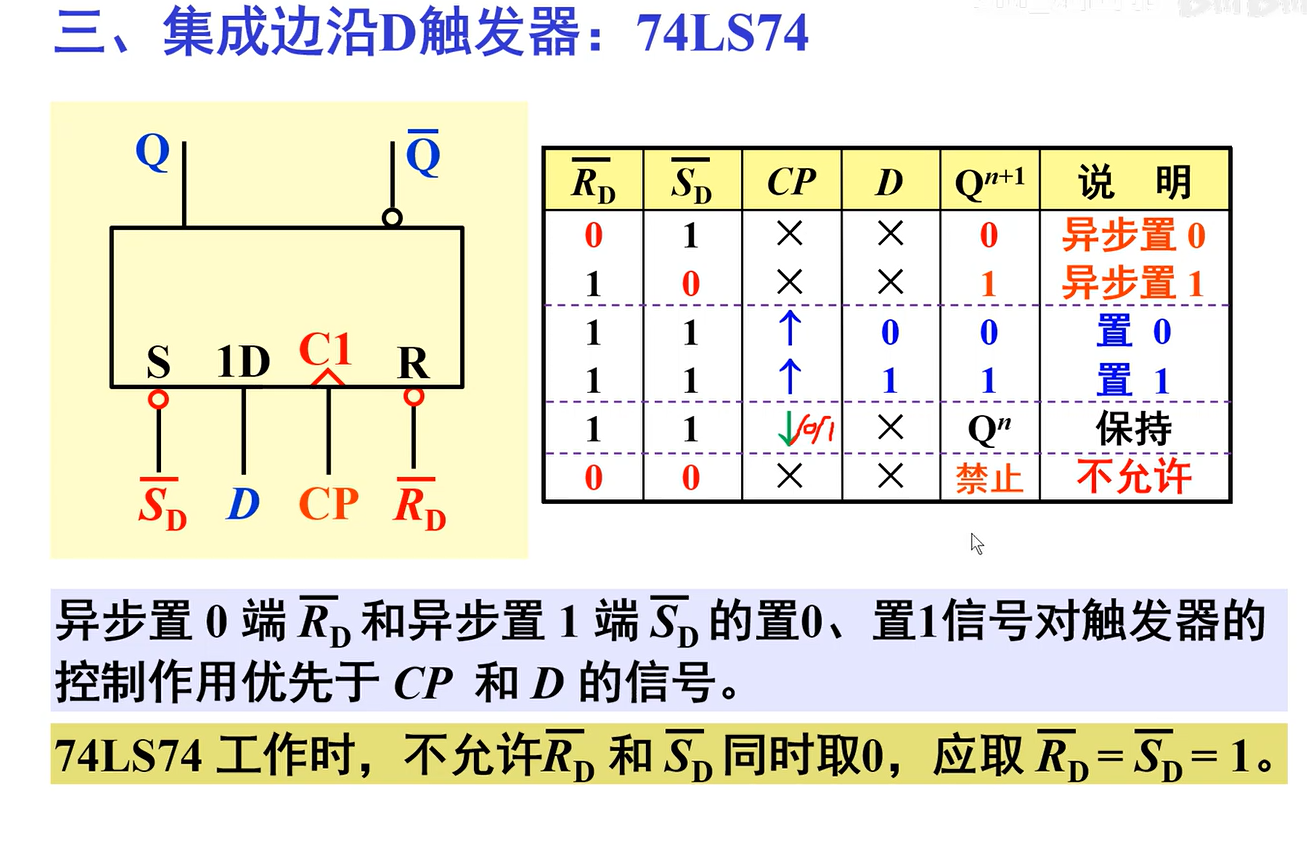

异步输入端用来预制触发器的初始状态,或在工作过程中强行置位和复位触发器

以上CP=1期间有效

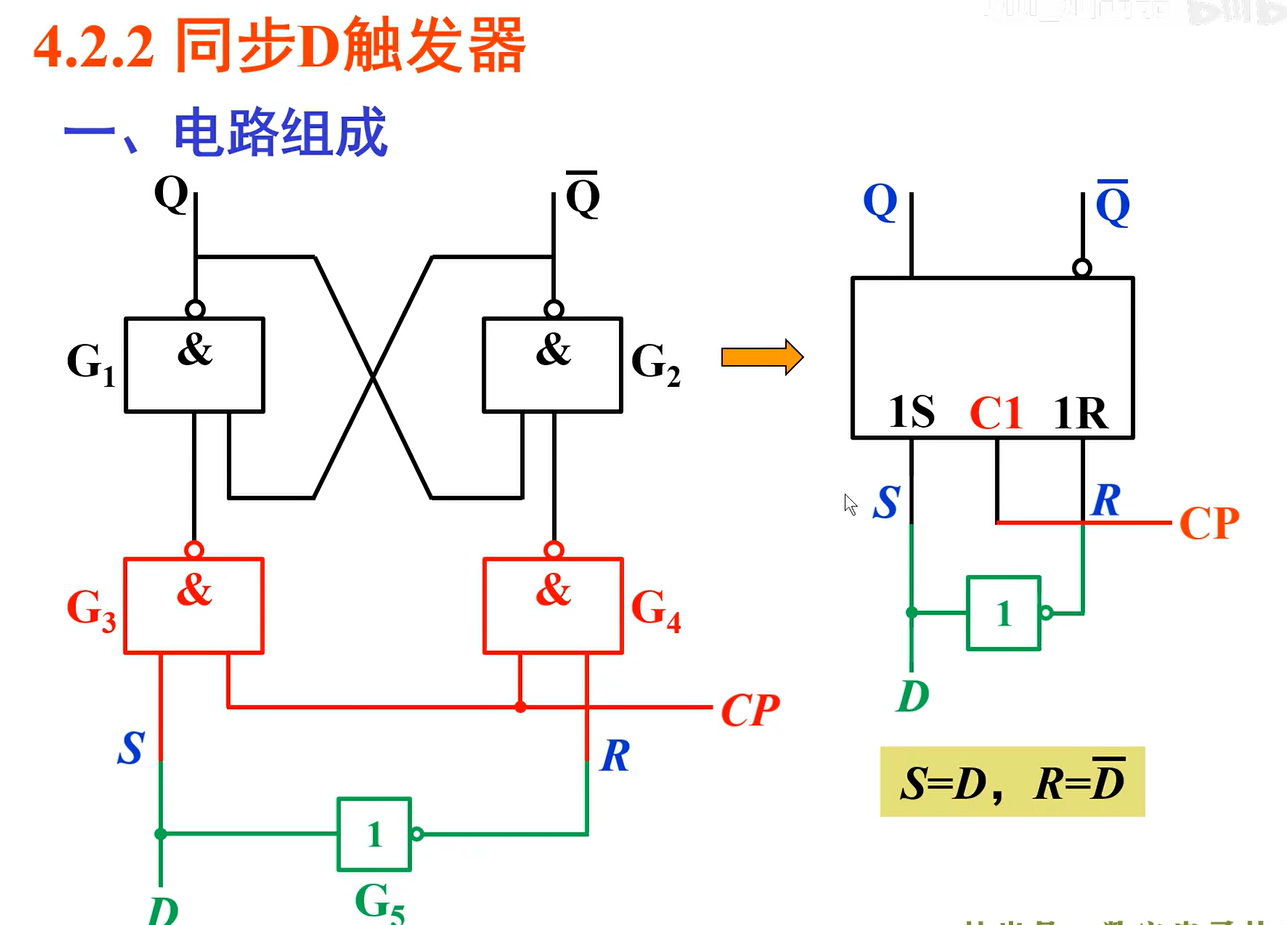

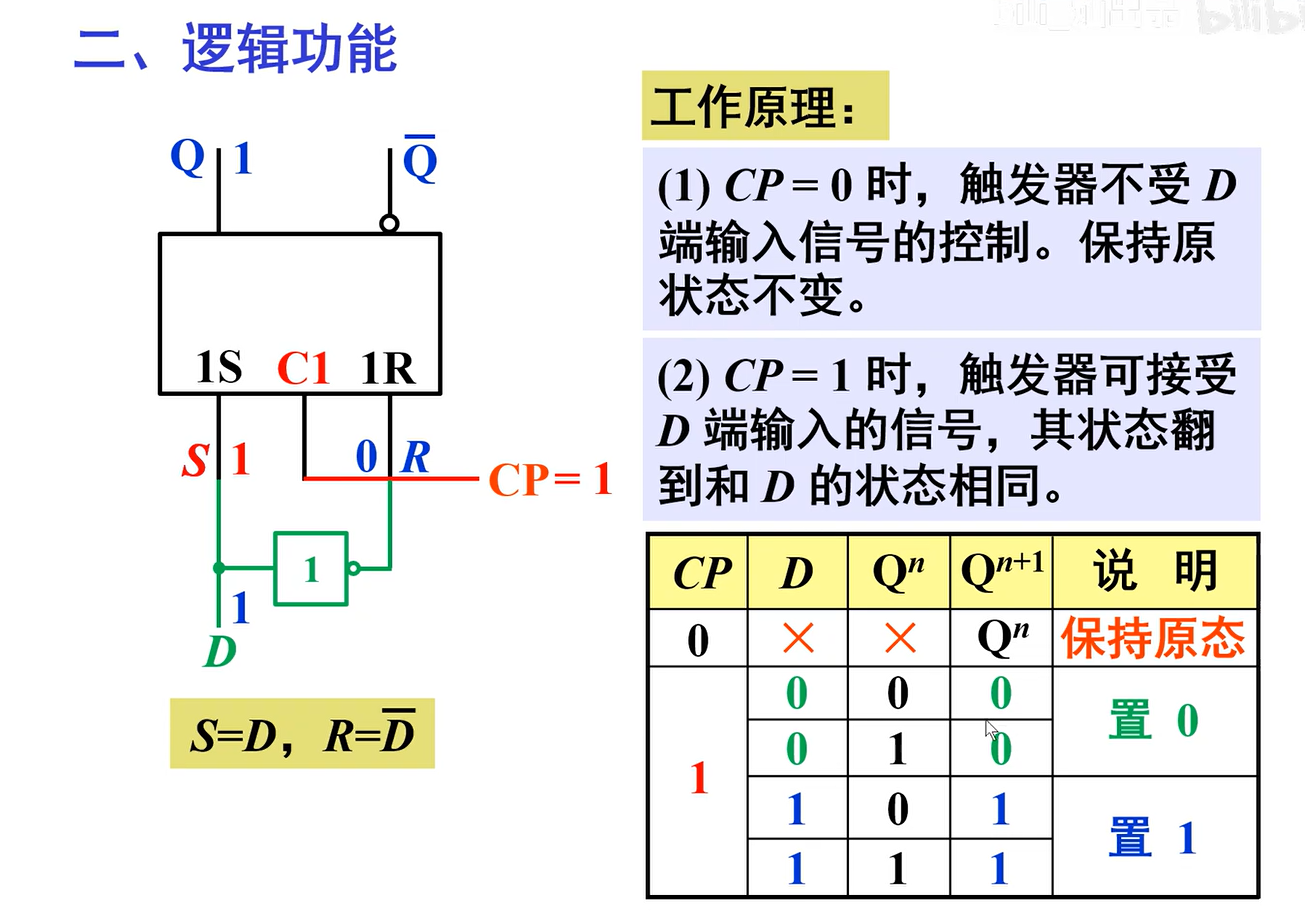

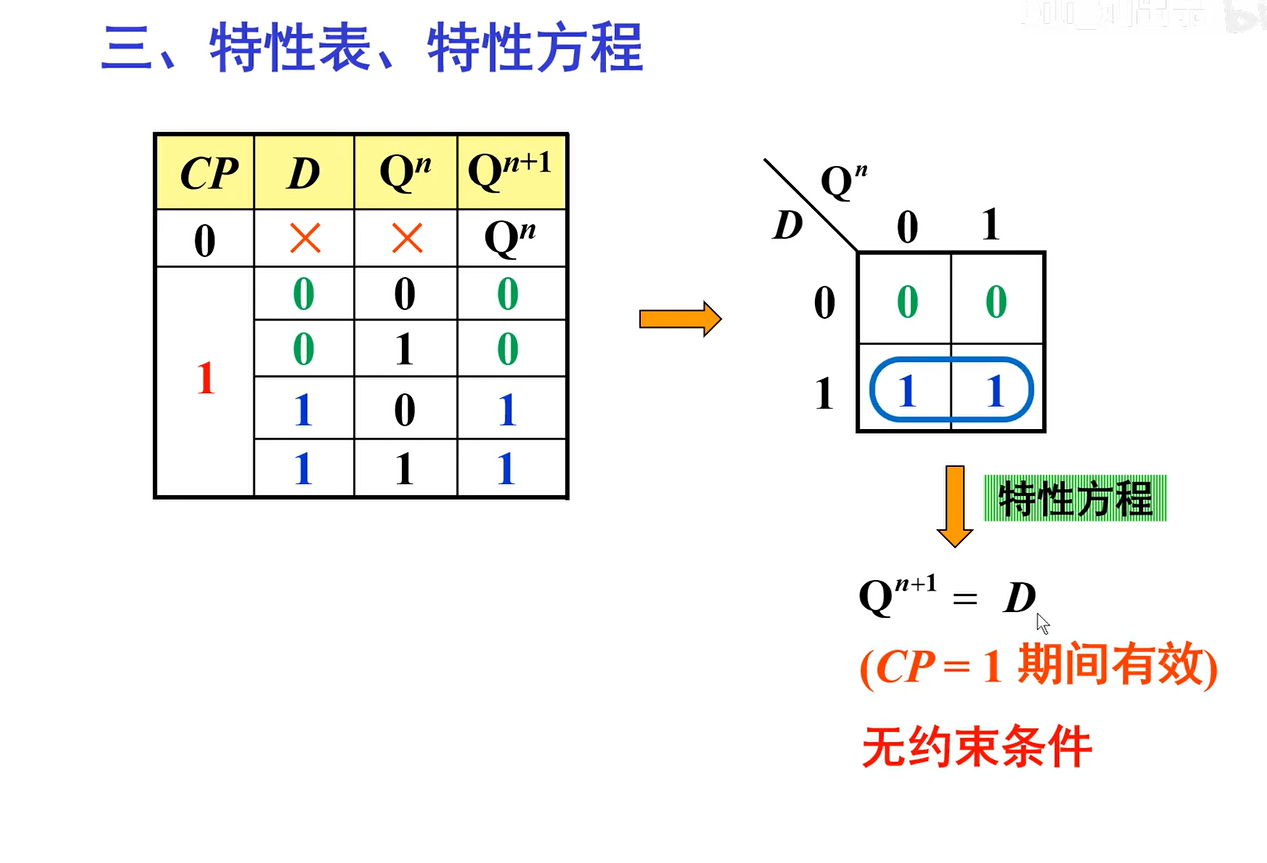

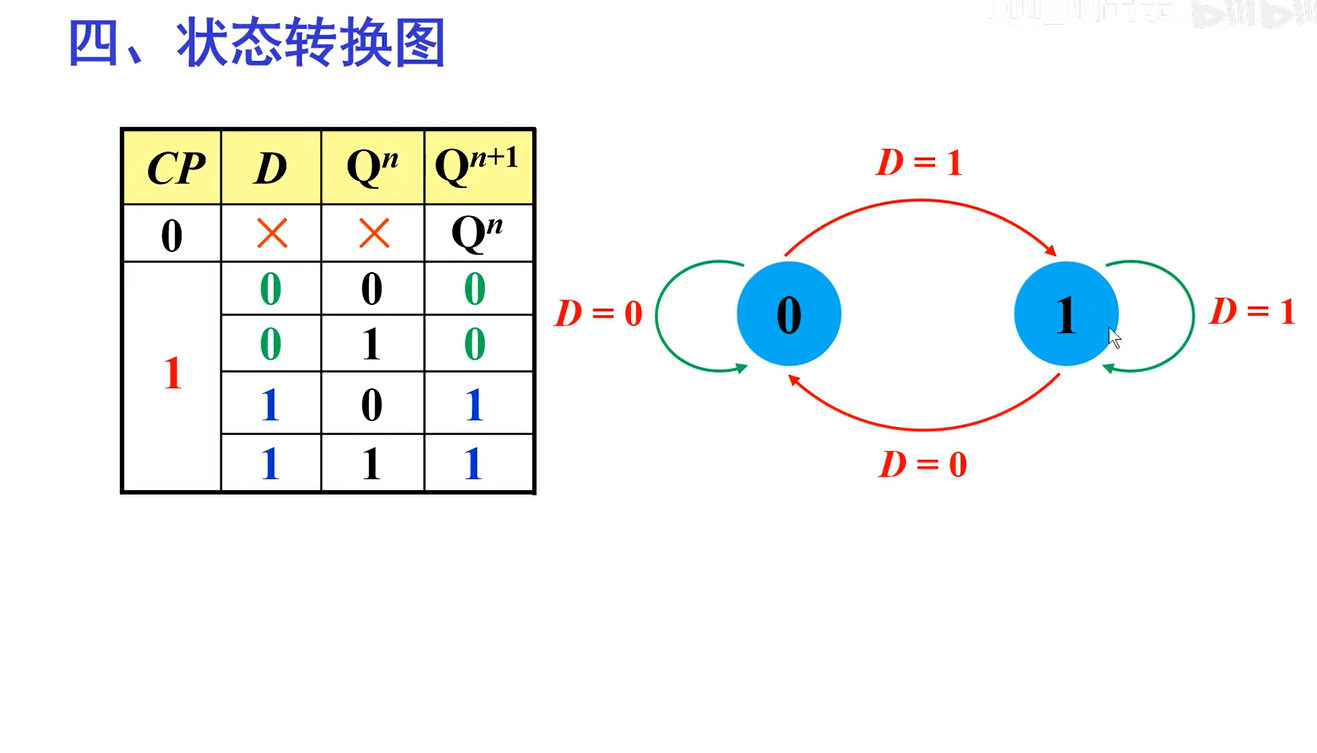

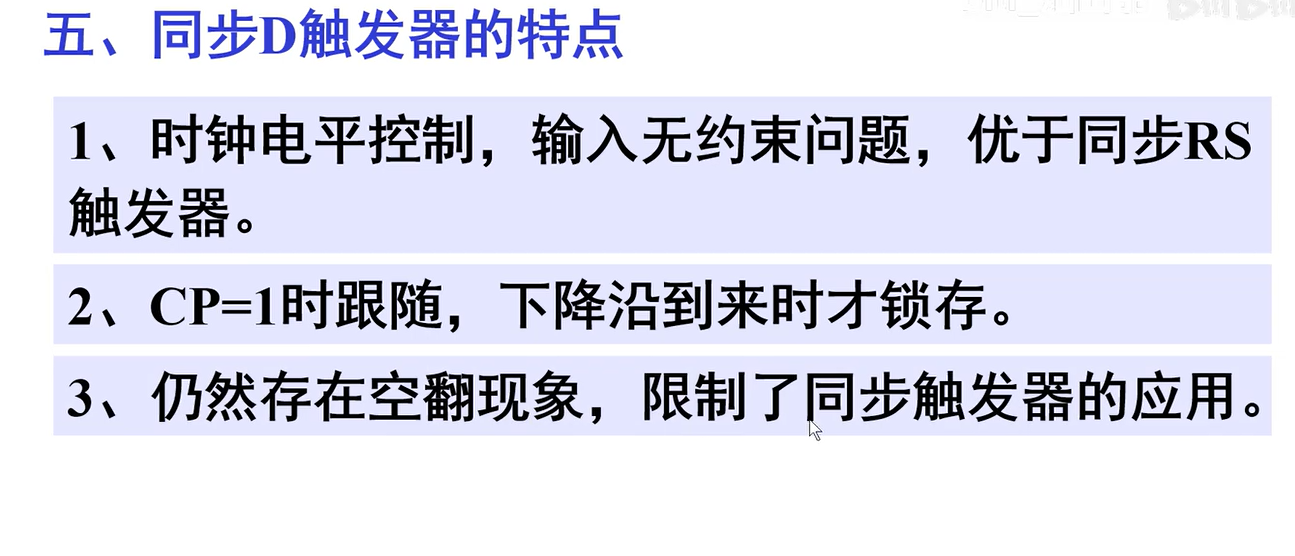

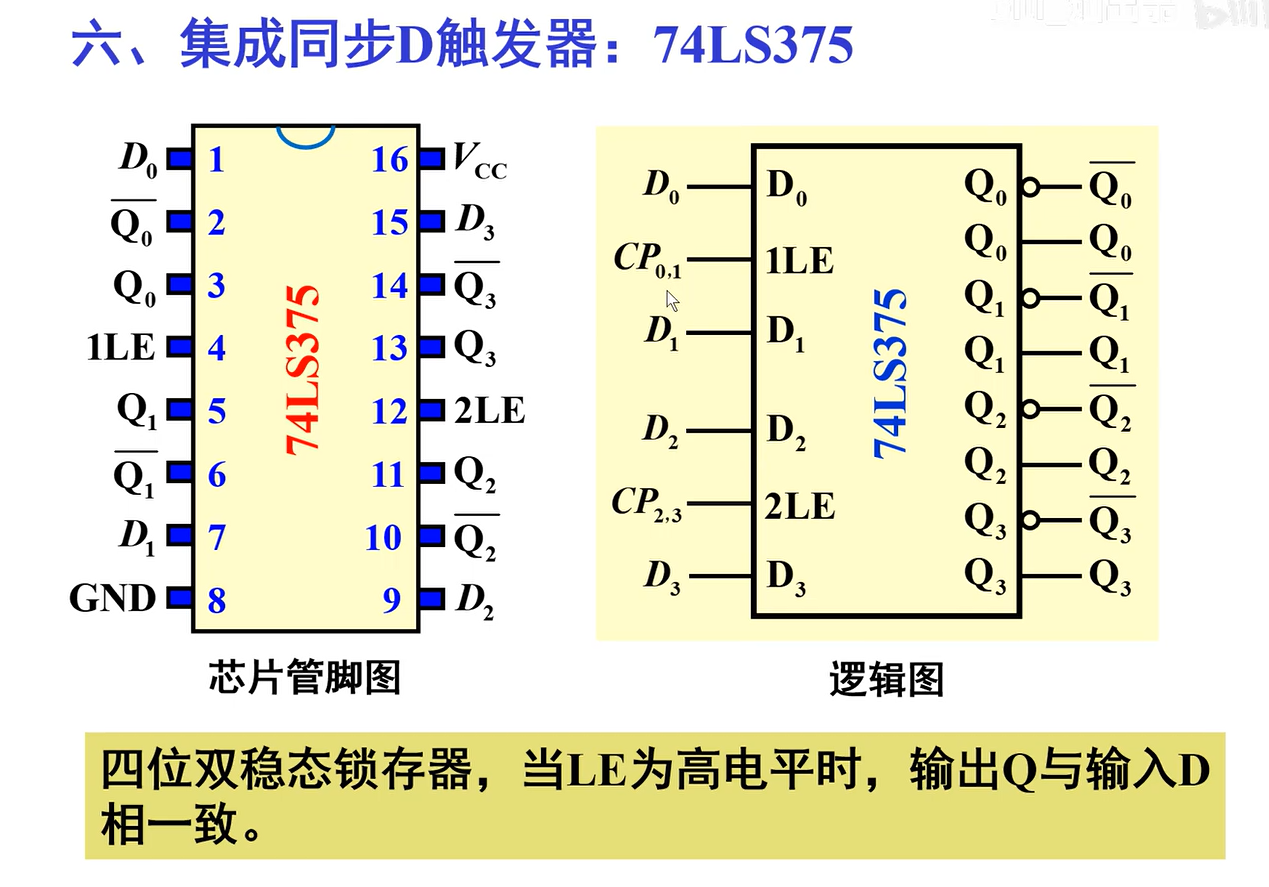

4.2.2 同步D触发器

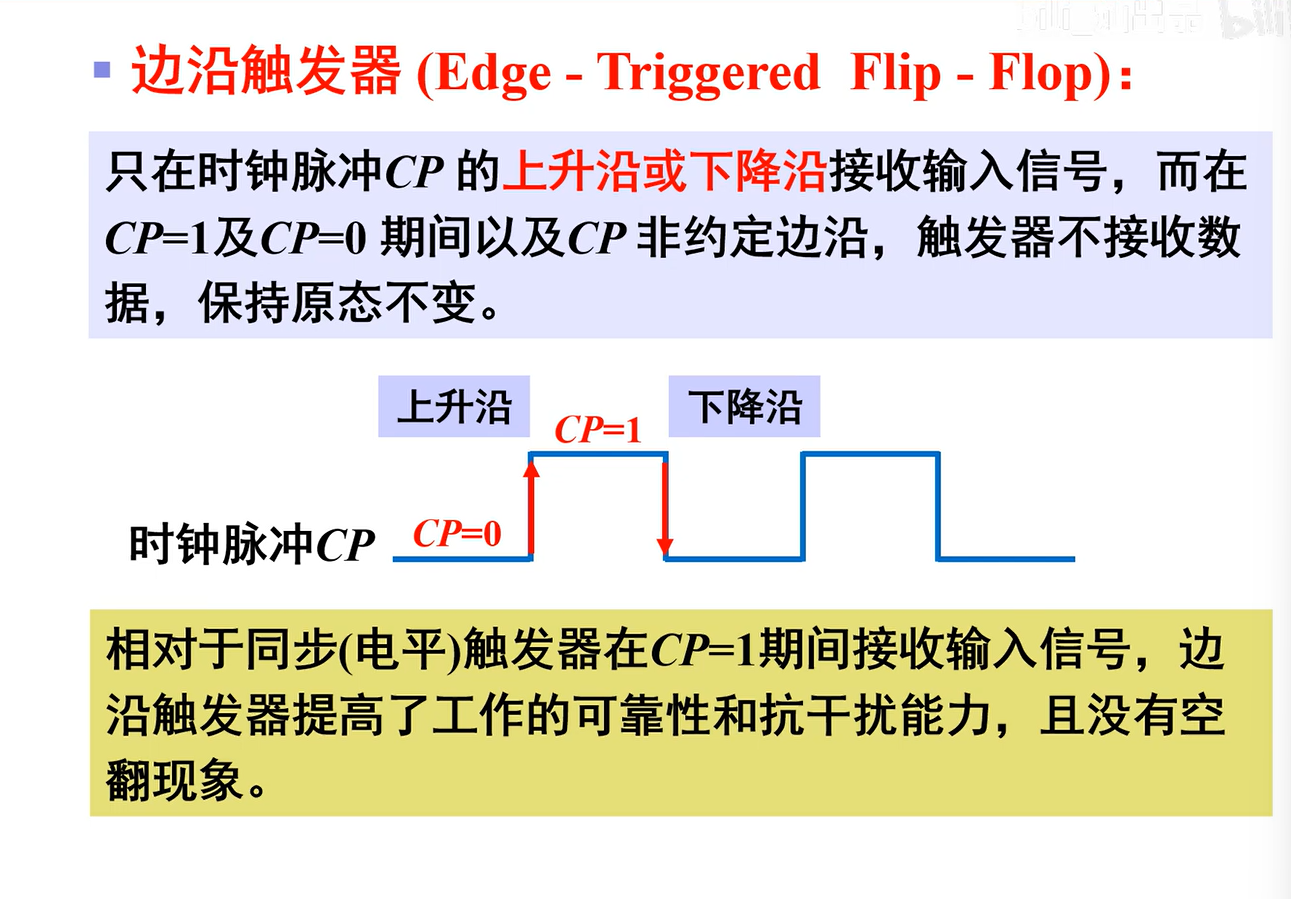

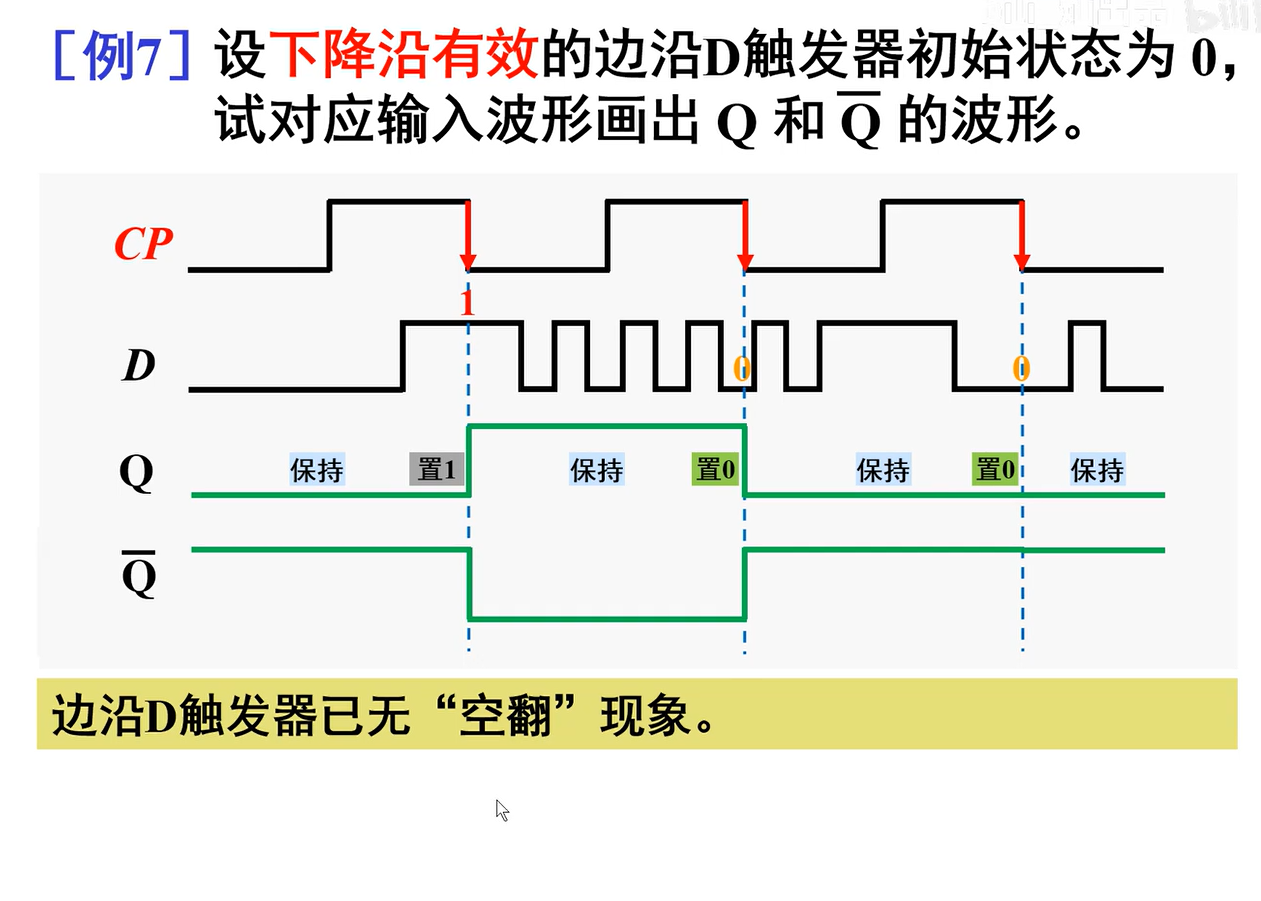

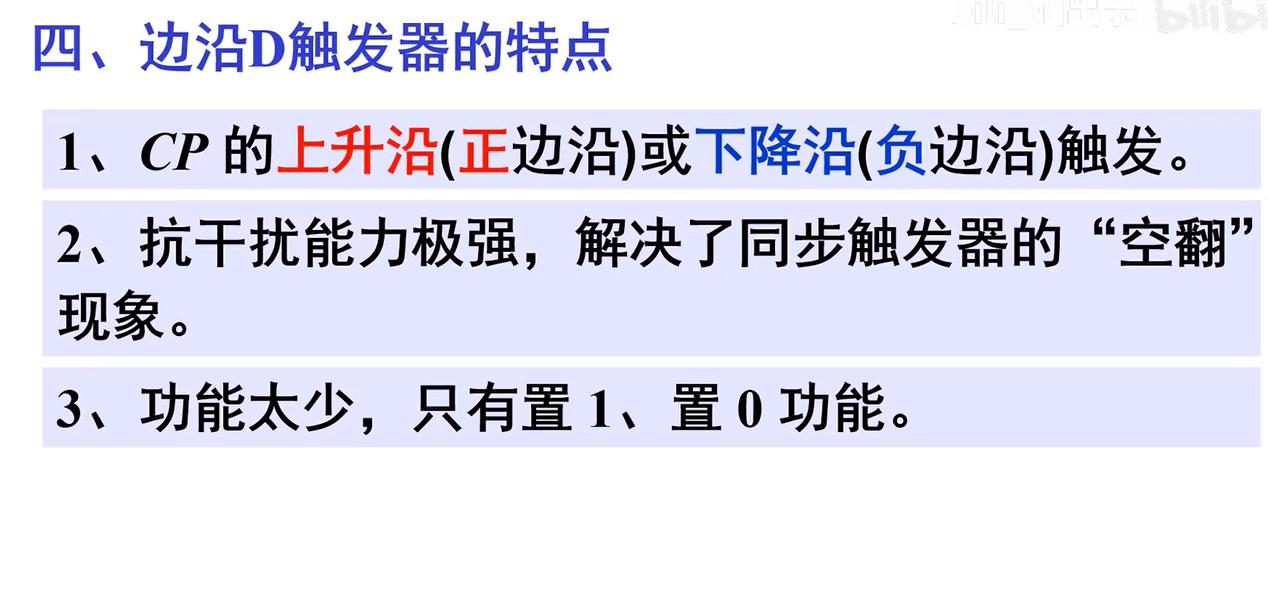

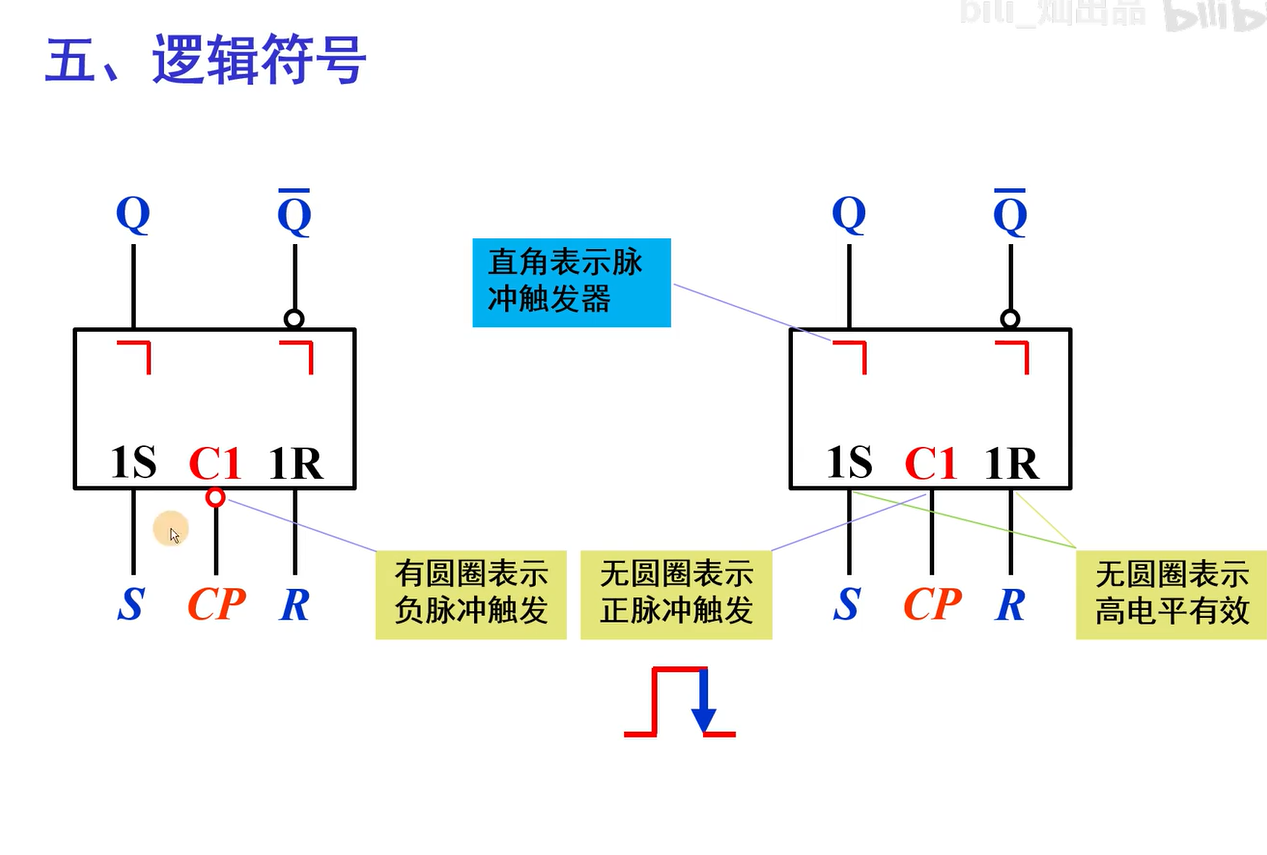

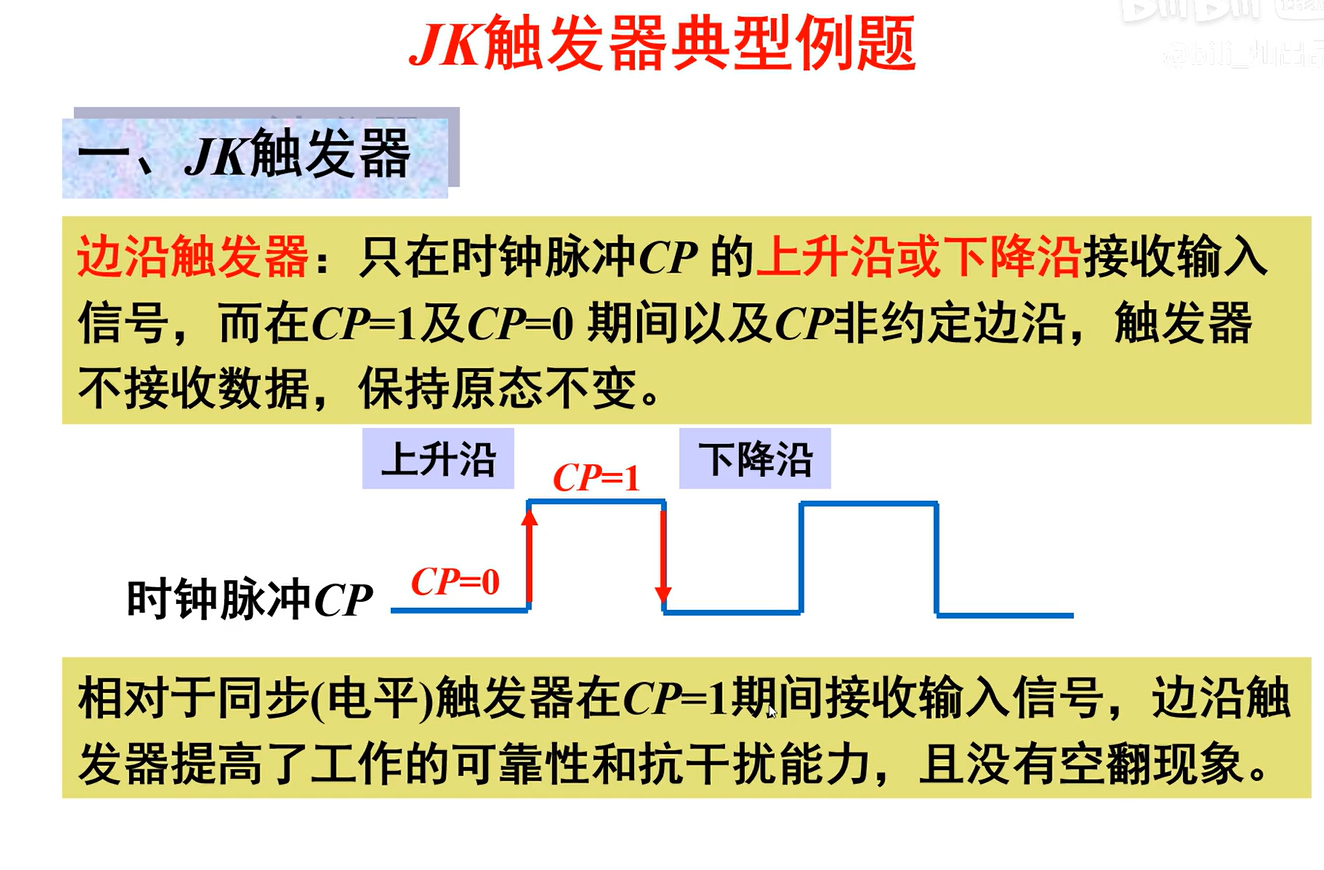

4.3 边沿触发器

在上升沿或下降沿接收信号

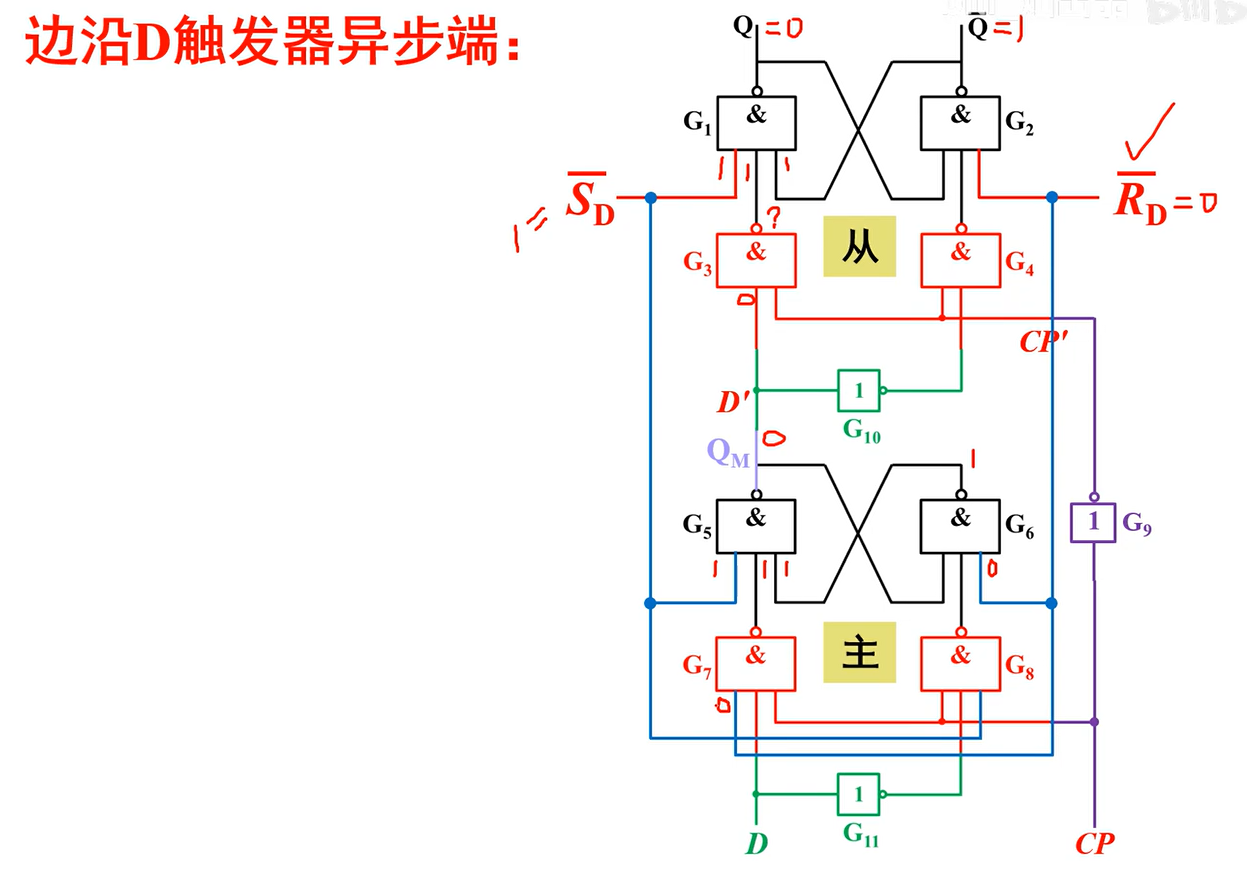

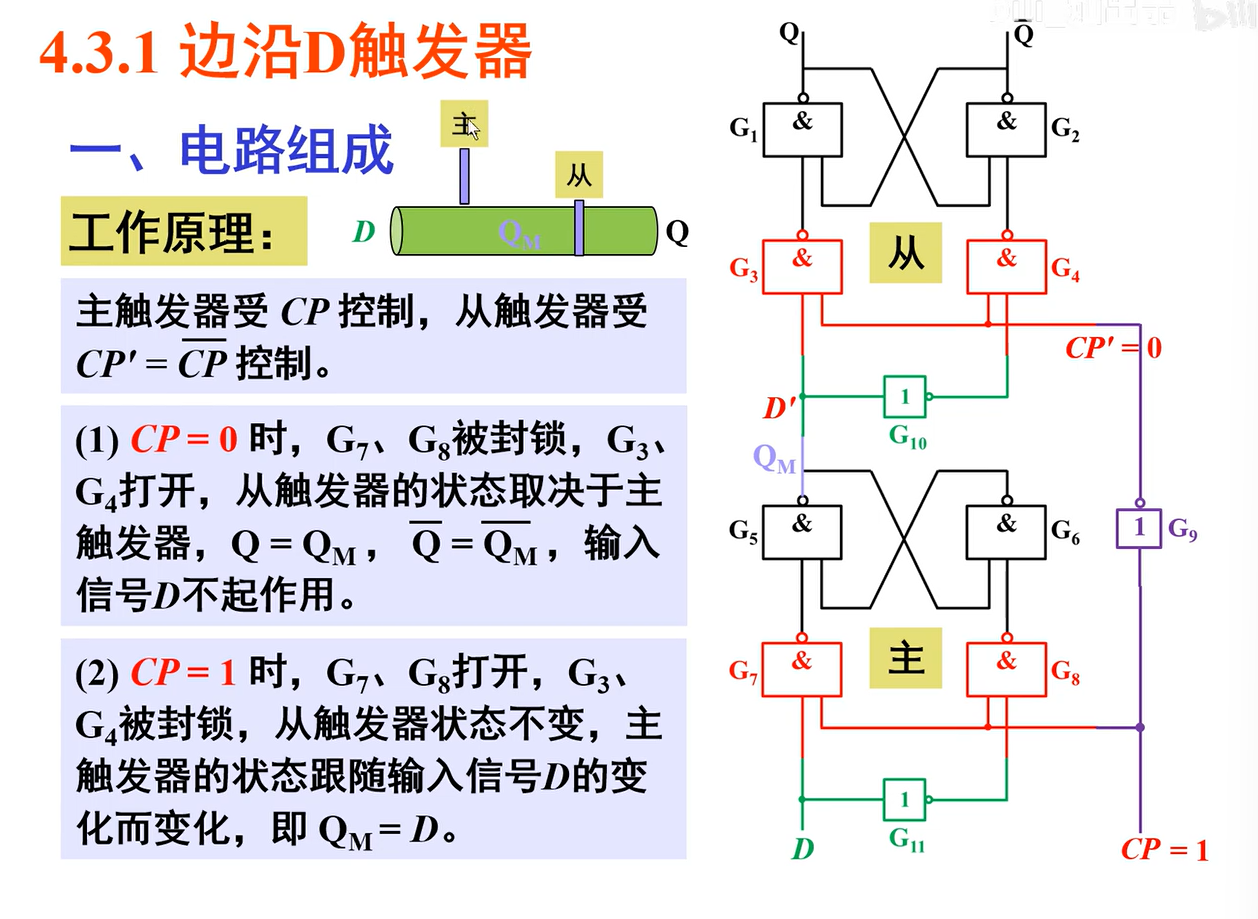

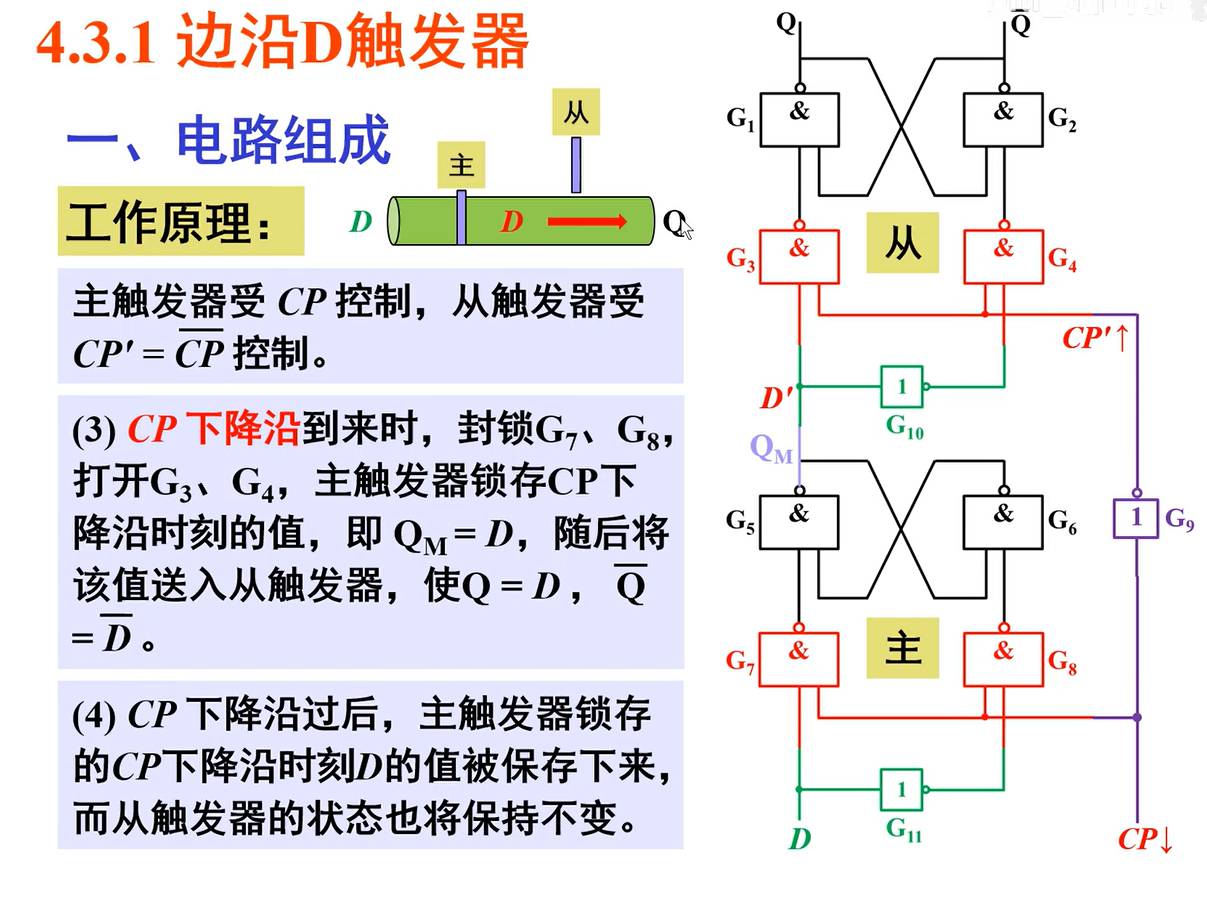

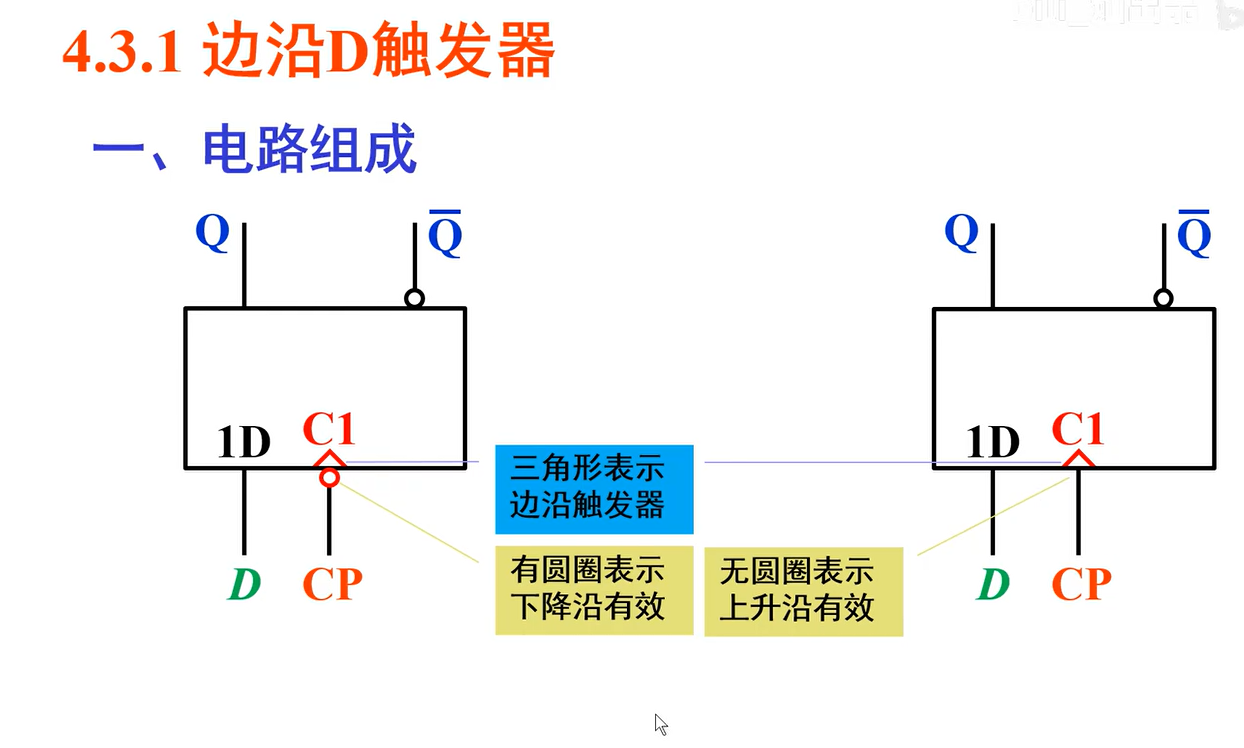

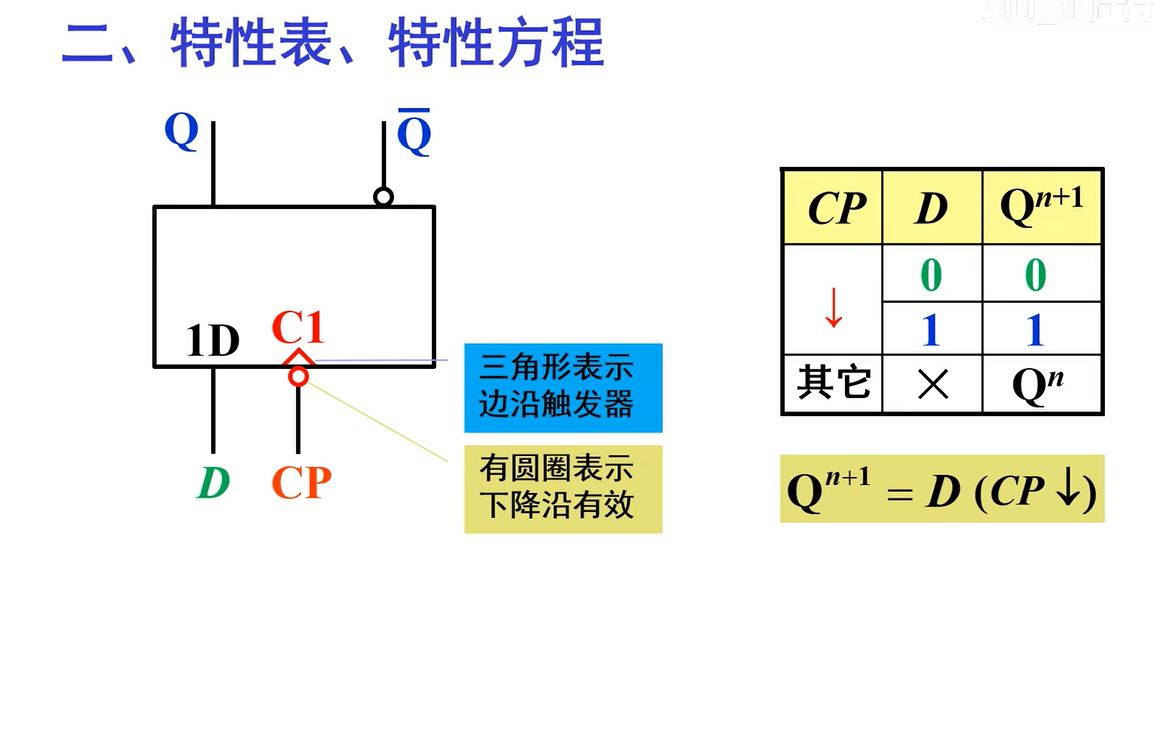

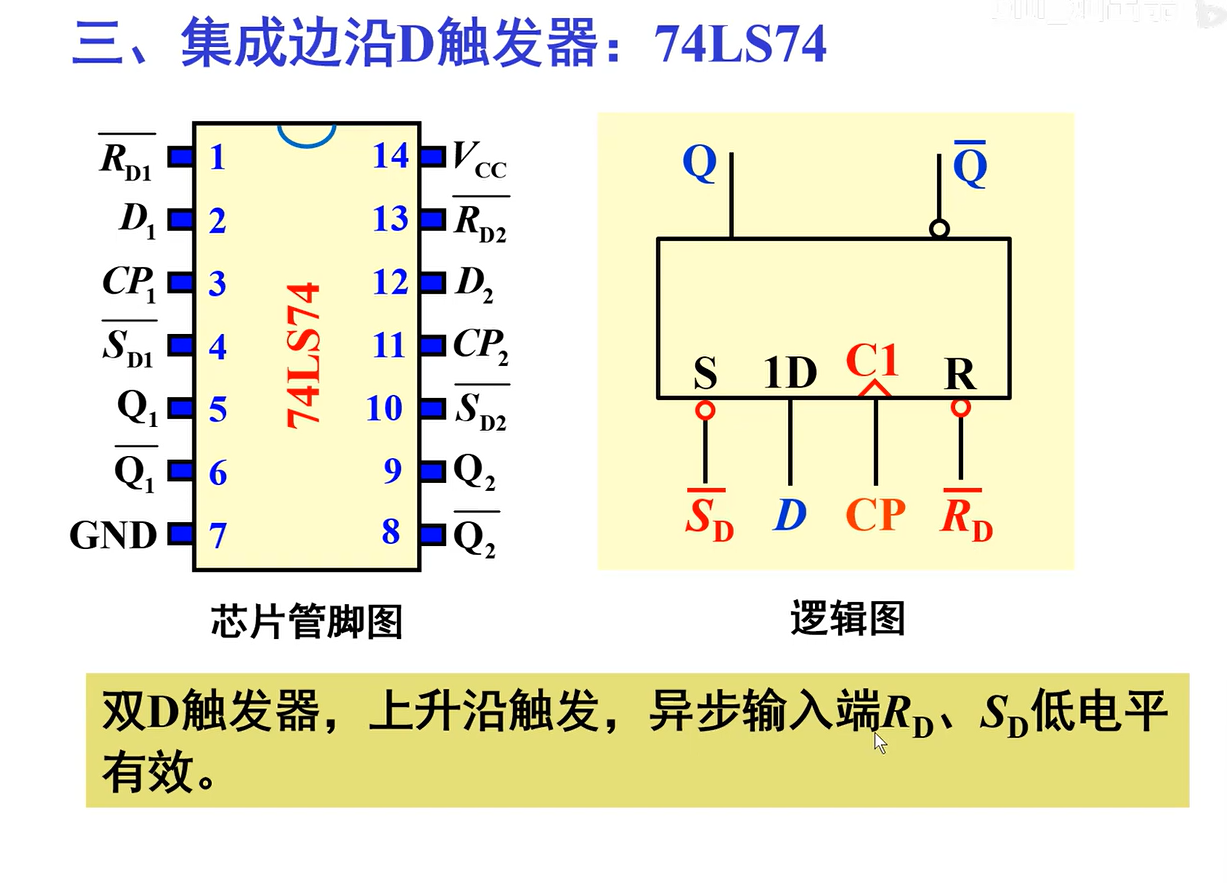

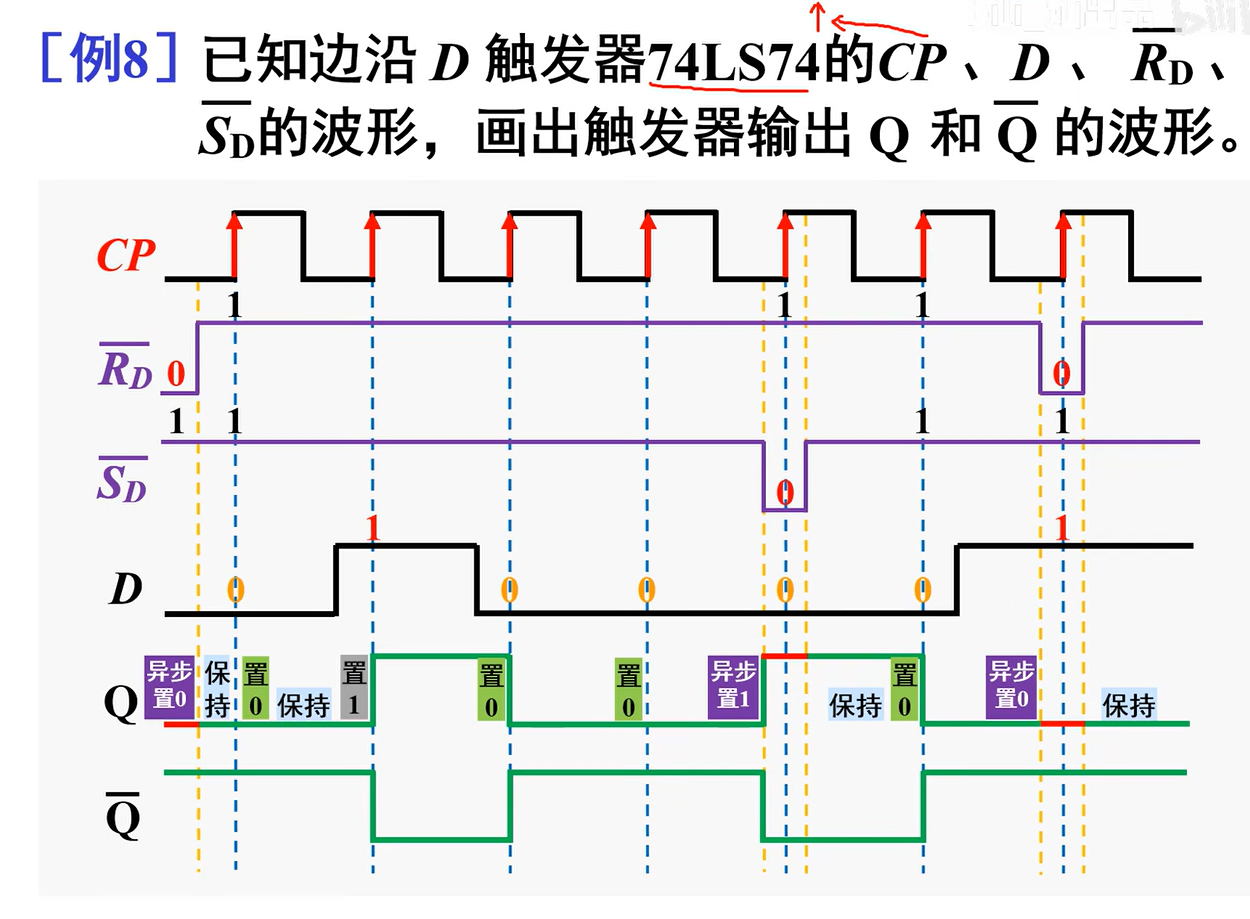

4.3.1 边沿D触发器

1,电路组成

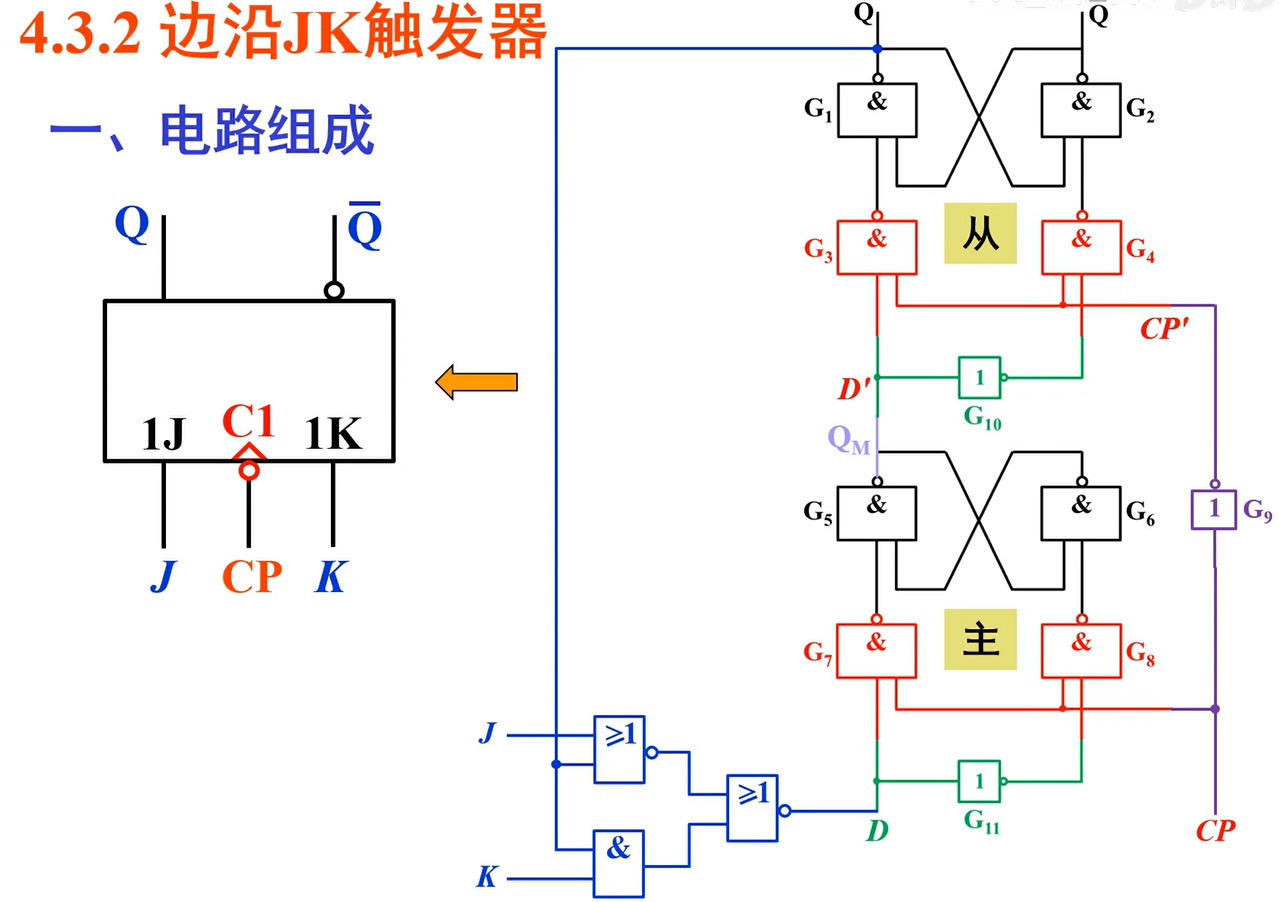

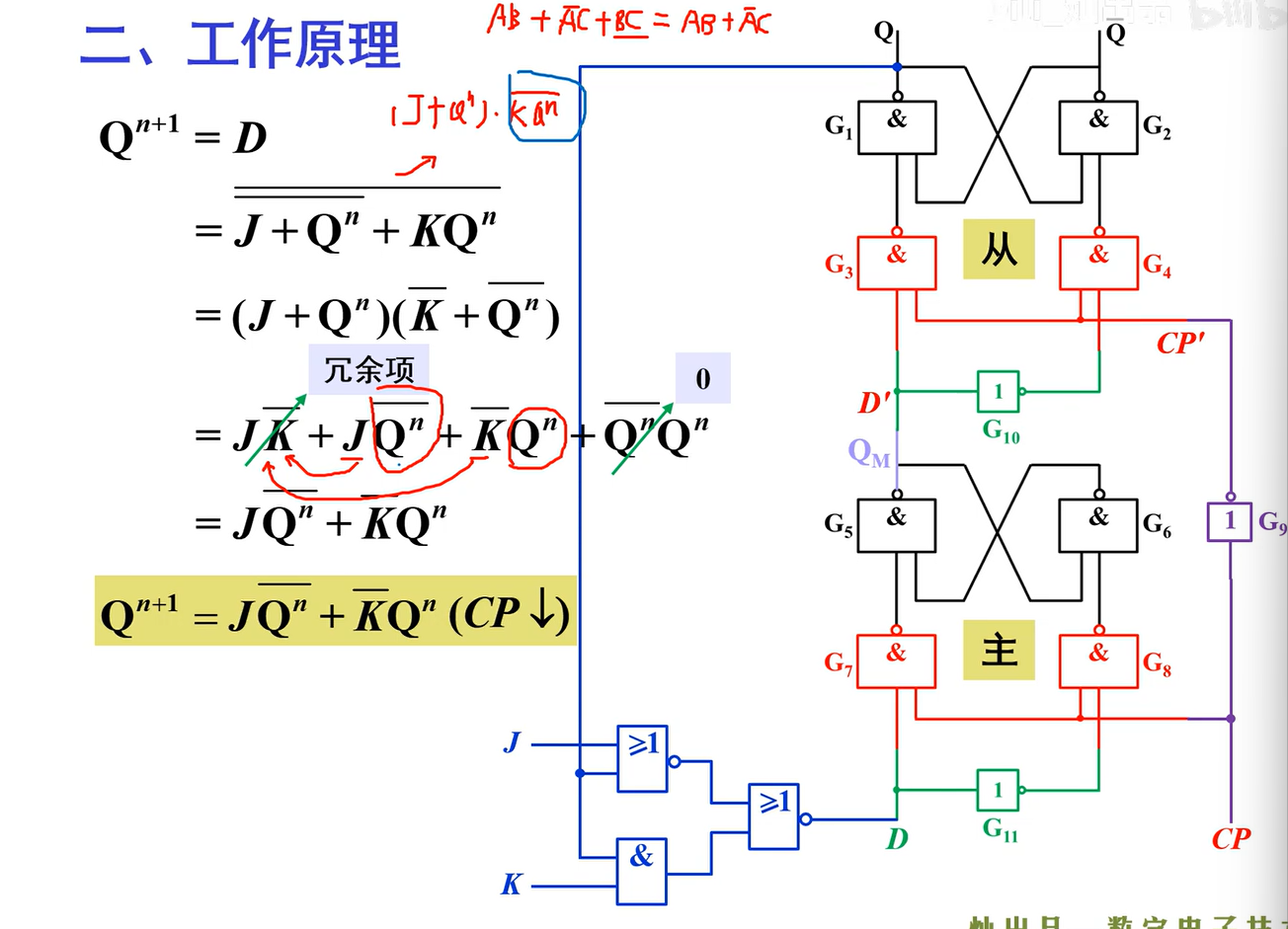

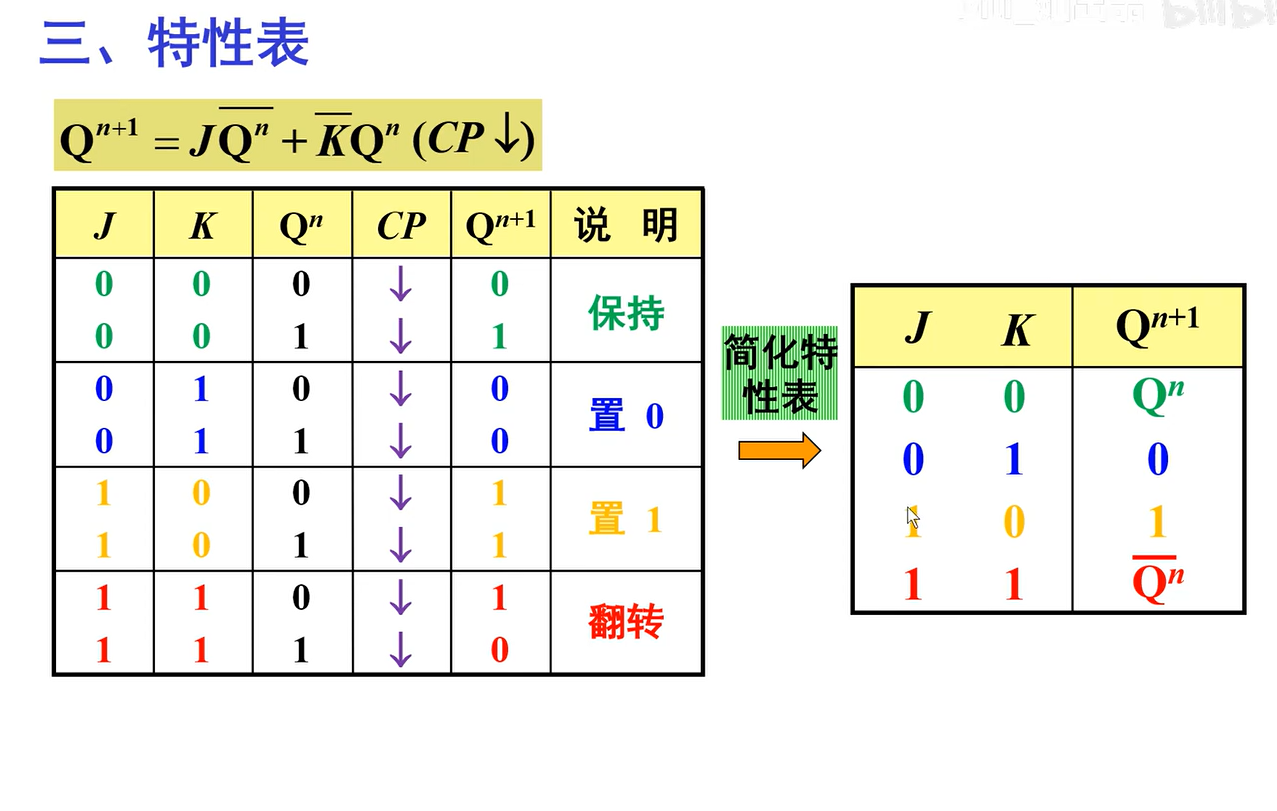

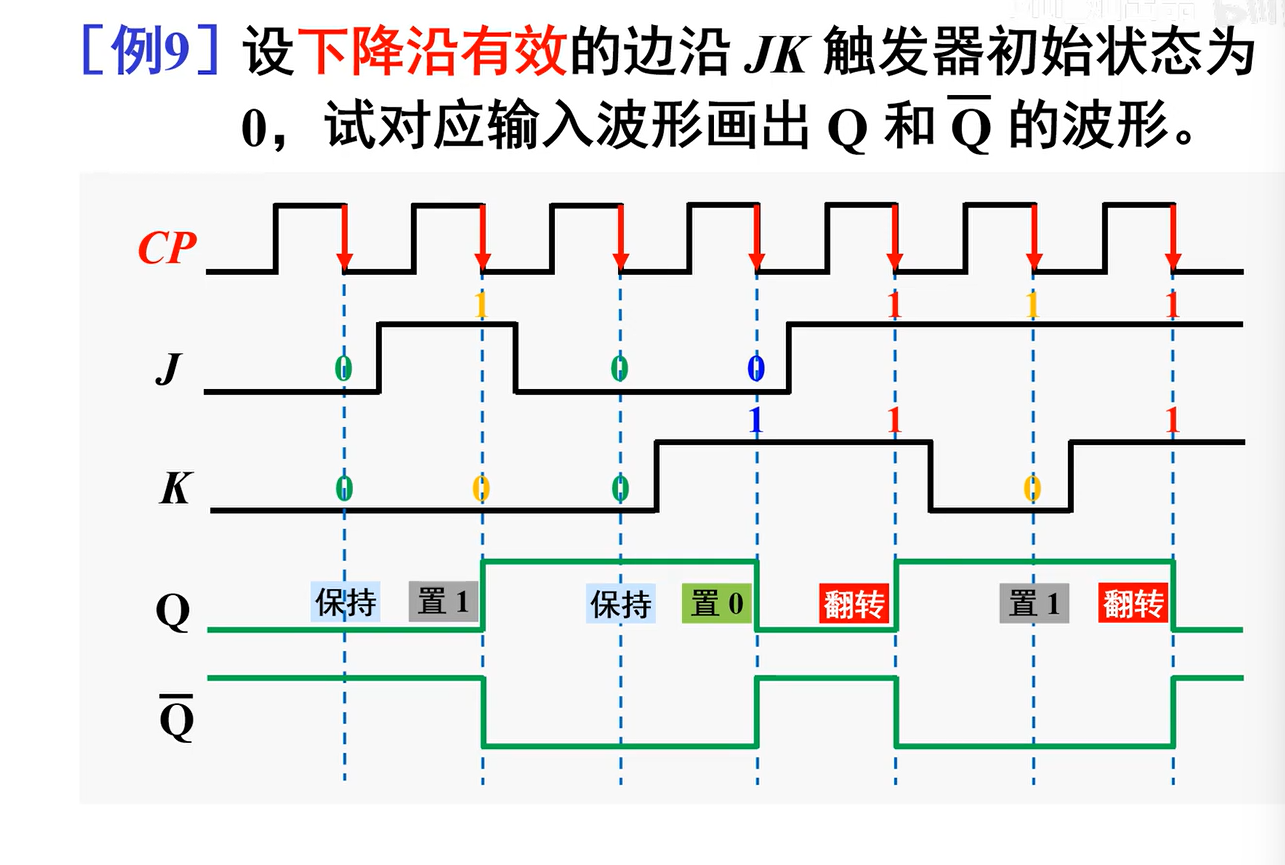

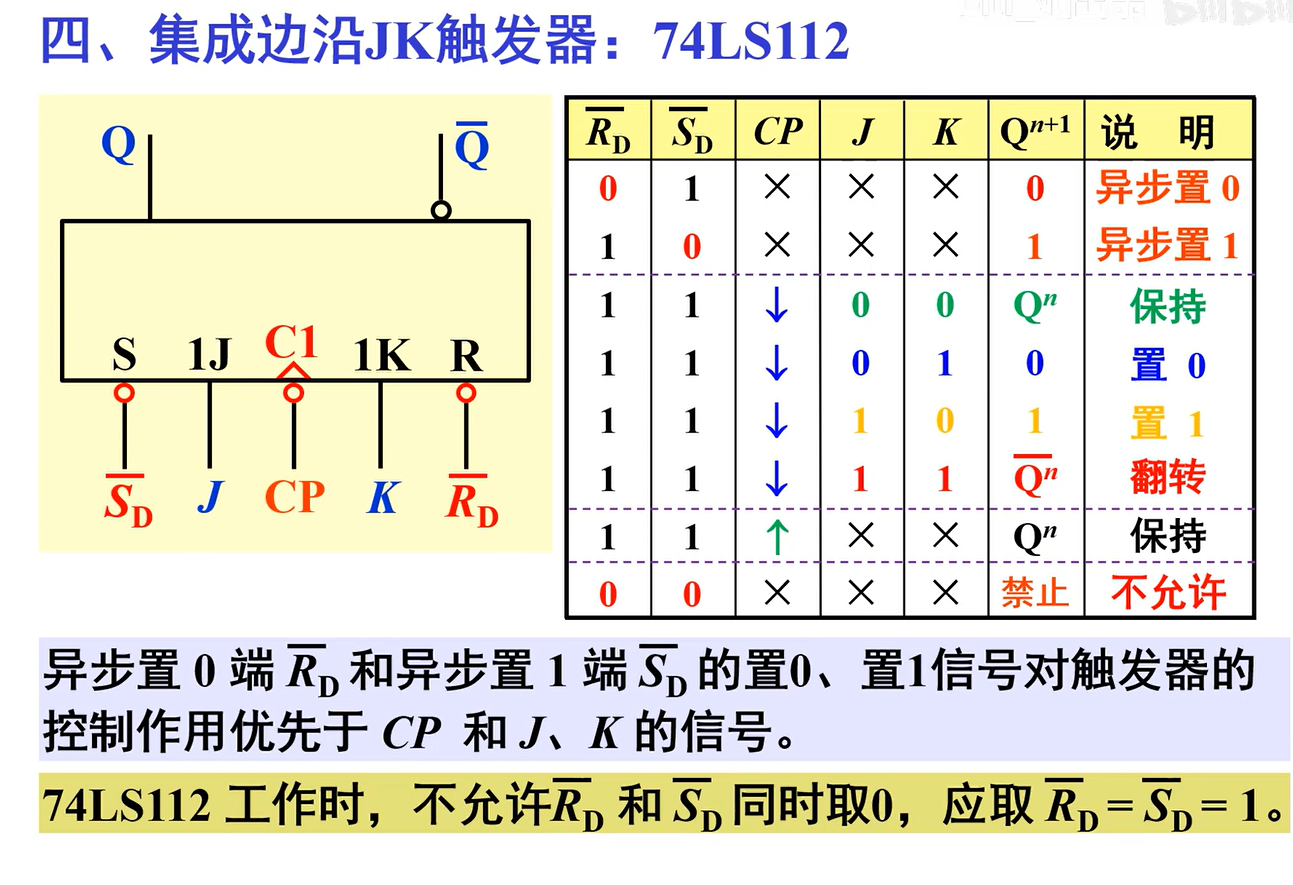

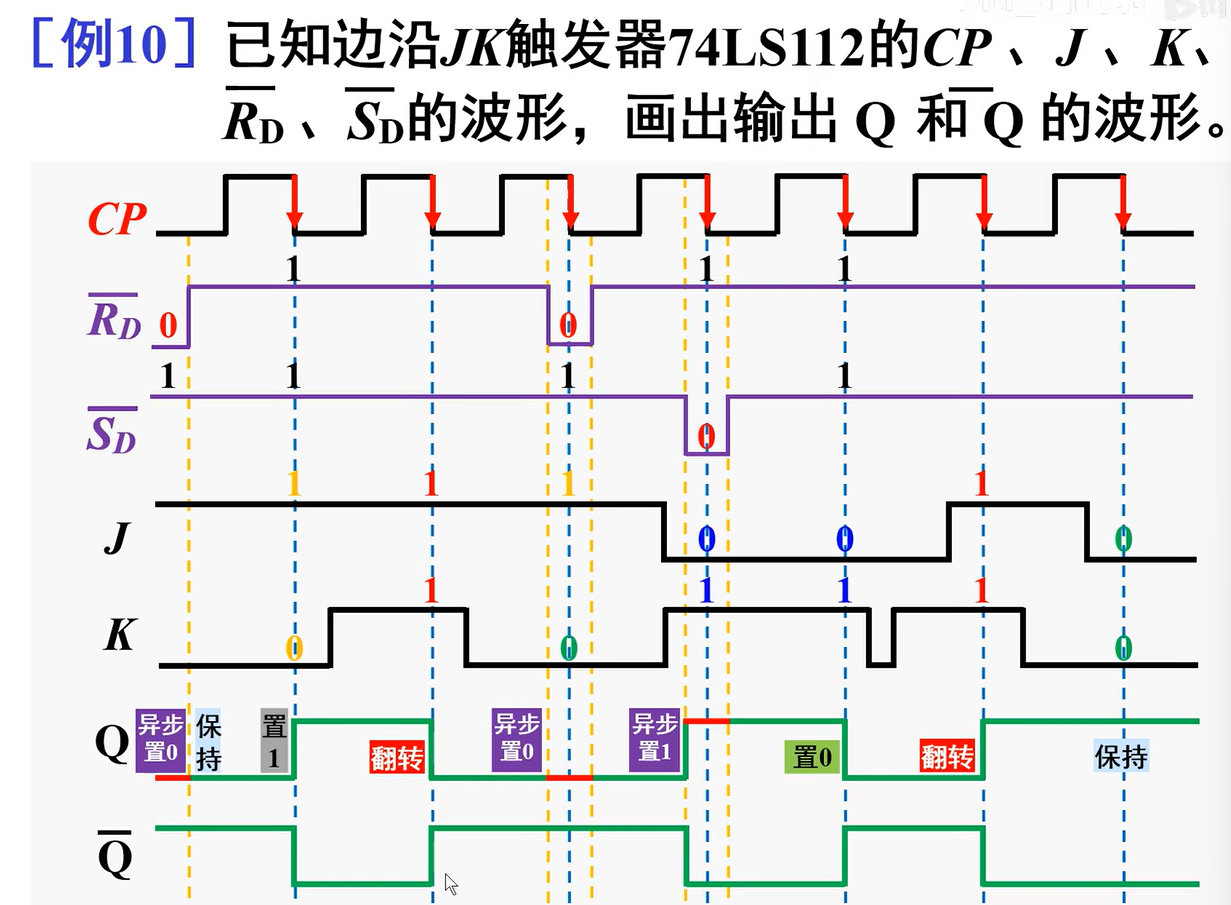

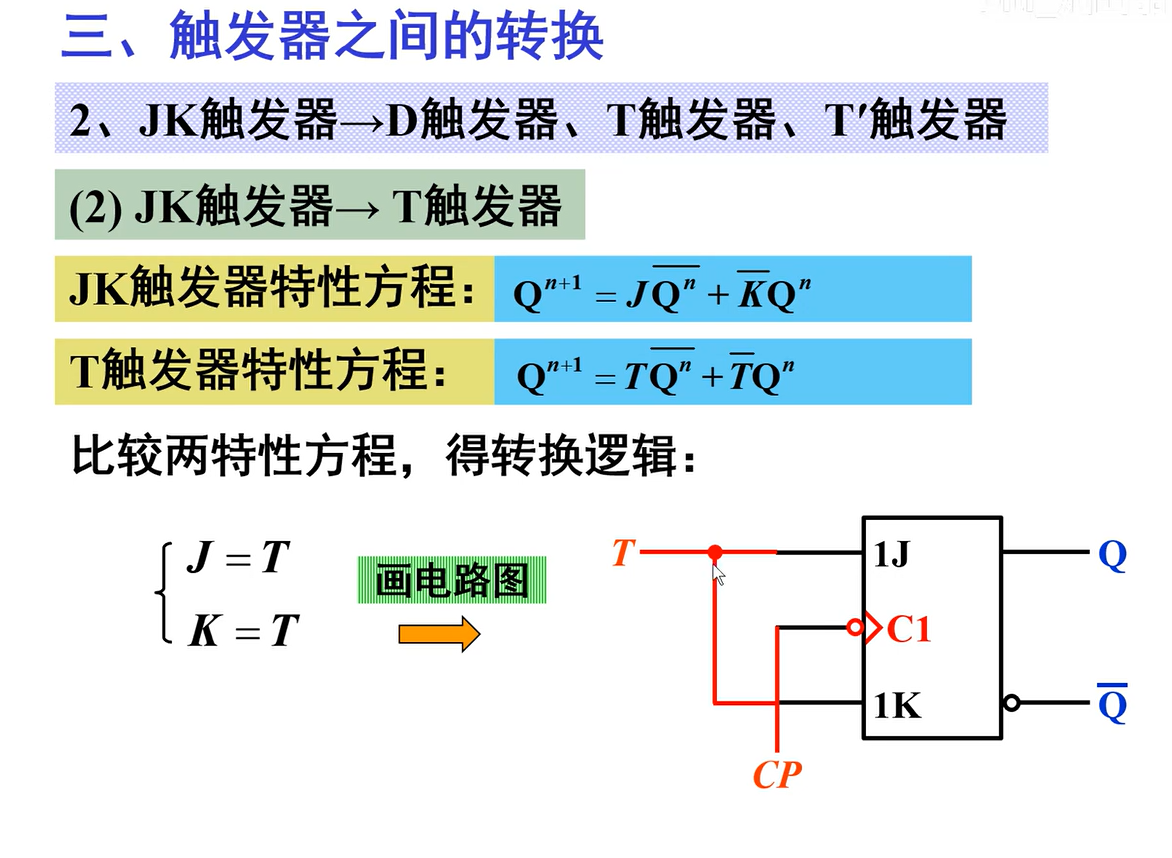

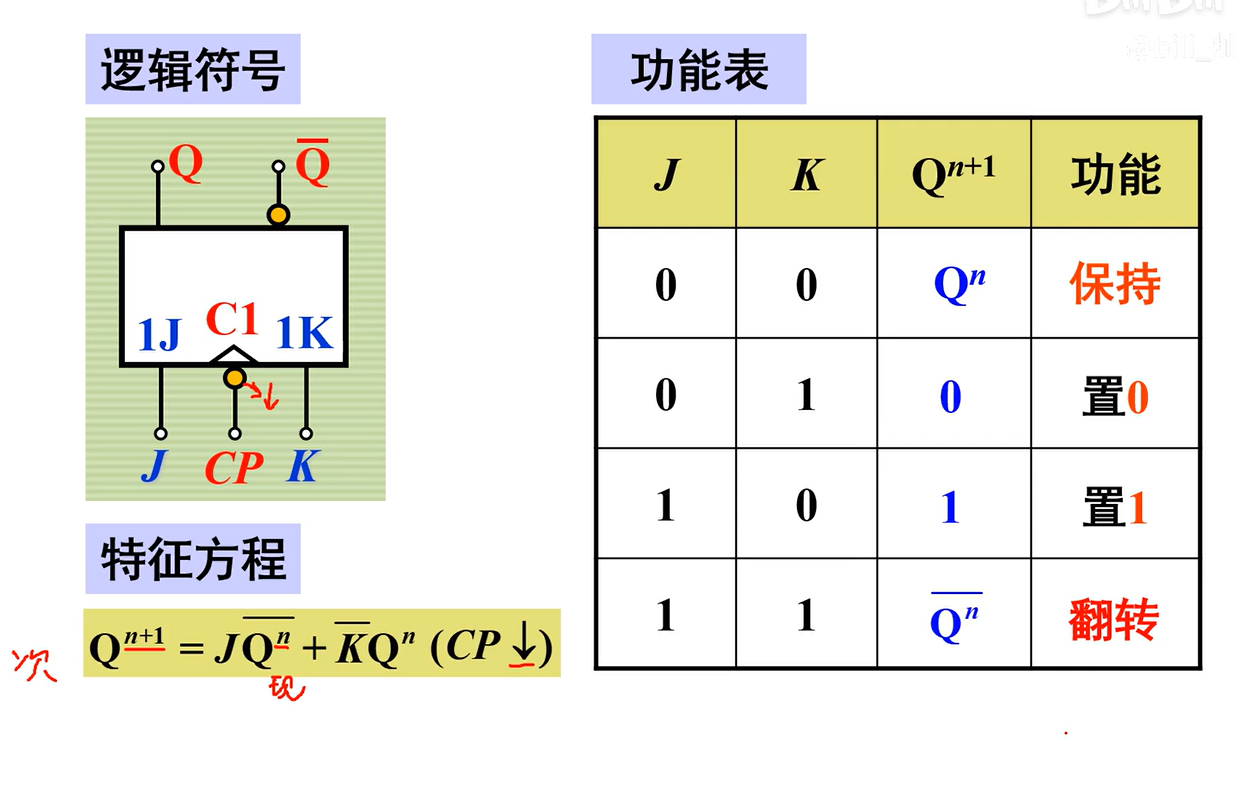

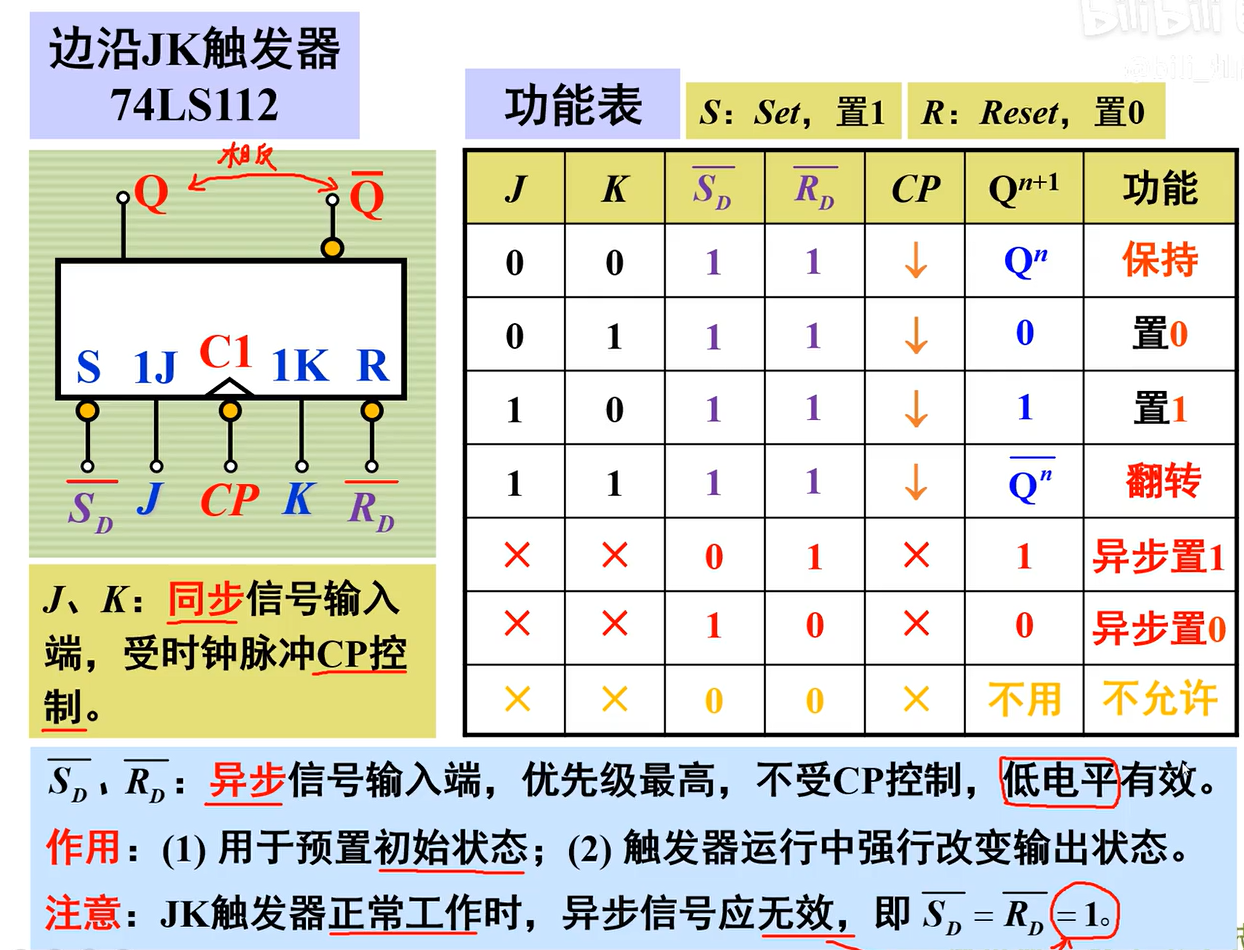

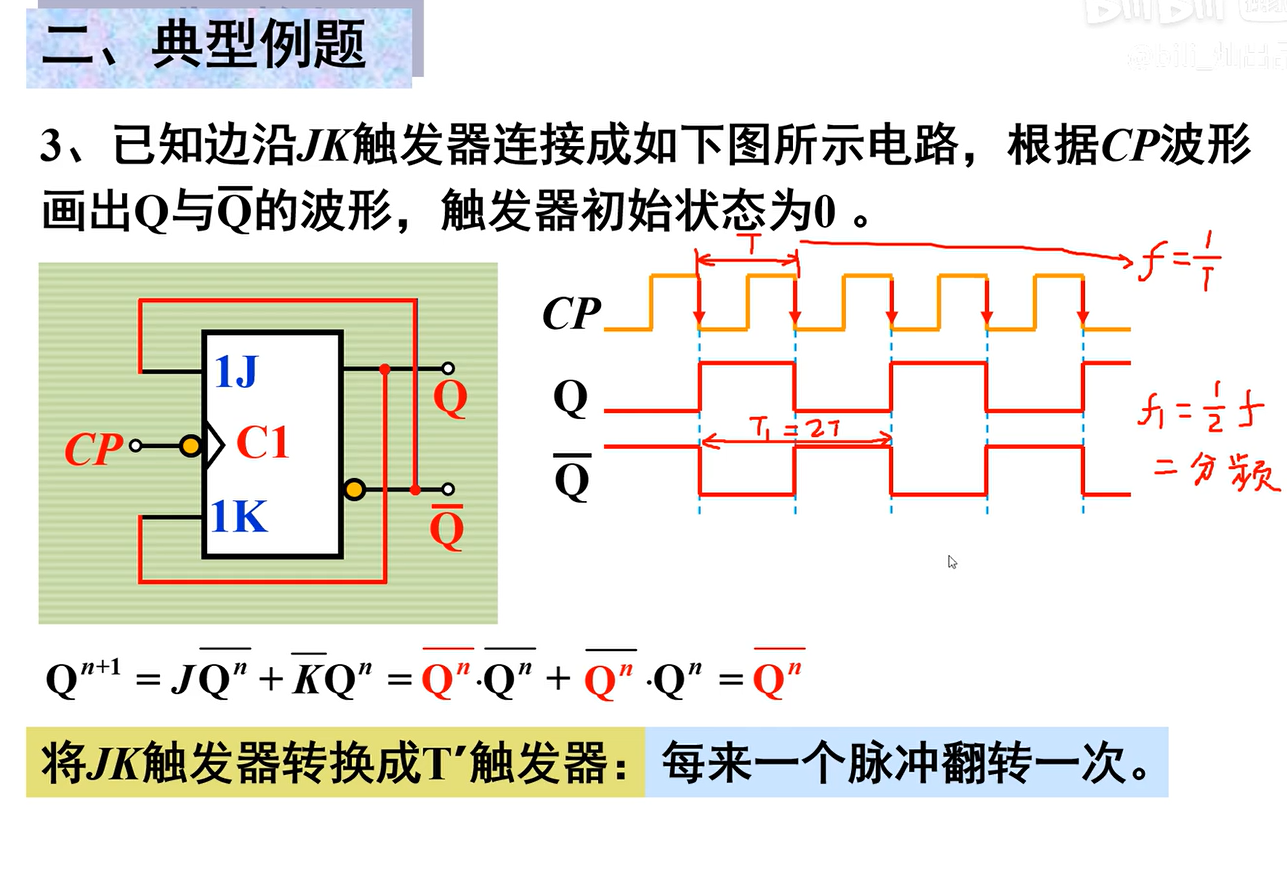

4.3.2 边沿JK触发器

双JK触发器,下降沿触发,异步输入端非RD,非SD低电平有效

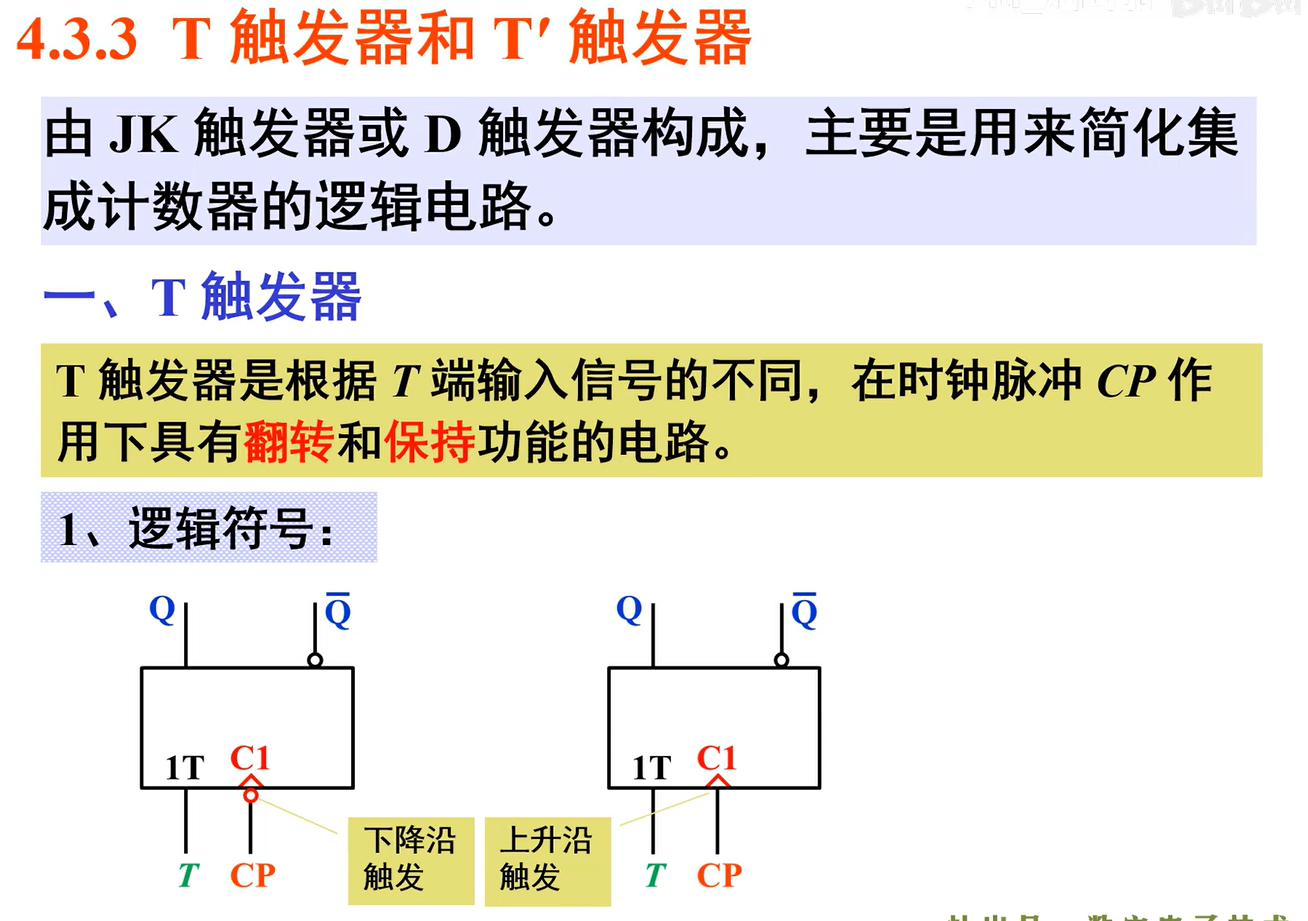

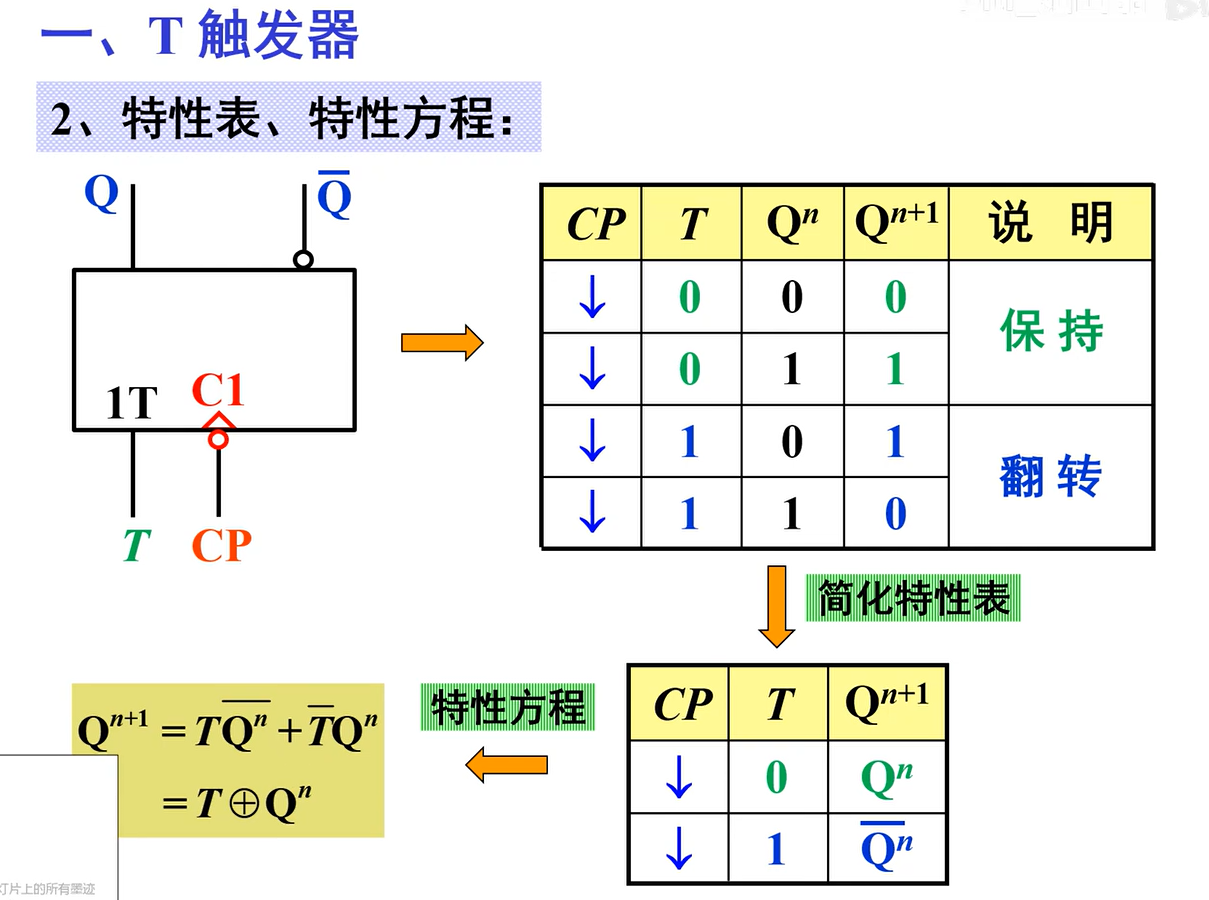

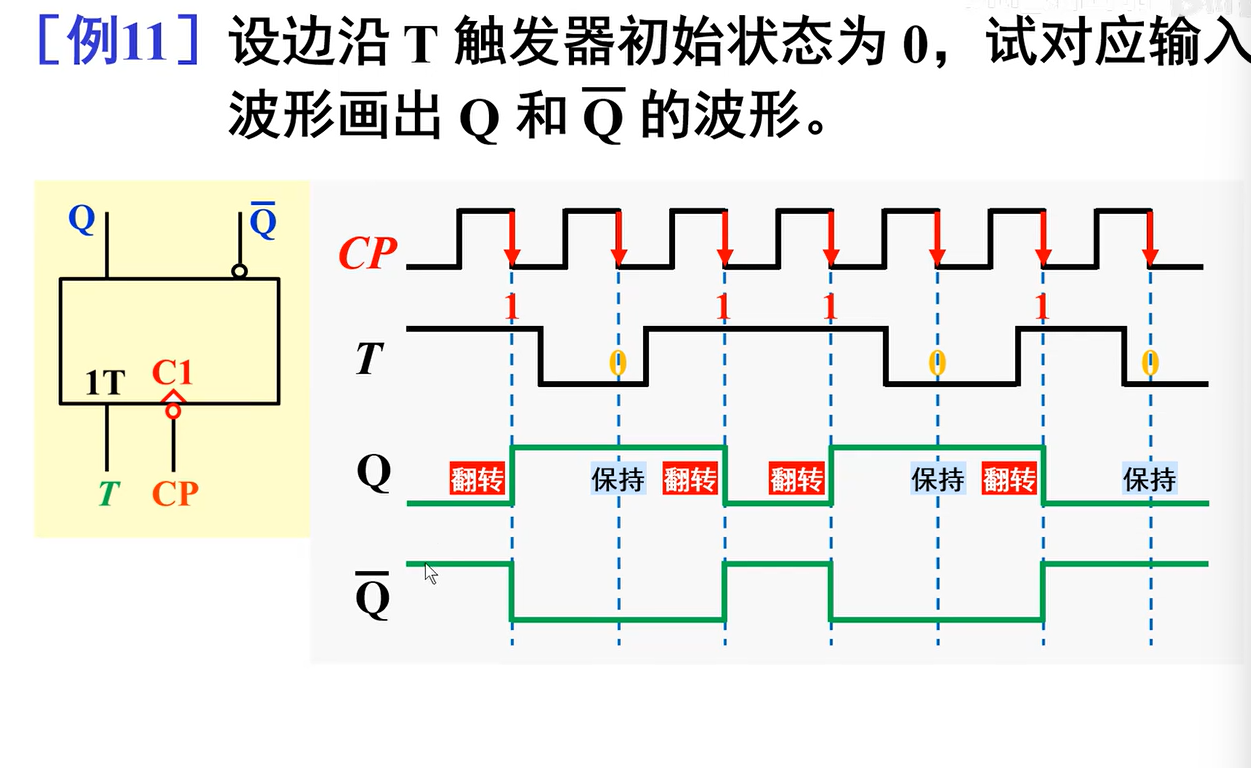

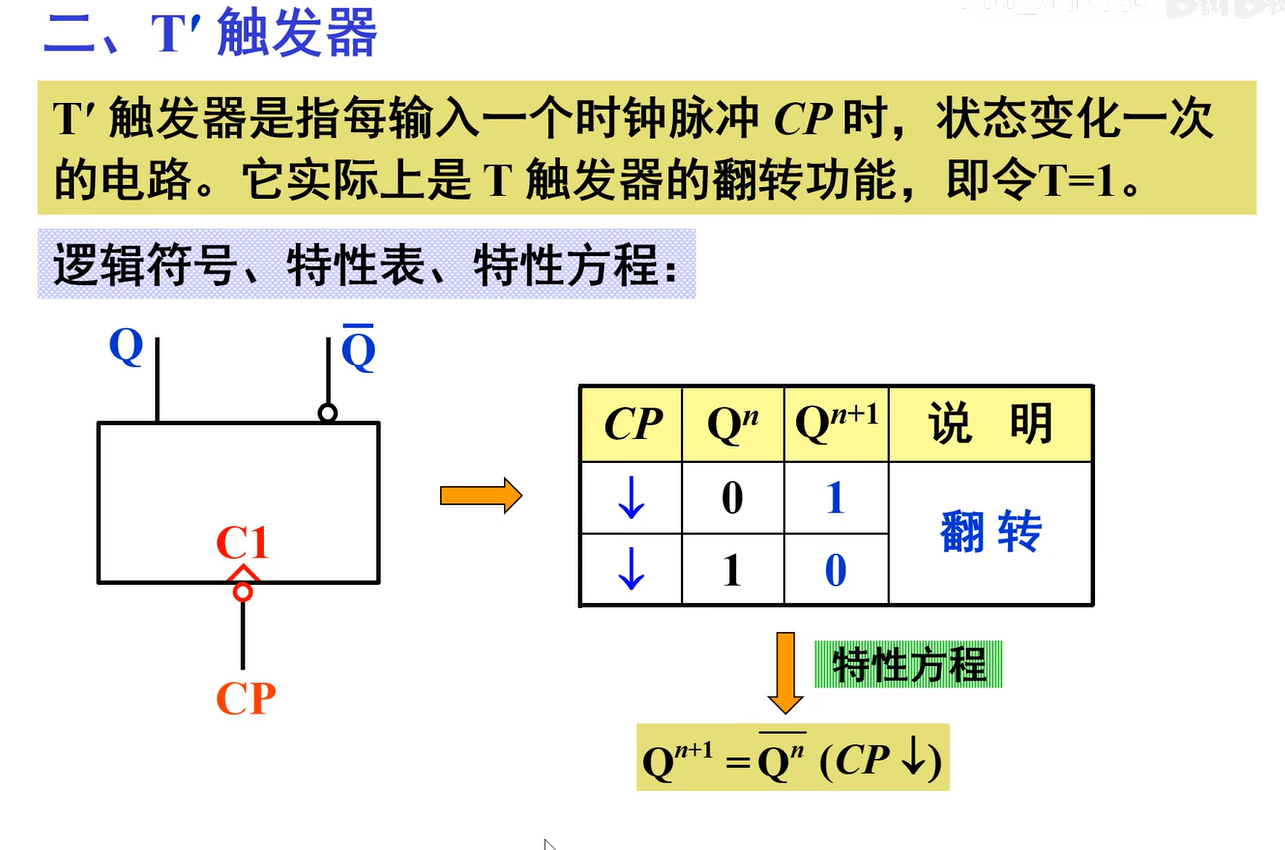

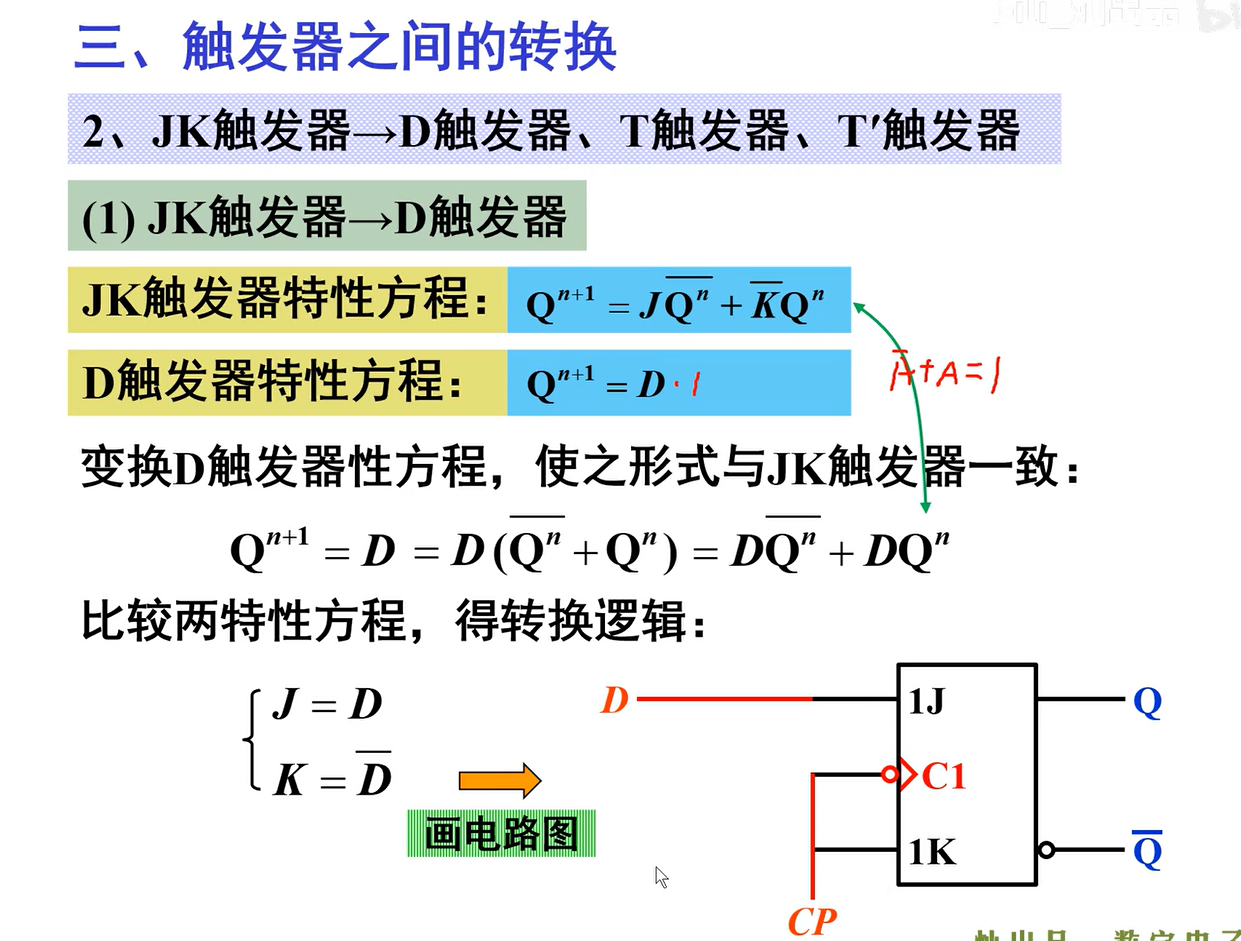

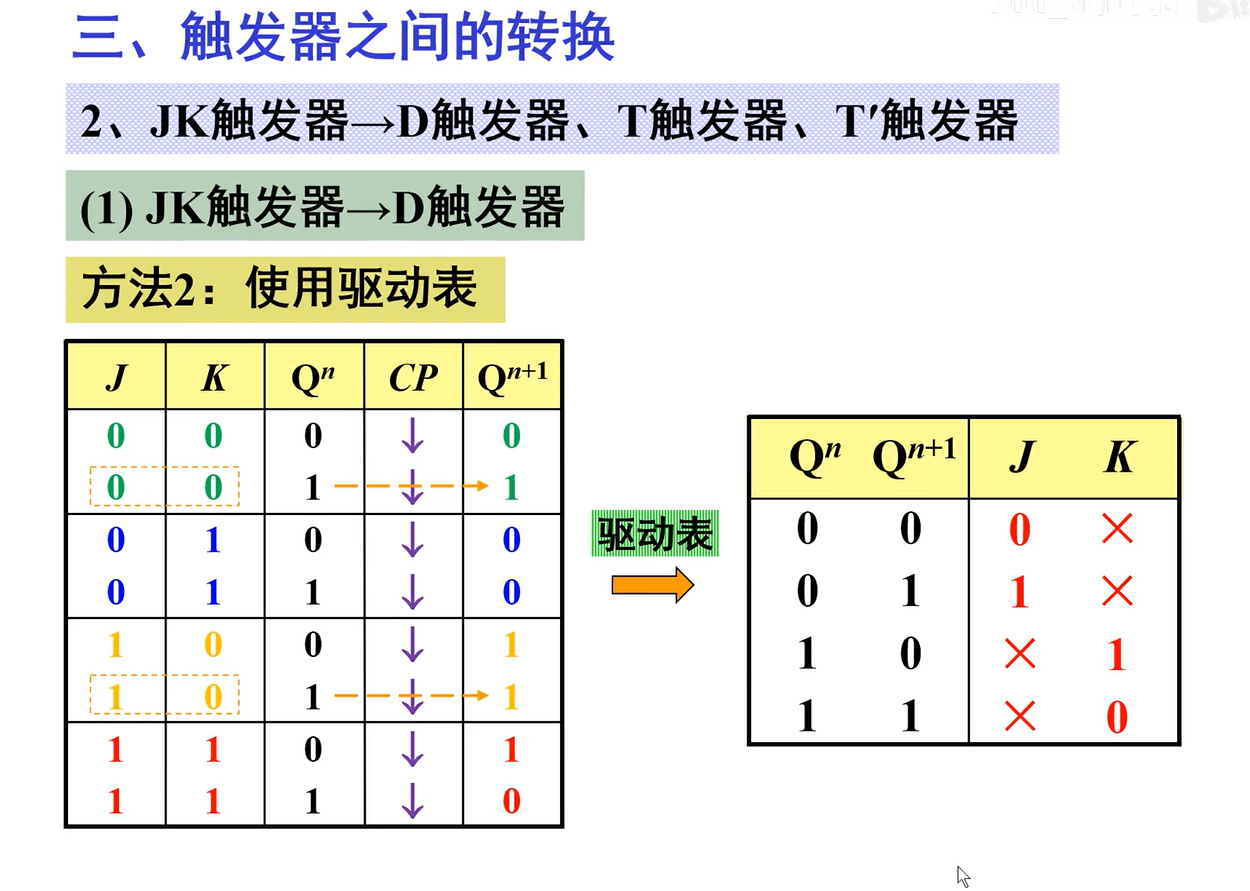

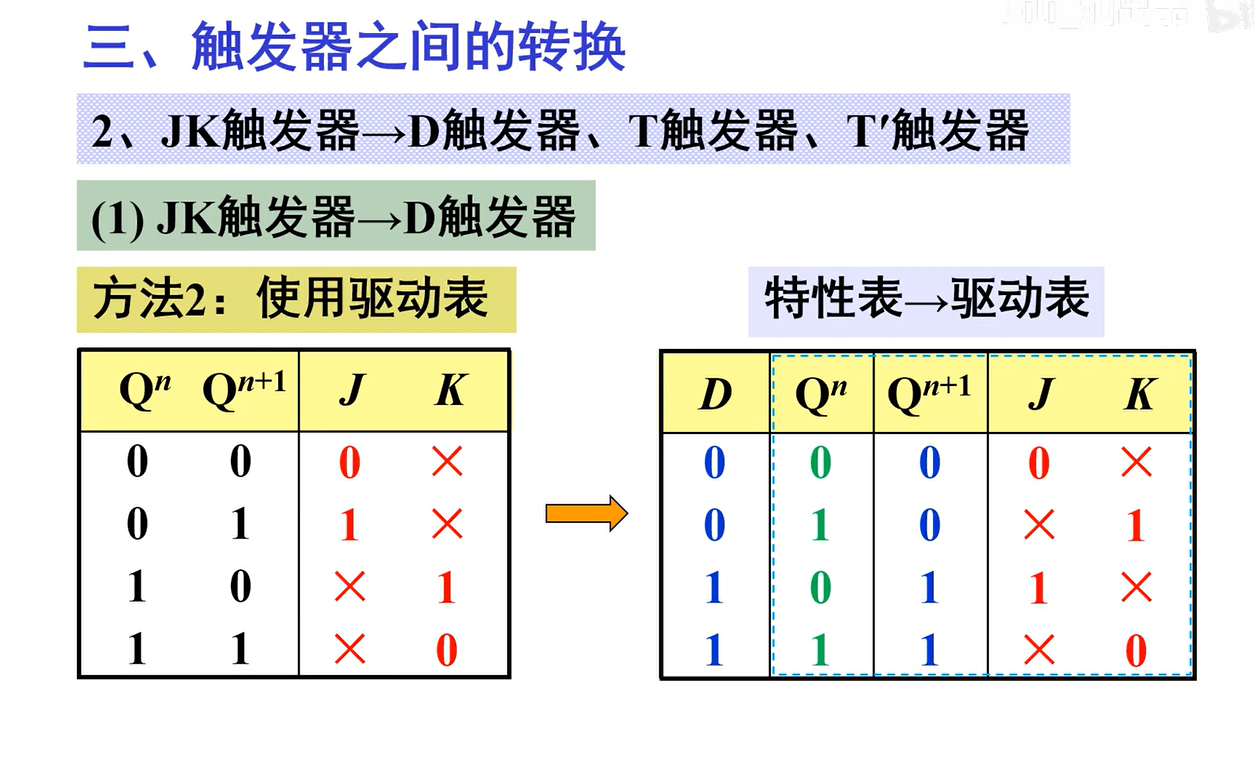

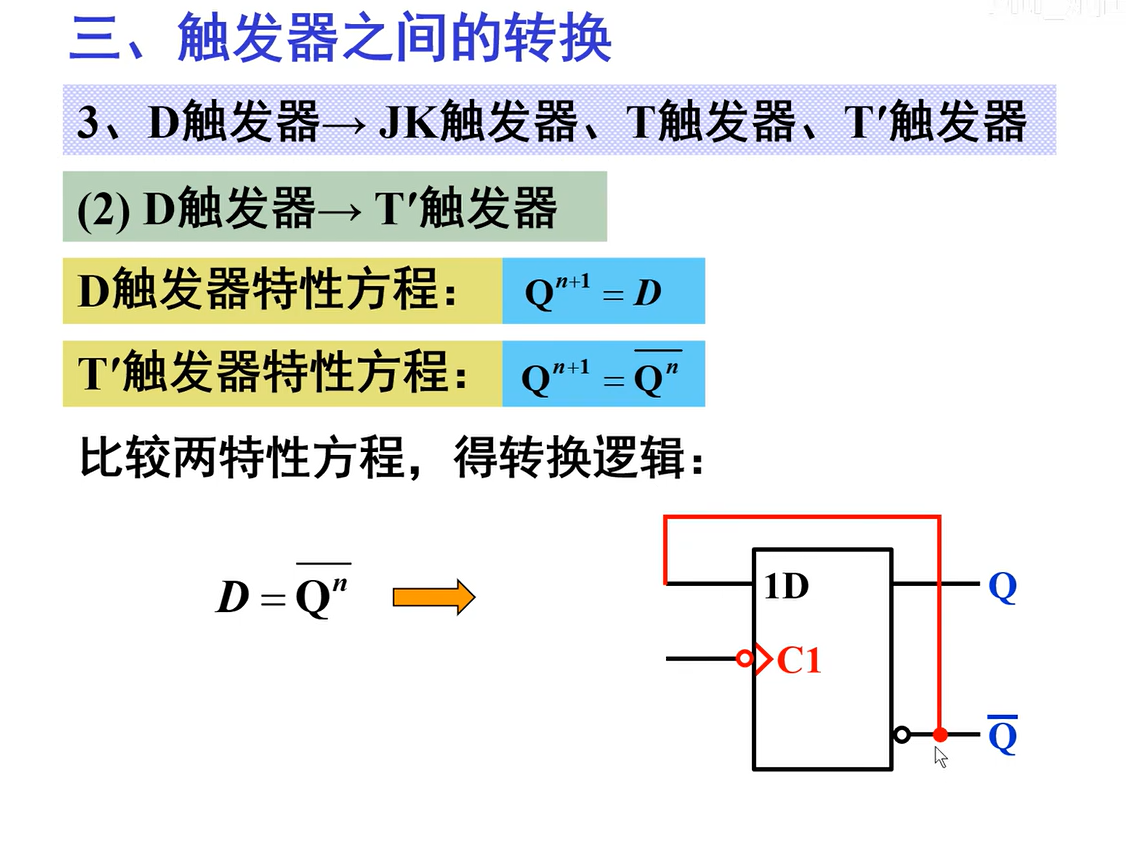

4.3.3 T触发器和T’触发器

由JK和D构成

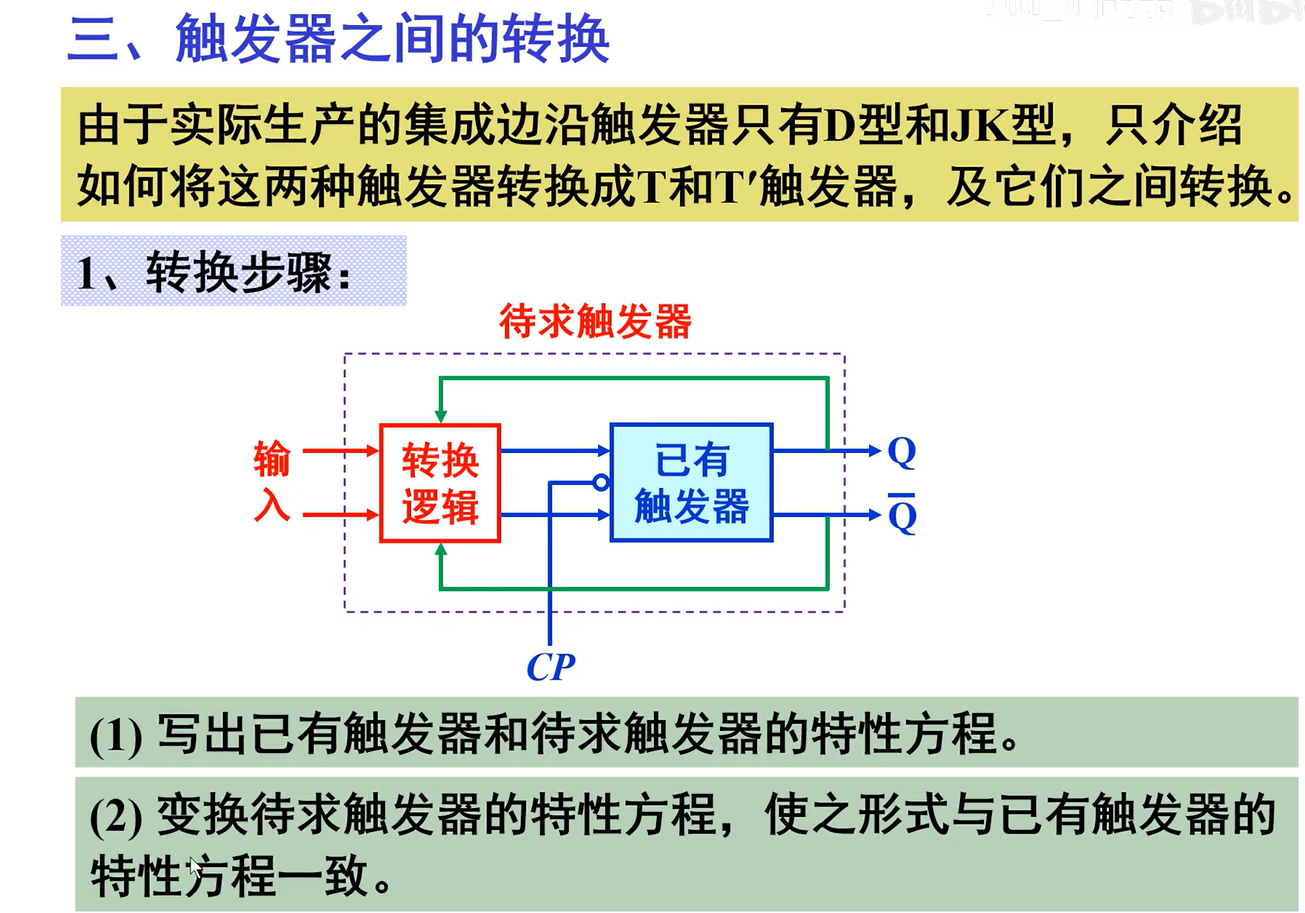

(3)求转换逻辑

(4)画电路图

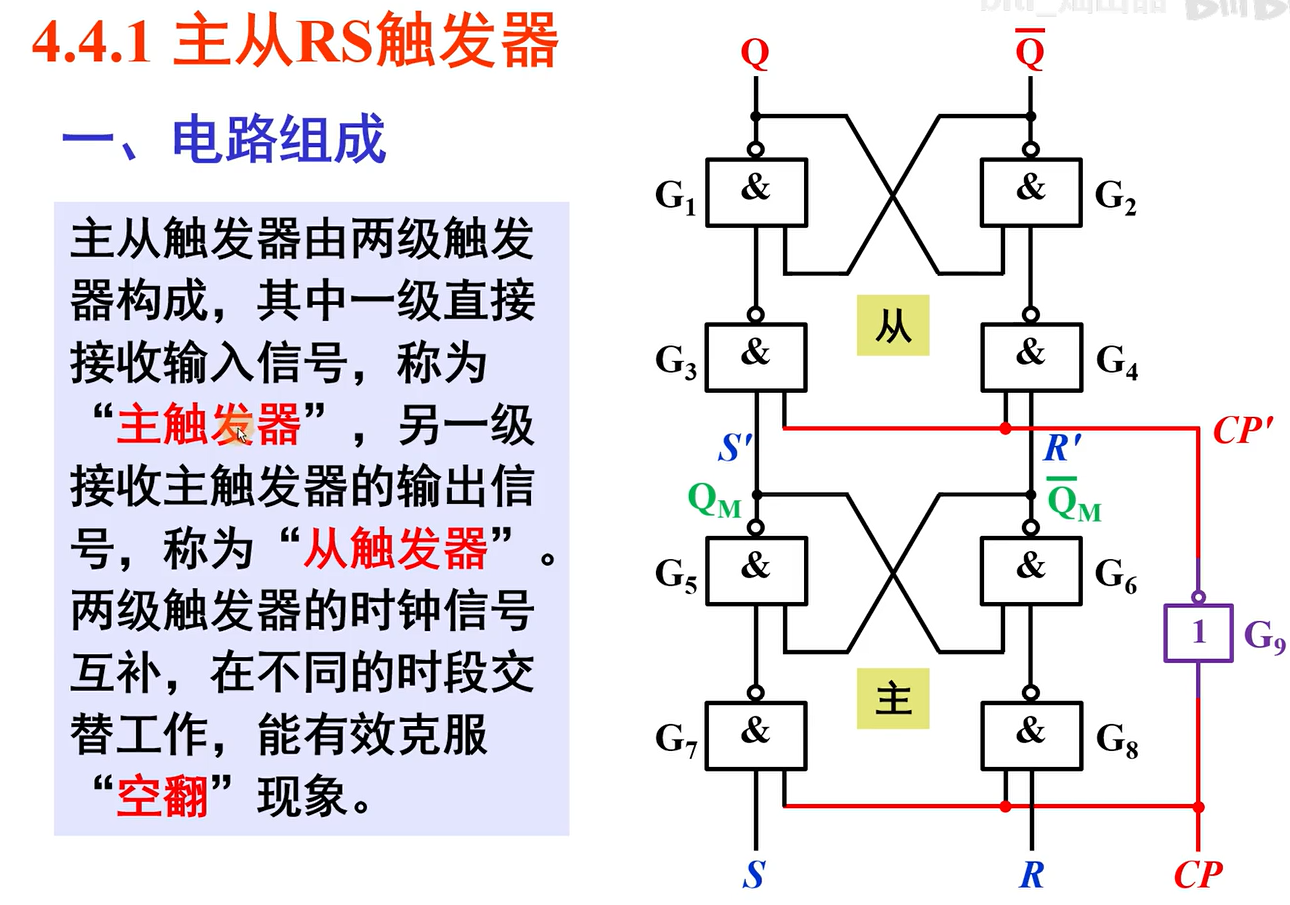

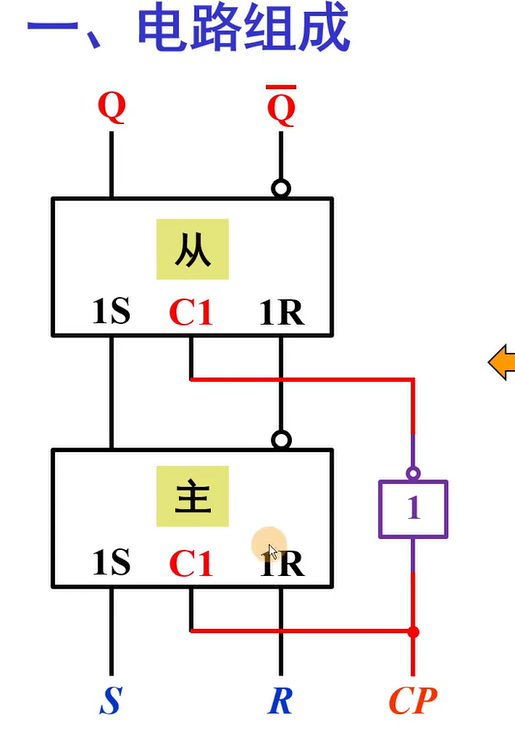

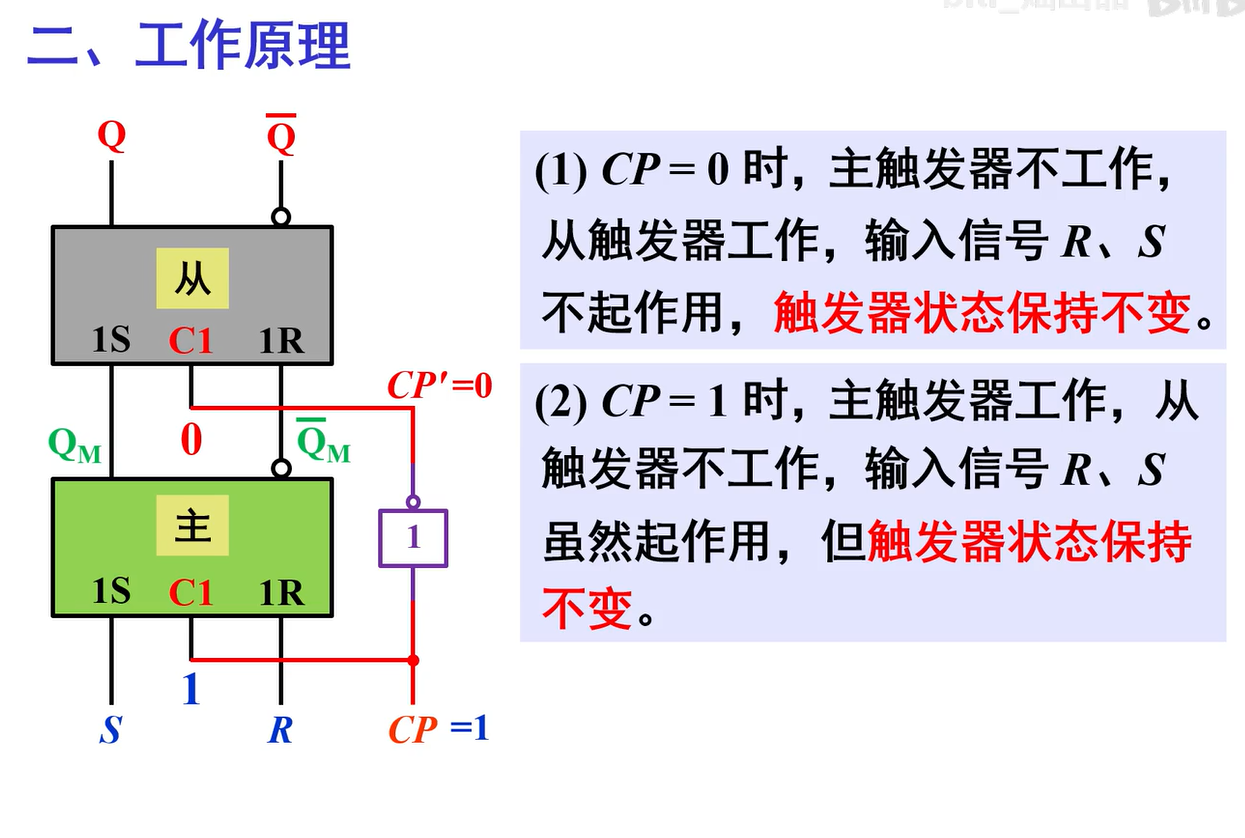

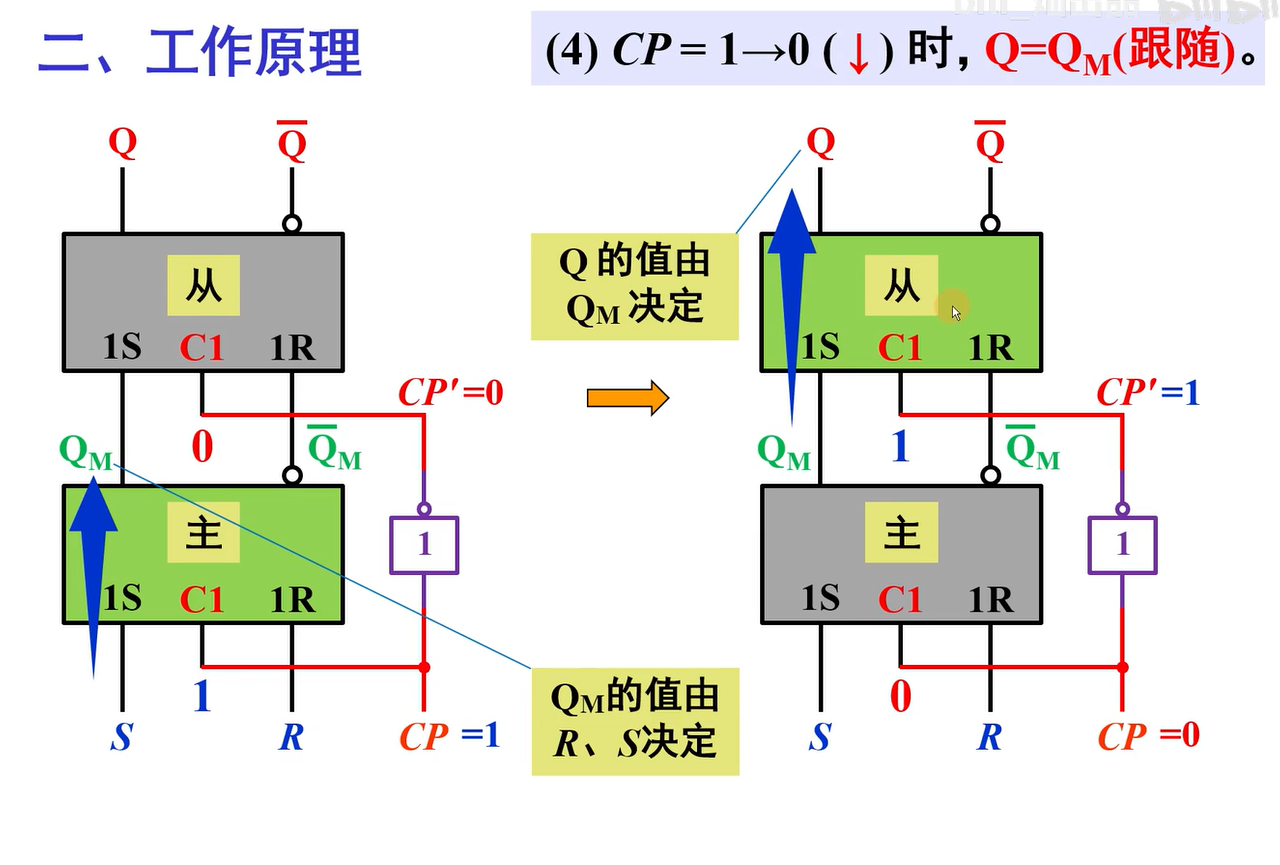

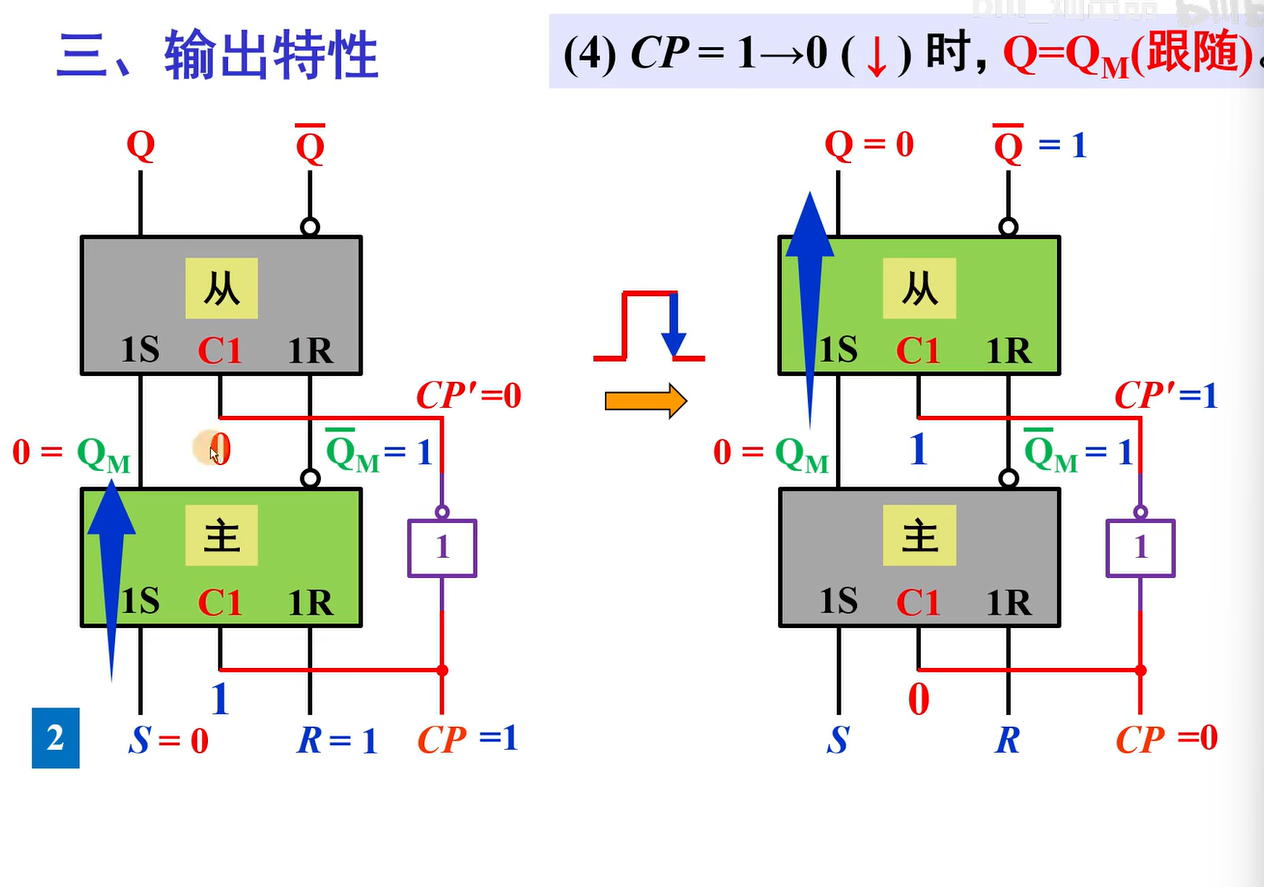

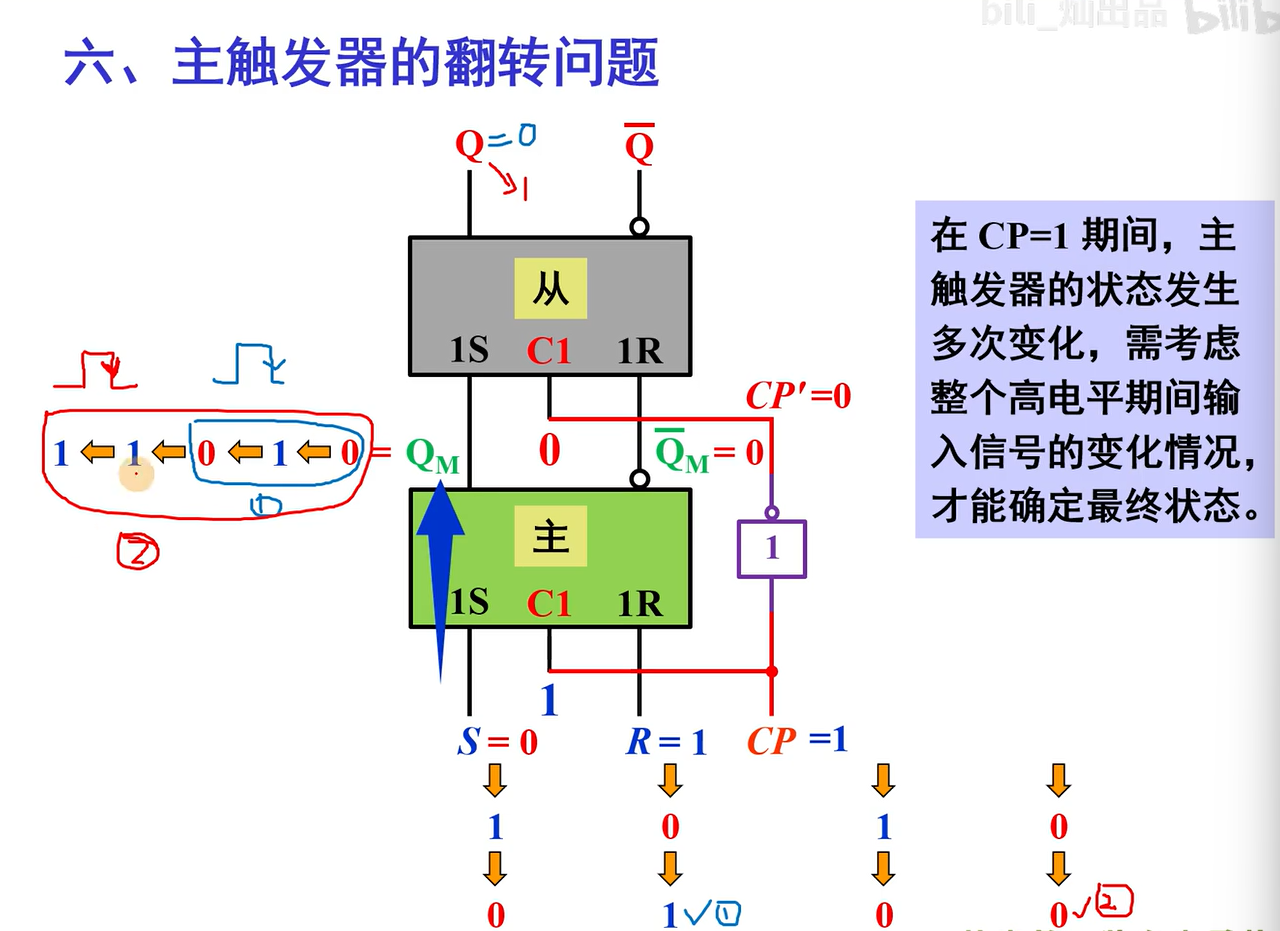

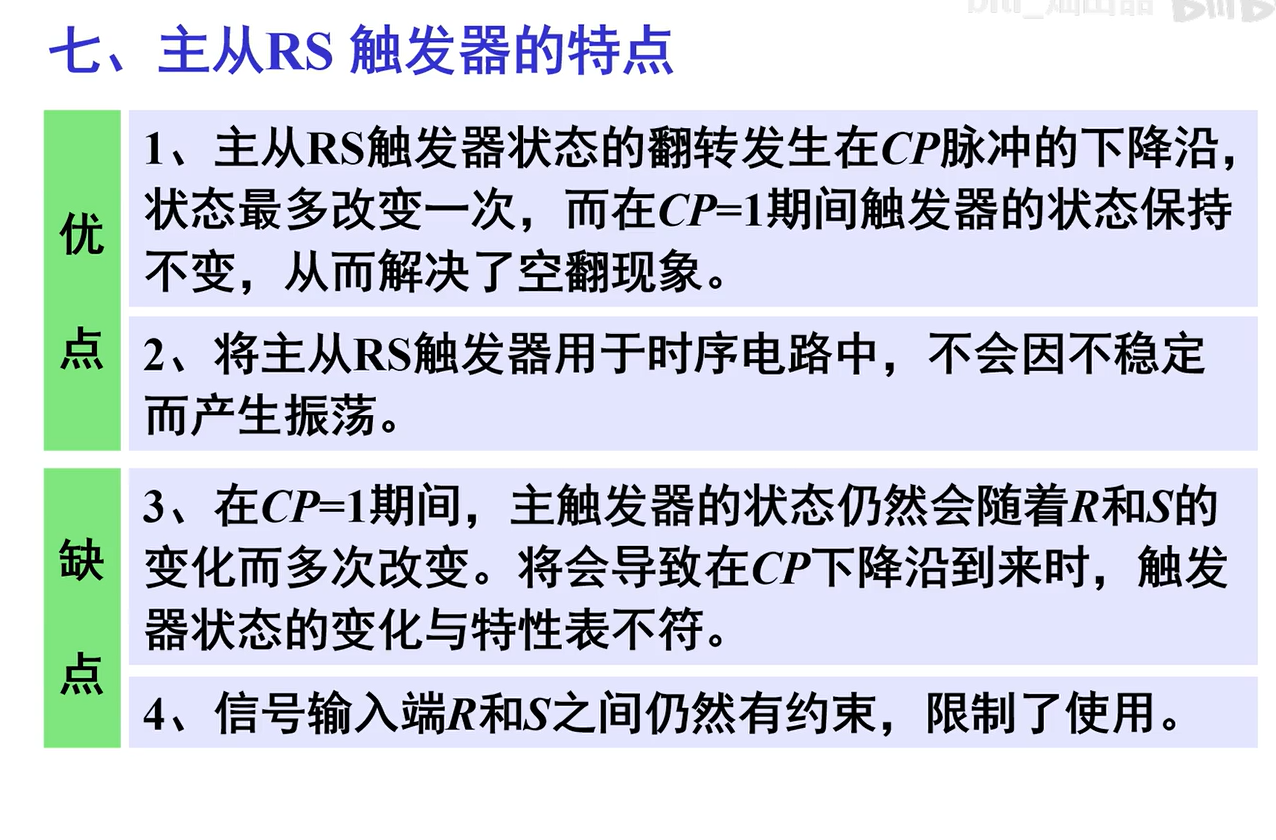

4.4主从触发器(脉冲触发器)

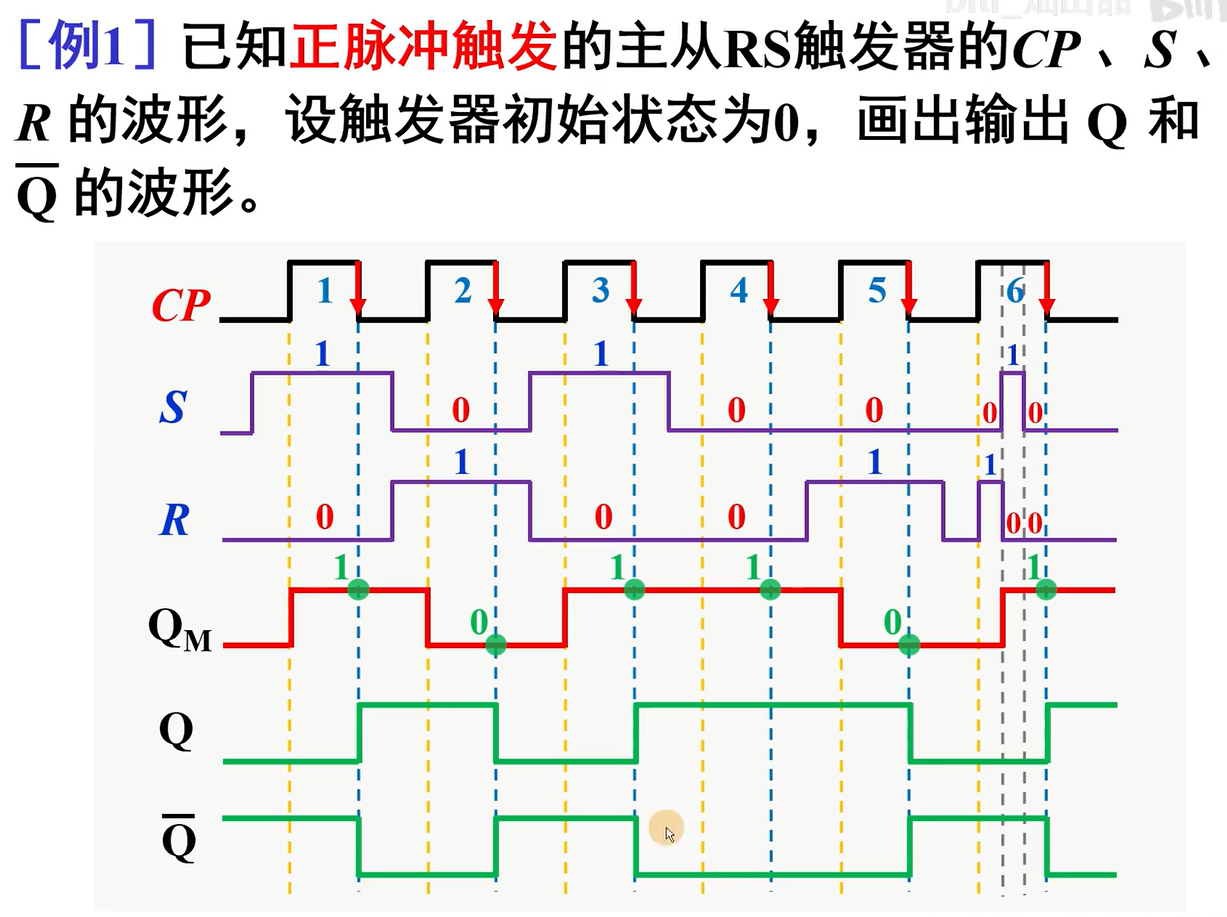

4.4.1 主从RS触发器

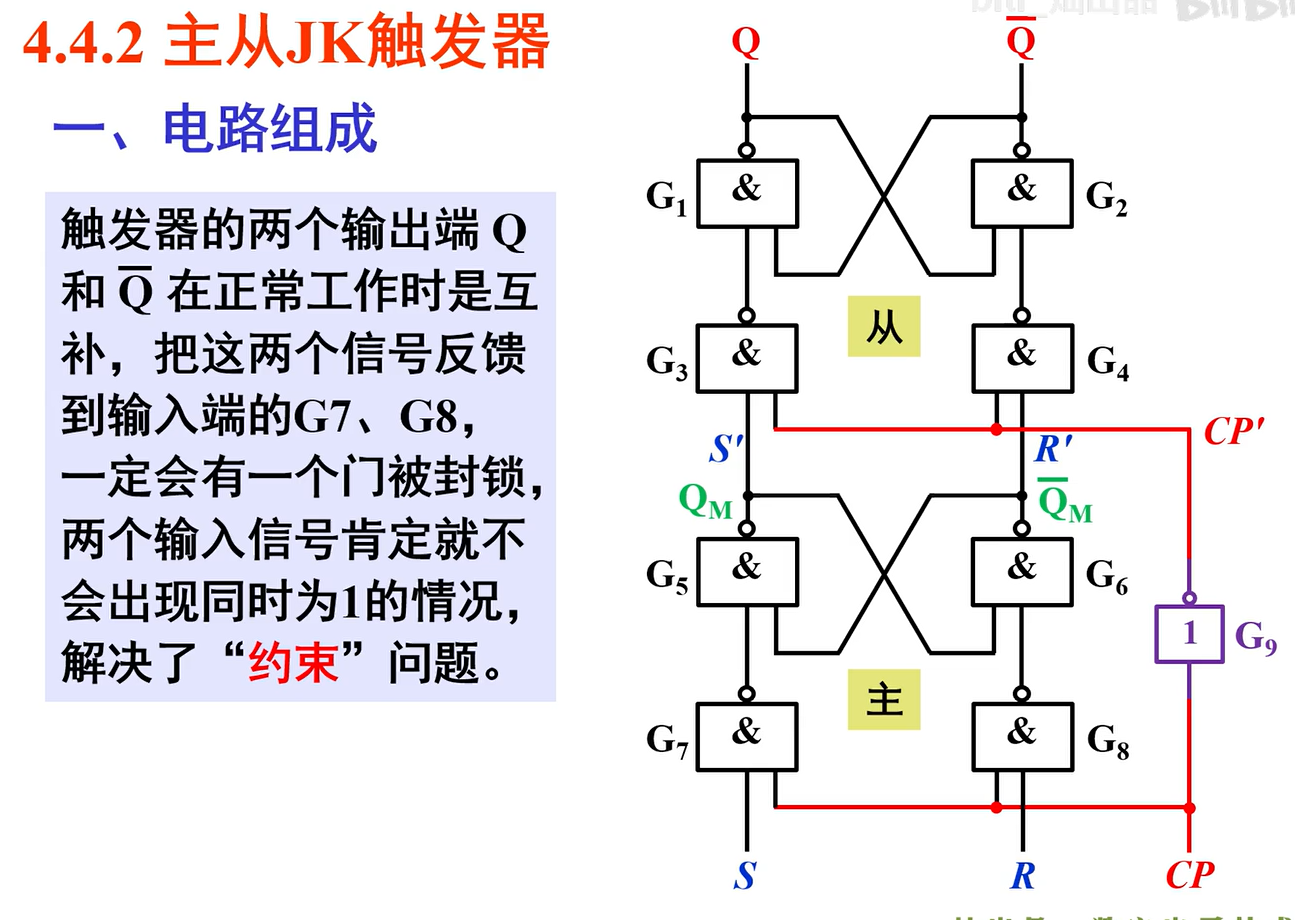

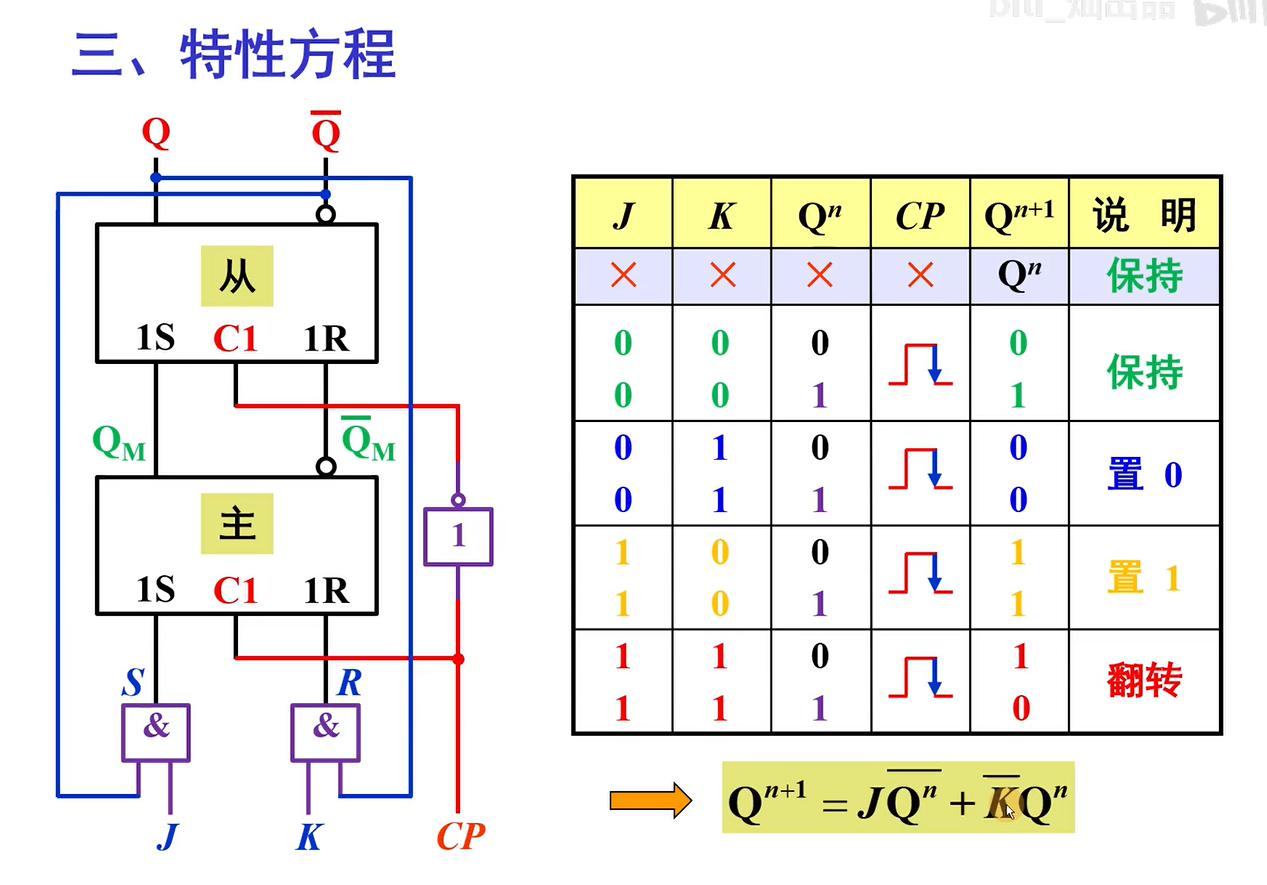

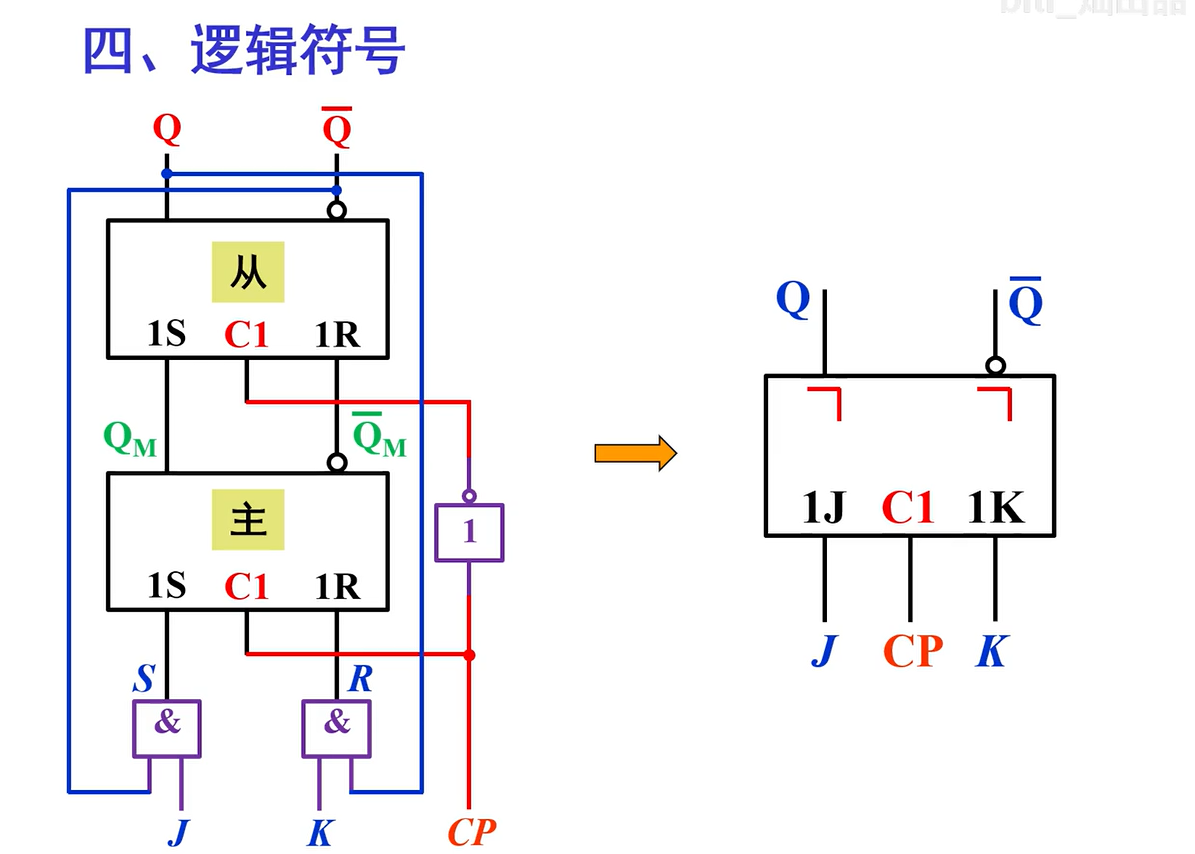

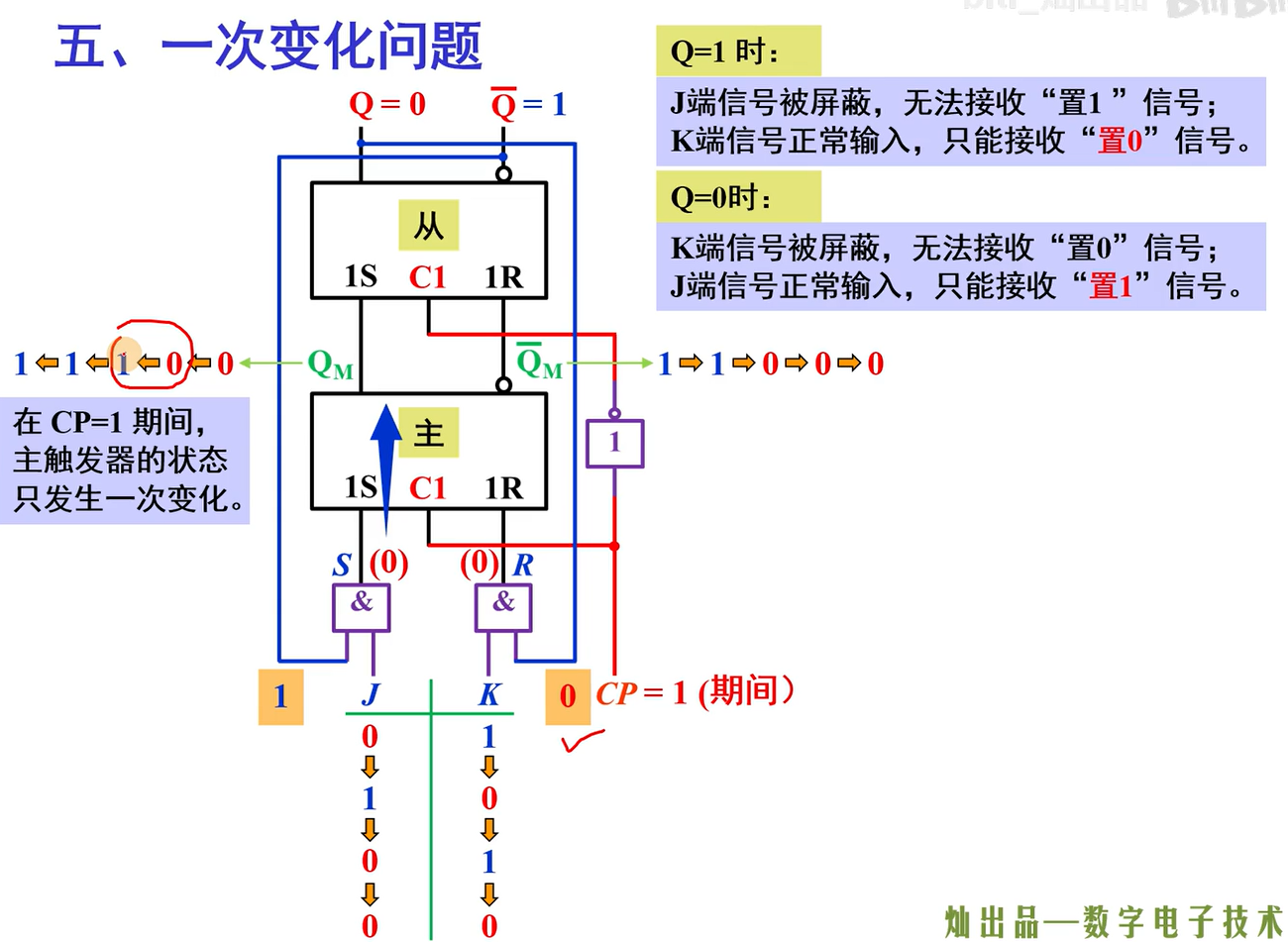

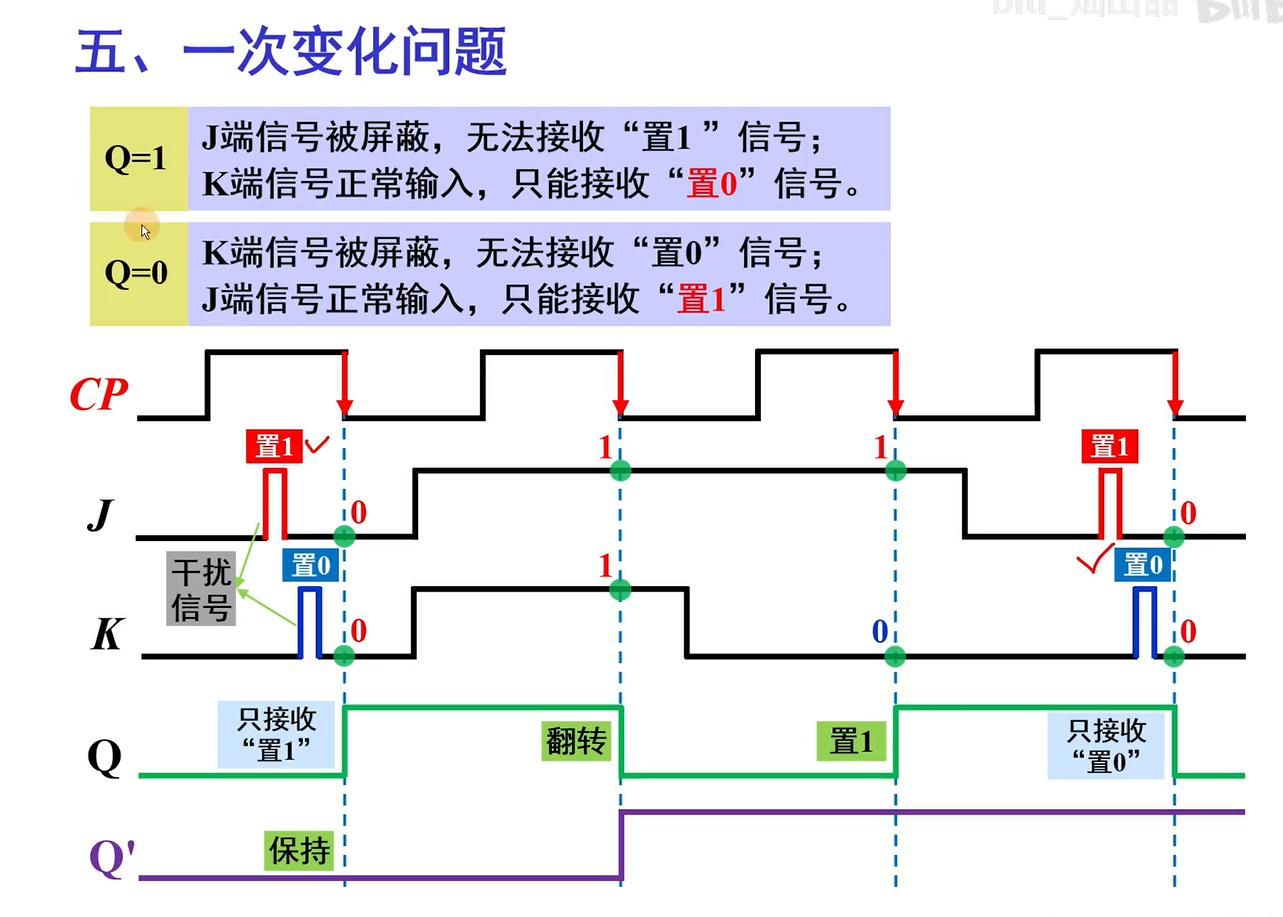

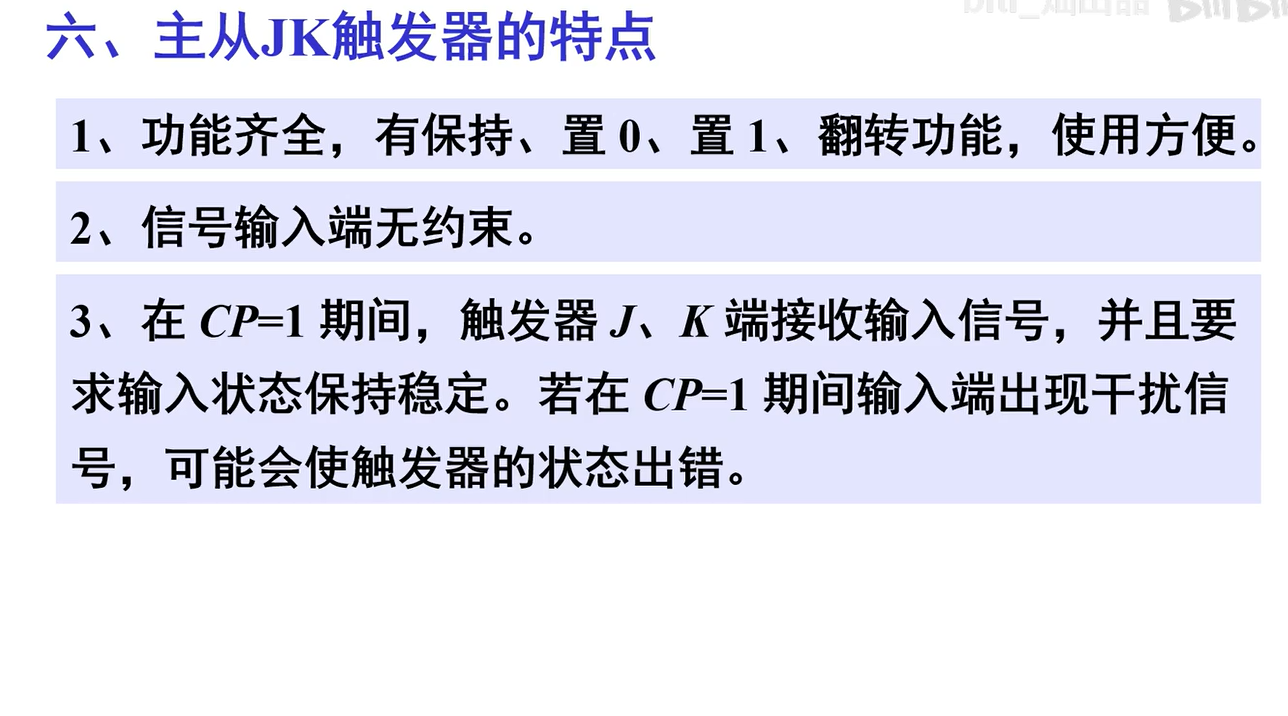

4.4.2 主从JK触发器

为了避免产生错误的一次反转,要求在CP=1期间J,K端的输入信号保持不变

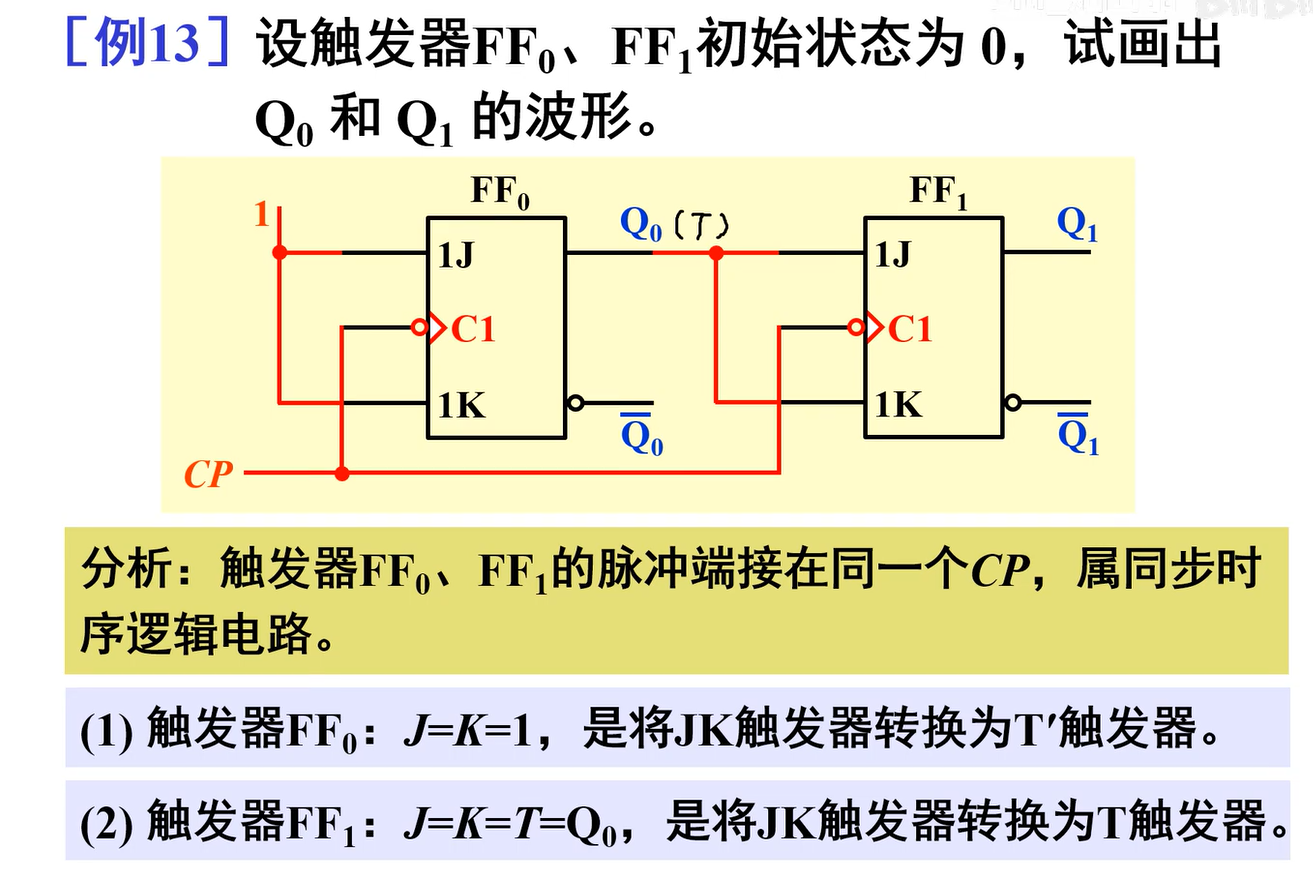

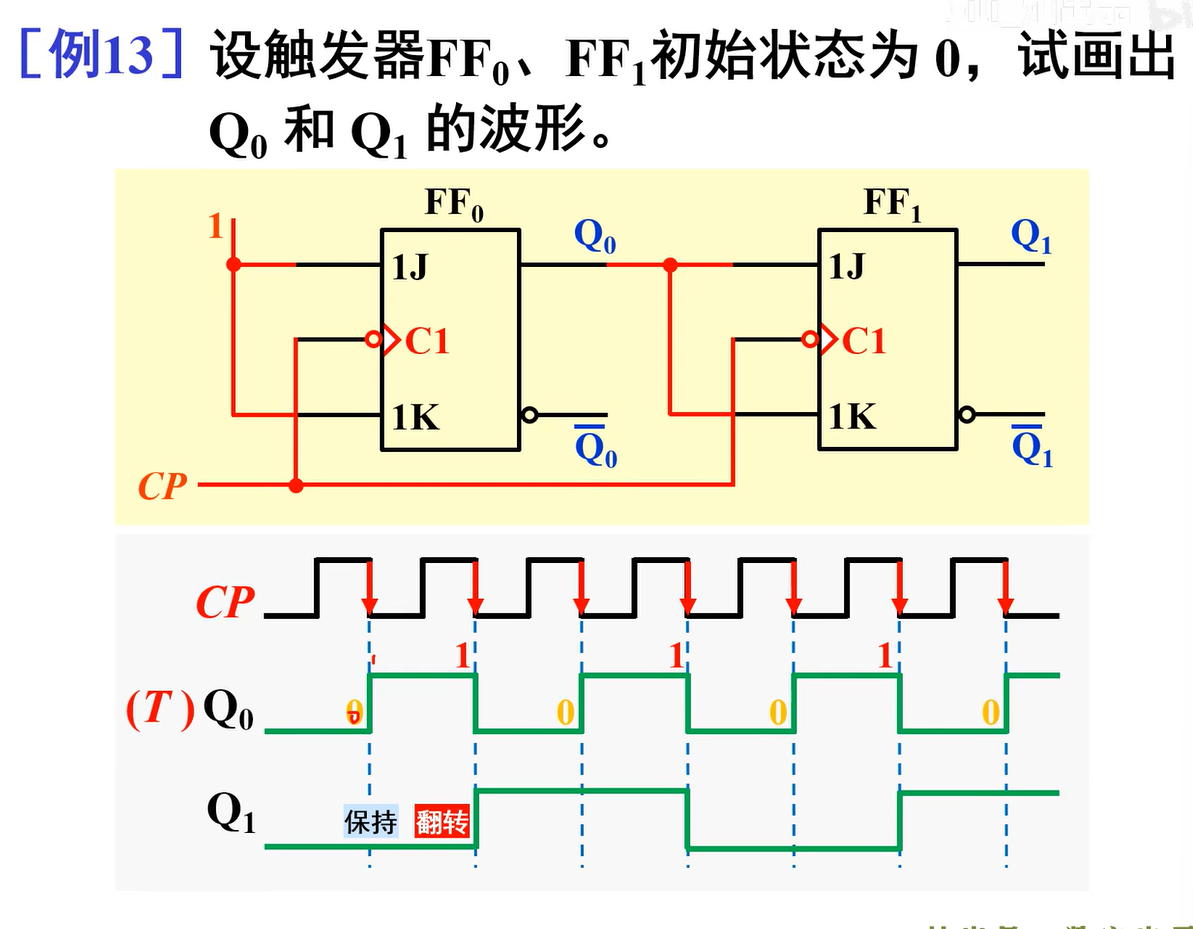

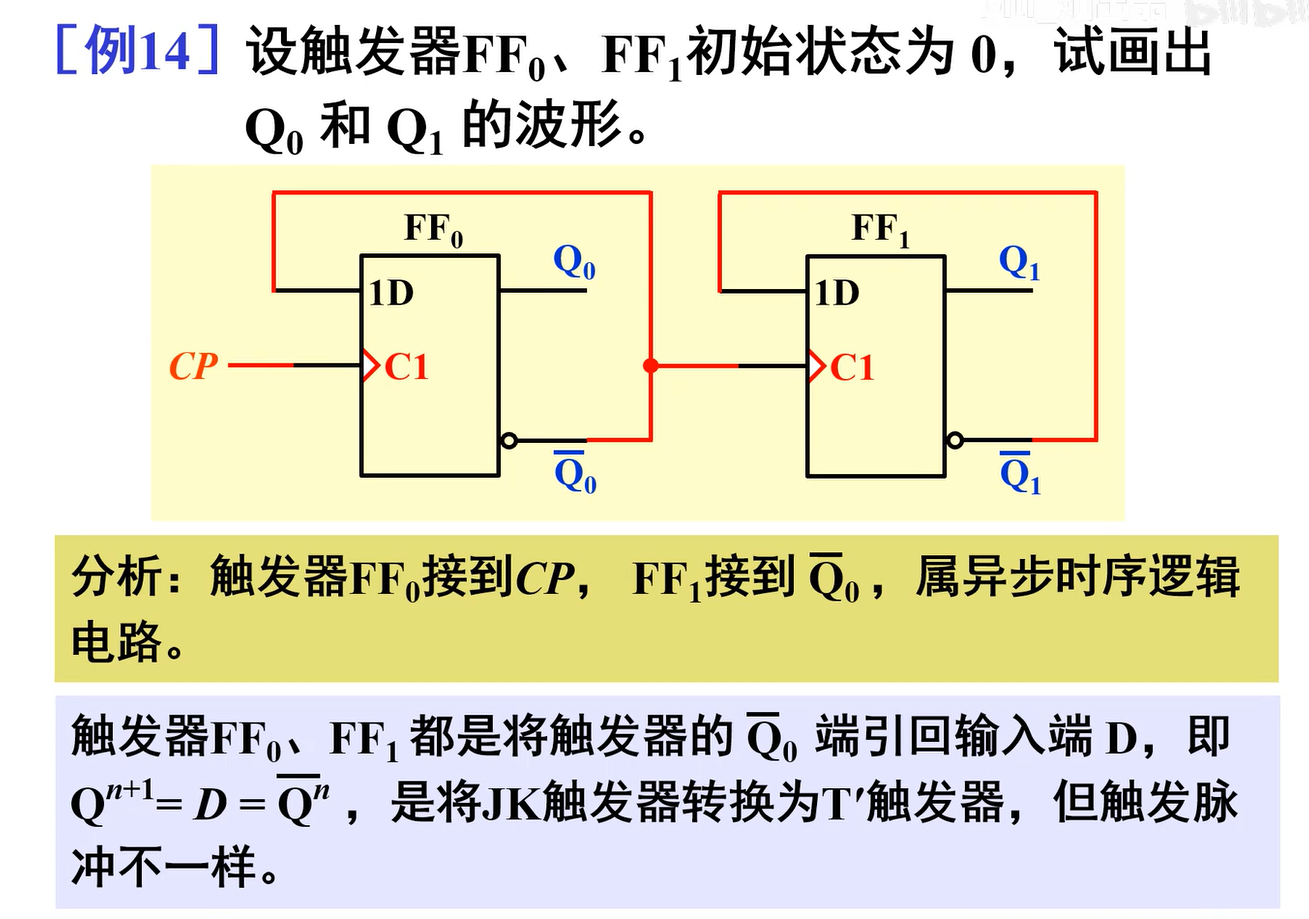

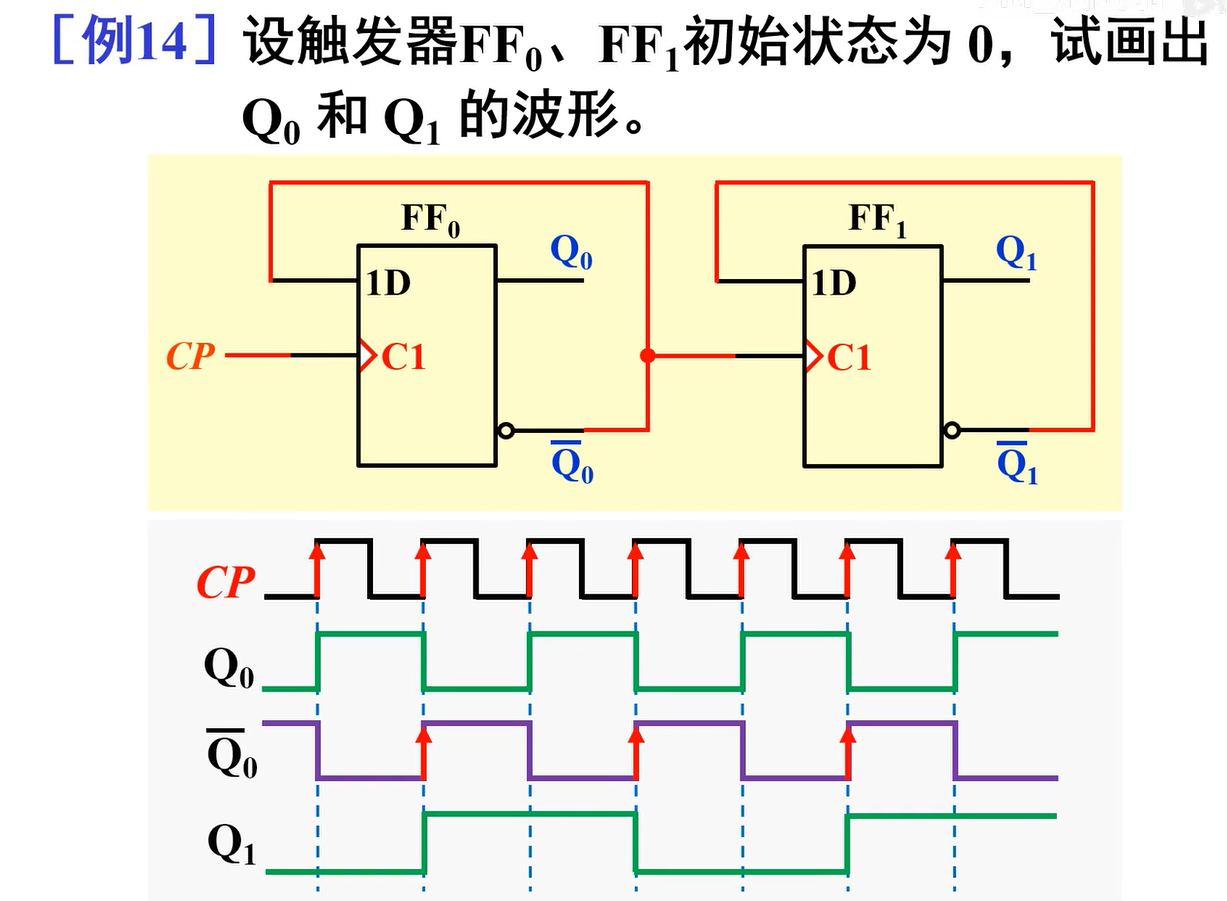

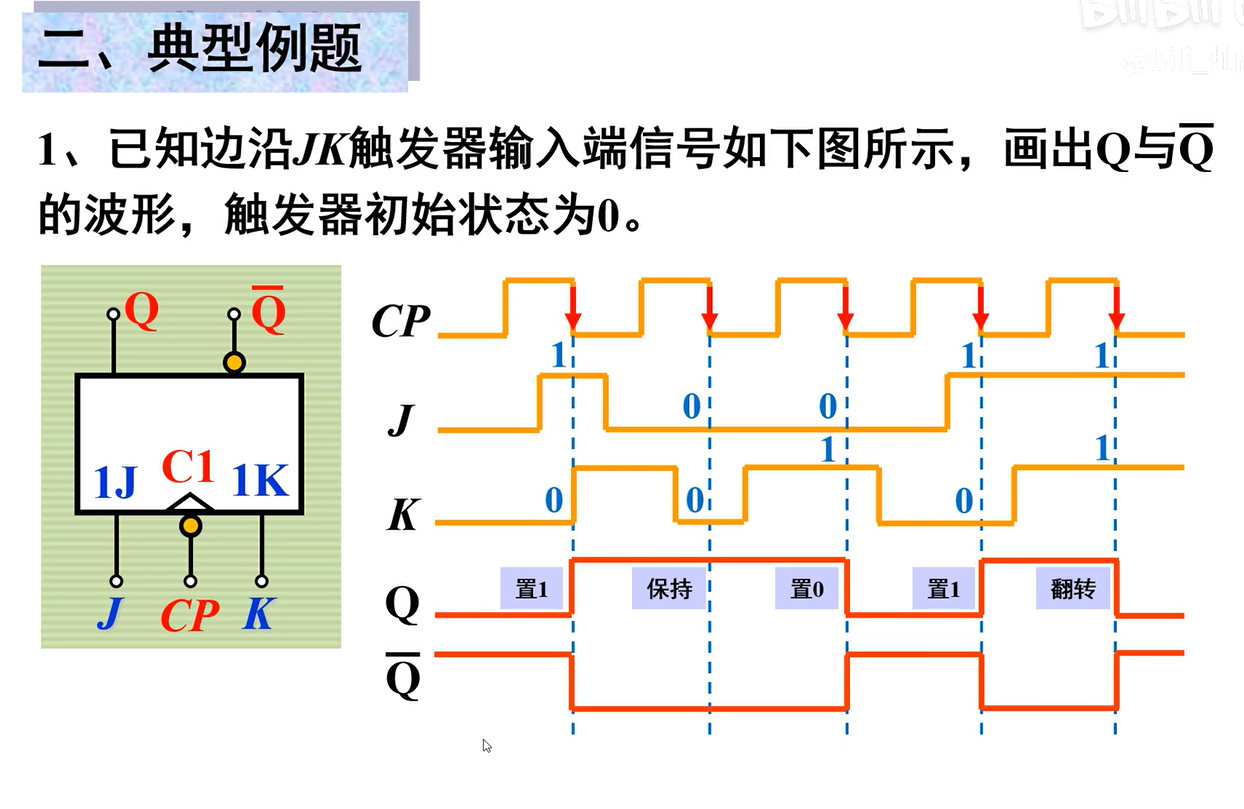

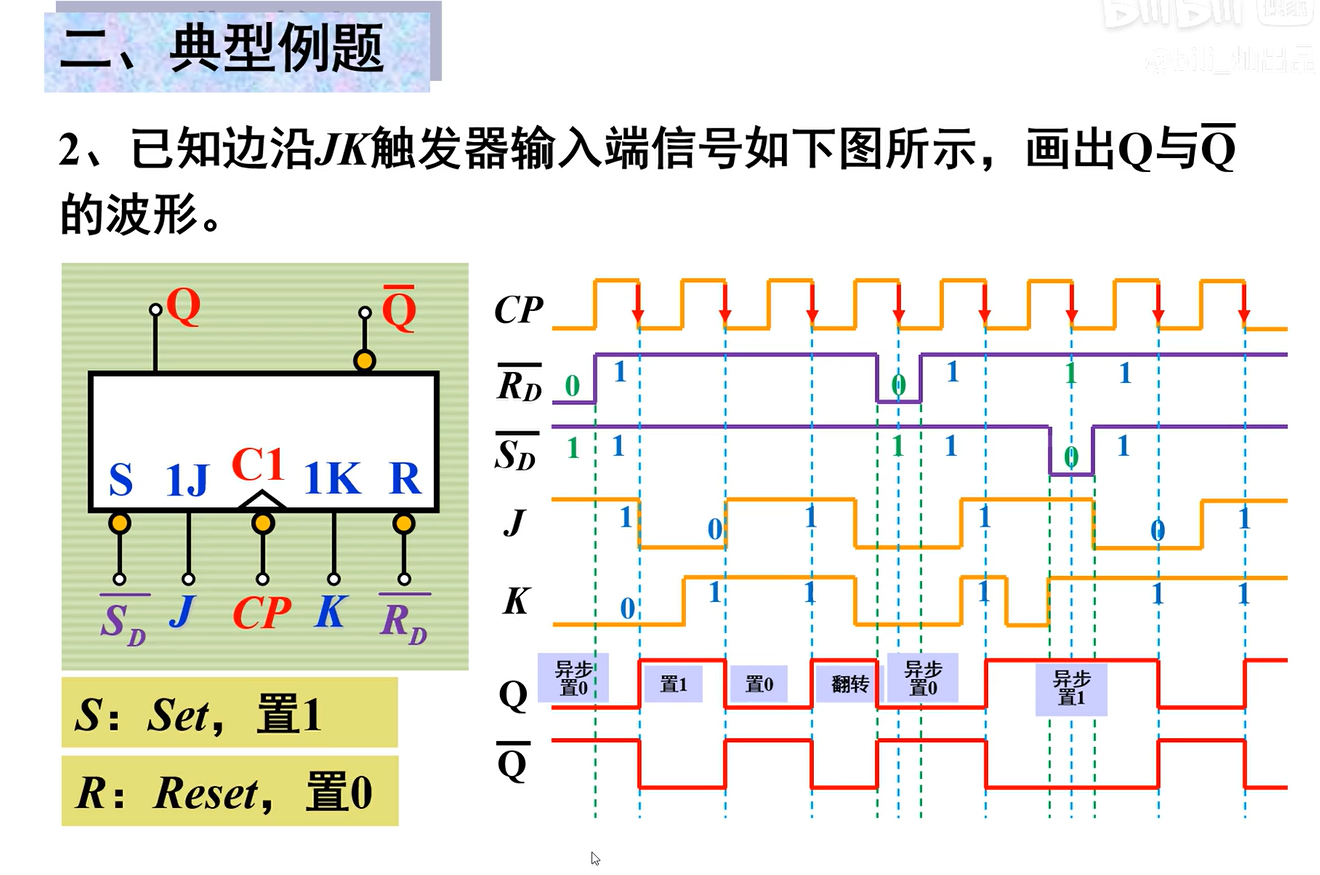

JK触发器典型例题

同步RS触发器——异步端修正

(3)异步输入端是用来预置触发器的初始状态,或在工作过程中强行置位和复位触发器,平时不工作时,SD非=RD非=1