最近在调试一个LVDS的屏显功能,涉及到了一些LVDS的东东,简单地整理如下,后续会再补充。

(1)对于altera FPGA(CYCLONE III)

1、对于作为LVDS传输的BANK必须接2.5V的VCCIO;

2、左右BANK(即1/2/5/6 BANK)的LVDS发送差分对信号无需外接匹配电阻,而上下BANK(即3/4/7/8 BANK)则需要,如果硬件工程师忘了,还可以在FPGA的IO引脚分配时里加端接电阻设置;

3、分配管脚时,左右BANK的LVDS差分信号脚在IO分配时选择的IO电平标准是LVDS,而上下BANK的LVDS差分信号脚在IO分配时选择的IO电平标准是LVDS_E_3R;

4、分配管脚时,只要指定LVDS信号的p端(+),则n端(-)会自动分配。在verilog代码中只要一个信号接口即可,无需在代码中定义一个差分对接口;

5、速度高时需用IP核(200MHz或400Mbps以上,串并转换器),在altera FPGA内使用的LVDS收发IP核是altlvds_rx和altlvds_tx,相应的IP使用说明在megawizard里有。

(2)对于xilinx FPGA

区别altera的地方在于首先在Verilog的代码里,xilinx的LVDS信号需要定义一对差分对信号,通过xilinx的原语进行差分对转单端或者单端转成差分对信号。另外在IO引脚分配时,xilinx的电平标准都是一样的,比如都是LVDS_33。

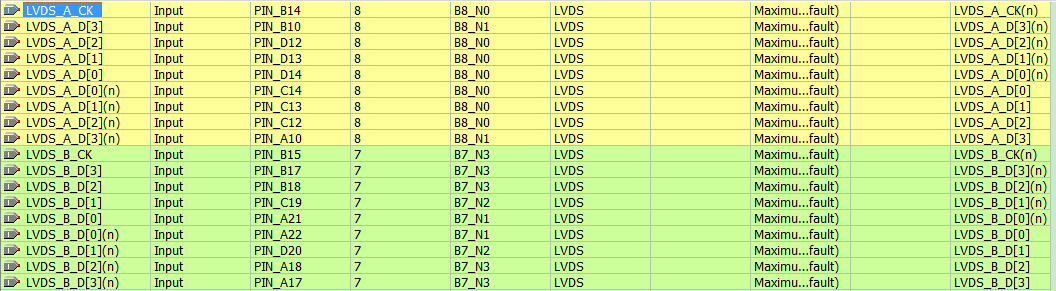

下图1是altera下的LVDS信号引脚分配,可见用户只需要分配p端(+)引脚即可。

图1 altera LVDS引脚分配情况

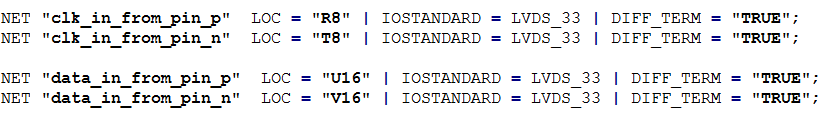

下图2是xilinx的LVDS信号引脚分配,xilinx的LVDS引脚区分p端和n端。当然在vivado下引脚分配可以只分配P端脚号,N端脚号会自动分配。而在代码里都需要写明差分对信号,再通过原语转成单端信号。

图2 xilinx下LVDS的引脚分配情况

浙公网安备 33010602011771号

浙公网安备 33010602011771号

LVDS是一种高速串行接口。速度一般都是几百MHZ以上。Altera低端的Cyclone IVE/Cyclone III的LVDS速度都可以达到800Mbps以上,高端的更能上到1.6Gbps。因此,IO的性能是远远比FPGA内部的LE性能要好的。这么高的速率情况下,你如果是用内部的LE来移位再输出到LVDS IO上,顶多能上到400Mbps(如果上DDIO的话)就已经不错了,再大的话是移不出来的。

这种情况下,你只有调用专用的串转并/并转串模块,也就是LVDS RX/TX模块。这个模块是专用的解串电路,跟Tranceiver有点像,但是功能没有Tranceiver多,性能没有它好。

了解上面一点后,你的问题其实就是数据对齐的问题了。你输入的是并行的数据,转成串行的数据以后,必然会有一个数据位对齐的问题。说来话有点多了,这个是高速链路的知识了。数据对齐有很多方式,Altera的LVDS模块就是用bitslip来控制的,bitslip是移位控制,在LVDS上电训练链路的那个时间,用bitslip来控制移位,发现如果不是训练码型的话就移一位直到能接收到正确的码型为止。

数据对齐还有另外一种方法。做LVDS接口的一般都有一个随路时钟,这个时钟是跟TX,RX的同源/同步的。移动这个时钟的相位也能起到数据对齐的作用。但是前提是时钟频率跟数据频率的比例和串行因子一定要是相等的。例如,数据频率是800Mbps,串行因子是8,那么参考时钟频率需要是100MHZ。