STM32知识点记录

1. 调试器

DAP全称Debug Access Port,是ARM提出的调试接口标准,专为Cortex-M系列微控制器设计。

常用的调试接口类型分为:JTAG(Joint Test Action Group,联合测试行动小组)和SWD(Serial Wire Debug,串行调试)。

JLink是SEGGER公司推出的JTAG仿真器。

STLink是意法半导体为STM8/STM32系列设计的集在线仿真与下载为一体的开发工具,支持JTAG/SWD/SWIM三种模式。

2. 烧录

单片机烧录方式可分为:ISP、ICP、IAP

- ISP(In-System Programming 在系统编程)

- 通过单片机内置的引导程序(Bootloader)和标准通信接口(如UART、SPI、I2C、USB等)实现程序烧录。

- 过程:单片机的标准通信接口连接PC的USB -> 拉高BOOT引脚 -> 复位单片机 -> 从Bootloader启动 -> 通过串口发送固件文件 -> Bootloader接收并写入Flash -> 复位/Bootloader自动跳转 -> BOOT引脚恢复低电平 -> 运行新程序

- 烧录时机:系统复位进入Bootloader

- 成本低,速递慢,依赖通用硬件。

- 适合量产后的固件升级。

- ICP (In-circuit programmer 在电路编程)

- 通过专用的编程器/调试器(如J-Link、ST-Link)直接访问单片机的调试接口(如SWD、JTAG),直接读写Flash/ROM。

- 烧录时机:芯片编程时

- 速度快,可靠性高,不能远程升级

- 适合工厂批量烧录程序、开发阶段调试。

- IAP(In-Application Programming 在应用编程)

- 运行时通过APP自行修改Flash中的其他程序区域。

- 烧录时机:APP运行时

- 需要划分Flash为多个区域,支持远程升级。

- 适用手机OTA升级、物联网设备无线更新。

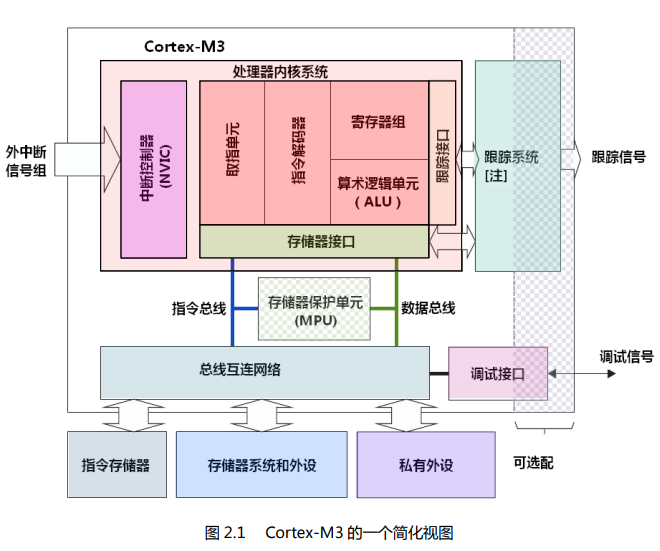

3. 硬件结构

- Cortex-M内核

- 处理器、寄存器、存储器接口都是32位。

- 独立的指令总线和数据总线,取指与数据访问可并行。

- 支持中断和调试

- 寄存器组

- R0 ~ R7 低组寄存器

- R8 ~ R12 高组寄存器

- R13 主堆栈指针MSP和进程堆栈指针PSP

- 堆栈指针的最低两位永远是 0,这意味着堆栈总是 4 字节对齐的

- 任一时刻只能使用其中的一个

- R14 链接寄存器LR :当呼叫一个子程序时,由 R14 存储返回地址

- R15 程序计数器PC:指向当前的程序地址

- NVIC:管理全部中断源

- MPU:管理存储器的访问权限

- 跟踪系统:实时输出程序运行过程信息,便于调试。

4. 单片机启动流程

① 上电/复位

② 系统从 0x0000 0000 地址读取两项内容:

-

第一个字(偏移 0x00):设置主堆栈指针 MSP(Main Stack Pointer)。

-

第二个字(偏移 0x04):设置程序入口地址(即复位中断向量 → Reset_Handler)。

③ startup_stm32f10x_hd.s

- 初始化栈大小、堆大小

- 执行向量表

- 执行SystemInit()函数 (system_stm32f10x.c)

- 初始化Flash接口

- 初始化PLL

- 初始化系统时钟

- 执行_main函数

- 全局/静态变量初始化

- 初始化堆栈

- 库函数初始化

- 程序跳转进入用户main()函数

5. 中断处理流程

| 类别 | 定义 | 示例 | 是否使用EXTI模块 |

| 外部中断 | 芯片外部的信号,通过引脚触发 | GPIO电平变化 | ✅ |

| 内部中断 | 芯片内部的外设或系统异常 | 定时器、USART 接收中断 | ❌ |

- GPIO线路连到EXTI控制器(外部中断控制器)

- EXTI设置触发方式(上升沿、下降沿)

- 中断源发出请求信号(IRQ)(外设拉高其中断请求线IRQx)

- NVIC 判断是否通过

NVIC_EnableIRQ()开启了该中断,优先级是否足够高 - 跳转到中断向量表中对应的 ISR(中断服务函数)

- 执行 ISR

- 清除中断标志防止重复触发

- 返回主程序

前2步是外部中断需要使用EXTI模块多出来的步骤,后面6步是共同步骤。

6. 轮询 vs 中断

都是处理外设事件的机制,但是轮询是主动询问,中断是被动打断。

轮询需要CPU循环检查外设状态,浪费资源等待,中断是外设主动通知CPU,只在需要时打断。

7. 位带操作

通过别名地址直接写入寄存器的某一比特位,不需要传统的“读-改-写”操作,防止在读写过程中被中断打断。

位带别名区把一个比特位膨胀成一个32位的字。

每个位带区的大小是1MB(0x000FFFFF字节)。

别名地址=位带别名区基地址+(字节偏移*32)+(位号*4)

#define BITBAND(addr,bitnum) ((addr & 0xF0000000) + 0x02000000 + ((addr & 0x000FFFFF) << 5) + (bitnum << 2))

8. GPIO和AFIO

GPIO控制每个引脚的模式和电平

AFIO控制每个引脚的复用功能

每个GPIO端口包含:

- 2个32位配置寄存器(GPIOx_CRL,GPIOx_CRH)

- 2个32位数据寄存器 (GPIOx_IDR和GPIOx_ODR)

- 1个32位置位/复位寄存器(GPIOx_BSRR)

- 1个16位复位寄存器(GPIOx_BRR)

- 1个32位锁定寄存器(GPIOx_LCKR) 当在一个端口位上执行了锁定(LOCK)程序,在下一次复位之前,将 不能再更改端口位的配置。

GPIO端口的每个位可以由软件分别配置成多种模式

| 模式 | 简介 | 电气特性 | 常用场景 |

| 🟦浮空输入 | 默认模式 | 容器受干扰 | 按键输入 |

| 🟩上拉输入 | 内部上拉电阻 | 默认高电平,外部可拉低 | 按键接 GND 时使用 |

| 🟨下拉输入 | 内部下拉电阻 | 默认低电平,外部可拉高 | 按键接 VCC 时使用 |

| ⬛模拟输入 | 禁用输入/输出缓冲器 | 抗干扰强 | ADC(模数转换)输入,如传感器 |

| 🟥推挽输出 | 上拉和下拉驱动 | 能输出高/低电平 | LED、蜂鸣器、普通控制输出 |

| 🟫开漏输出 | 只能输出低电平,高电平需外部上拉 | 多设备共享一线通信 | I²C 总线、多个设备输出同一引脚 |

| 🔵推挽复用 | 外设输出高/低电平 | USART TX、SPI SCK、PWM 等 | |

| ⚫开漏复用 | 需外部上拉电阻 | I²C SDA/SCL(典型应用) |

9. PWM

- 通过改变脉冲的宽度(占空比),调节输出电压的有效值。

- 适用于电机转速控制、LED亮度调节

10. DMA 直接存储器存取

- 提供在外设和存储器之间或者存储器和存储器之间的高速数据传输,无须CPU干预。

- 有一个仲裁器来协调各个DMA请求的优先权。

- 每个独立的通道都直接连接专用的硬件DMA请求。

- 每个通道都有3个事件标志(DMA半传输、DMA传输完成和DMA传输出错)。

- 数据区的传输宽度(字节、半字、全字),源和目标地址必须按数据传输宽度对齐。

访问冲突?

- CPU和DMA同时访问同一目标内存

- 总线仲裁机制会决定谁先访问

- DMA1 和 DMA2 同时访问同一目标

- 总线仲裁机制会决定谁先访问

- DMA1 中的通道1 和 通道2 同时访问同一目标

- 仲裁器处理访问顺序

常见应用场景

| 外设 | 应用场景 |

|---|---|

| USART | 接收大块串口数据 |

| ADC | 连续采样模拟信号、存入内存 |

| SPI/I²C | 批量数据收发 |

| DAC | 需要持续输出音频/波形 |

| 内存-to-内存 | 批量复制内存内容 |

🧩 DMA 和 CPU 的区别

| 项目 | CPU 传输 | DMA 传输 |

|---|---|---|

| 主体 | CPU 手动搬运 | DMA 自动搬运 |

| 效率 | 低(中断+搬运) | 高 |

| 实时性影响 | 高 | 低(CPU 空出做更重要任务) |

| 中断次数 | 多(每个字节) | 少(每次传输完成) |

10. ADC 和 DAC

- ADC 数字信号->模拟信号 传感器数据采集

- 12位分辨率 -> 转换后的数字精度(0~4095)-> 能辨别的最小模拟量 3.3V/2^12 ≈ 0.000806

-

DAC 模拟信号->数字信号 模拟输出、音频

- 转换方法:逐次逼近法(二分比较) 比较结果/(2^12-1) * V(REF) ≈ 电压值

11. 定时器

| 定时器类型 | 名称 | 特点 | 适用场景 |

|---|---|---|---|

| 🟥 高级控制定时器 | TIM1、TIM8 | 功能最强,支持互补PWM、死区、刹车 | 三相电机控制、高级PWM |

| 🟩 通用定时器 | TIM2、3、4、5 | 支持输入捕获、PWM输出等 | 普通PWM、编码器、电机测速 |

| 🟦 基本定时器 | TIM6、TIM7 | 仅含时间基准,无通道 | DAC 触发、周期性中断、ADC 触发 |

12. 看门狗

用来在系统失控时自动复位。

一种特殊的定时器:当它倒计时结束,如果你没喂狗(重装初值),它就会让系统复位!

- 独立看门狗 IWDG:使用独立的低速时钟 LSI,即使主系统锁死,它也能正常工作,启动后不能关闭,主要用于 防死机自动重启。

- 窗口看门狗 WWDG:运行在主频PCLK1上,需要在指定窗口期内喂狗,若喂得太早/太晚都会触发复位,启动后可软件关闭,用于检测任务调度是否错乱。

——————————————————————————

时钟极性 CPOL:空闲时的时钟信号高低

时钟相位 CPHA:哪个跳变沿开始采样 0 上升沿 1 下降沿

| CPOL | CPHA | 说明 |

| 0 | 0 | 空闲时处于低电平,在上升沿采样 |

| 0 | 1 | 空闲时处于低电平,在下降沿采样 |

| 1 | 0 | 空闲时处于高电平,在上升沿采样 |

| 1 | 1 | 空闲时处于高电平,在下降沿采样 |

——————————————————————————

| 通信方式 | 发送端和接收端 | 信号流 |

| 单工 | 固定,一端只能发一端只能收 | 单向 |

| 半双工 | 不固定,有切换延迟 | 双向,但不能同时 |

| 全双工 | 固定,双向都可收发 | 双向,允许同时 |

——————————————————————————

13. USART 通用同步异步收发器

最常用的点对点串行通信接口,适合芯片与某一外设之间进行稳定可靠的数据传输

基础结构:

| 项目 | 说明 |

|---|---|

| 引脚 | TX(发送)、RX(接收) |

| 波特率 | 9600、115200、1M 等 |

| 数据格式 | 起始位 + 数据位(通常8位)+ 可选奇偶校验 + 停止位 |

⚙️使用步骤:

- 使能 GPIO 和 USART 时钟

- 配置 TX 为复用推挽输出,RX 为浮空输入

- 设置波特率、数据格式

- 启用 USART 和中断或 DMA(可选)

- 收发数据

14. SPI 串行外设接口

芯片与外设之间最快速、最常用的同步通信方式

特点:

- 高速:高达几十 Mbps,远高于 I²C

- 全双工

- 主从同步串行通信

4 根基本信号线:

| 引脚 | 名称 | 作用 | 主设备方向 |

|---|---|---|---|

| SCLK | 时钟线 | 同步发送接收数据 | 输出 |

| MOSI | 主出从入 | 主机发给从机的数据 | 输出 |

| MISO | 主入从出 | 从机返回给主机的数据 | 输入 |

| NSS/CS | 片选信号线 | 确定和哪一个从机通信 | 输出 |

⚙️ 使用步骤

-

配置 SPI 工作模式(主机/从机、CPOL/CPHA 时序)

-

配置波特率、数据位数、方向等

-

配置 GPIO(复用模式 AF_PP)

-

启动 SPI 外设

-

使用发送/接收函数传输数据

15. I²C 内部集成总线

适合芯片和多个低速外设之间的通信

特点:

- 低速

- 半双工

- 多设备共享通信总线

2 根信号线:

| 引脚 | 名称 | 功能 | 特性 |

|---|---|---|---|

| SDA | 数据线 | 双向数据 | 需上拉电阻 |

| SCL | 时钟线 | 主机输出时钟 | 需上拉电阻 |

16. CAN 控制器局域网

适合多个设备之间可靠通信,一般与外部 CAN 收发器芯片 配合使用。

特点:

- 多主机

- 差分通信

- 支持仲裁和自动重发

****************************************************************

| 协议 | 同步性 | 通信方式 | 最少引脚 | 必要信号线 | 速率 | 主从结构 | 适用范围 | 特点 |

| UART | 异步 | 全双工 | 2 | TX、RX | 中等 | 点对点 | 调试、AT指令 | 通信距离短但稳定 |

| USART | 同步+异步 | 全双工 | 3 | TX、RX、CLK | 中等 | 主从 | ||

| SPI | 同步 | 全双工 | 4 | MOSI, MISO, SCLK, NSS/CS | 高 | 主从 | Flash、OLED、音频等大数据交换外设 | 高速 |

| I²C | 同步 | 半双工 | 2 | SDA, SCL | 低~中 | 多主多从 | RTC、EEPROM、传感器 | 节省引脚 |

| CAN | 同步 | 多播 | 2 | CANH, CANL | 中~高 | 多主多从 | 汽车、BMS、工业控制 | 带仲裁,抗干扰 |

信号线类型:

| 信号线 | 含义 |

|---|---|

| TX | Transmit,发送数据 |

| RX | Receive,接收数据 |

| SCLK / CLK | 时钟线(同步通信使用) |

| MOSI | 主设备输出,从设备输入 |

| MISO | 主设备输入,从设备输出 |

| NSS / CS | 从设备片选,主机拉低表示选中 |

| SDA | I²C 数据线,双向 |

| SCL | I²C 时钟线,由主设备控制 |

| CANH / CANL | CAN 差分对(需要收发器转换) |

| AINx | 模拟输入引脚(ADC) |

| DOUTx | 模拟输出引脚(DAC) |

****************************************************************

浙公网安备 33010602011771号

浙公网安备 33010602011771号