ARM芯片架构之CoreSight高效的系统架构规范

2025-10-10 15:29 tlnshuju 阅读(90) 评论(0) 收藏 举报CoreSight System Architecture 规范

说明

本文基于 ARM 官方CoreSight Architecture Specification v2.0(Part D)内容进行独立理解与二次创作,

仅用于个人学习与技术研究。

1. 概述

1.1 CoreSight 系统架构的定位

ARM 提供的系统级调试与追踪(Debug & Trace)框架。就是CoreSight

在多核 SoC(System-on-Chip)中,它为实时调试、事件追踪、功耗域隔离以及架构拓扑自描述提供统一方案。

与 Part B「可见组件架构」和 Part C「可复用组件架构」相比,Part D 专注于系统整体:

- 如何组织和连接所有 CoreSight 组件

- 如何被外部调试器自动识别

- 如何保证在不同电源/时钟域下安全运行

2. 系统设计原则

2.1 时钟与电源域

- 独立域划分:调试逻辑可与核心处理器、总线或外设分属不同功率域。

- 调试可见性:即便某个域被下电,调试器仍可访问剩余域的组件。

- 跨域同步:采用 AMBA APB/ATB 接口时需考虑跨时钟域的同步策略,保证 Trace 数据无丢失。

2.2 认证接口控制

CoreSight 在架构层面定义了Authentication Interface:

- 支持区分 安全入侵调试、非安全入侵调试、安全/非安全非入侵调试 四类权限。

- 系统必须提供集中化的控制逻辑,用于在 SoC 启动或安全模式切换时动态开关调试权限。

- 认证状态会映射到

AUTHSTATUS等只读寄存器,调试器可实时读取。

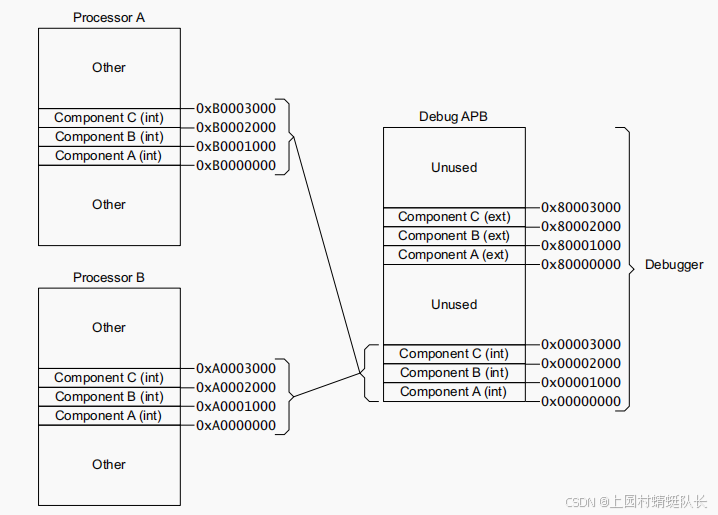

2.3 内外部访问隔离

Debug APB:CoreSight 建议通过 AMBA3 APB 访问控制寄存器。

Internal vs External:系统需区分来自片上软件与外部调试器的访问,以避免被应用程序误改。

可使用锁存寄存器(LAR/LSR)机制防止非预期写入。

3. 物理接口

CoreSight 支持多种与调试器连接的标准化物理接口:

| 接口类型 | 典型用途 | 特点 |

|---|---|---|

| ARM JTAG-20 | 传统边界扫描 | 兼容 IEEE 1149.1;引脚多但生态成熟 |

| CoreSight-10 / 20 | 高速 Trace | 引脚更少,支持串行/并行复用 |

| ARM MICTOR | 大带宽并行 Trace | 适合实验室高速采集 |

这些接口不仅是“电气规范”,还规定了信号分配、接地与屏蔽要求,以确保数百 Mbps 甚至 Gbps 级的 Trace 数据稳定传输。

4. Trace Formatter(追踪格式化器)

Trace Formatter 是系统级Trace Sinks的一部分,用于在数据输出前进行格式化与封包。

- 帧结构:采用时间戳、通道 ID、校验码等字段,保证多源 Trace 在下游器具中可重建。

- 运行模式:

- Continuous:持续输出,适合实时在线分析。

- Stop-on-Flush:在捕获结束后发送刷新帧,保证最后一批信息完整。

- 带宽调节:可根据下游缓冲区状态进行流控,避免因接口瓶颈导致 Trace 丢失。

5. ROM Table —— 系统级拓扑发现的核心

5.1 设计目标

ROM Table 是CoreSight 框架自描述机制的关键。调试器连接芯片后,

无需预存硬件信息即可“自发现”所有可调试组件的地址、类型和层次关系。

5.2 基本结构

- 存放位置:位于专用只读存储区,通过 Debug APB 可直接访问。

- 条目格式:每个 32-bit 入口包含目标组件基地址、指向下一级 ROM Table 的指针及有效标志。

- 层级组织:

- 一级表列出顶层组件或子表地址;

- 二级表递归描述子系统;

- 直到叶节点对应具体 CoreSight 组件(ETM、TPIU、STM 等)。

5.3 电源域 ID

ROM Table 每个条目可附带Power Domain ID:

- 调试器可据此判断组件是否处于上电状态。

- 便于在大 SoC 中实现“按需上电”调试,降低待机功耗。

5.4 自动检测流程

调试器执行以下步骤:

- 连接物理接口(JTAG/SWD/CoreSight-20)。

- 读取顶层 ROM Table,获取子表和组件基地址。

- 递归探测:依次访问每个子表,直至枚举完整拓扑。

- 读取识别寄存器:通过

CIDR/PIDR/DEVTYPE等确认组件类型与版本。

该流程保证即使芯片设计方未公开完整原理图,器具也能自动构建系统视图。

5.5 设计注意事项

- 对齐与大小:条目地址需 4 字节对齐;当组件窗口超过 4 KB 时,需在 PIDR 中标明

SIZE字段。 - 可扩展性:规范允许多达 960+ 入口的扩展表,满足超大 SoC 需求。

- 容错:调试器应在遇到无效或未上电条目时具备降级策略,避免扫描中断。

工程提示:ROM Table 的规划应在芯片早期设计阶段确定,否则后期改动会影响整个调试生态。

6. 框架级拓扑检测

“地图”,拓扑检测还需要实际“连线确认”:就是ROM Table 只

- 主从接口探测:调试器按照接口类型(ATB、Channel 等)激活并观察握手信号。

- 信号控制:仅需最小集信号(如 ATVALID、ATREADY)即可确认连通性。

- 算法:调试器依次对每个主接口施加激励,检测对应从接口响应,从而建立完整连接图。

7. 合规性与验证

CoreSight 规定系统必须满足的Compliance Criteria,以保证不同厂商组件可互操作:

- Debug 合规类:验证调试访问、锁存寄存器、认证接口等是否符合规范。

- Trace 合规类:验证 ATB 带宽、Trace Formatter 输出格式、时间戳精度。

- 多 DAP 拥护:在一个 SoC 上允许存在多个 Debug Access Port,要求地址映射和仲裁机制一致。

8. 工程实践与案例

- 移动 SoC:通常采用多级 ROM Table,顶层表只保留关键 Trace 入口,其余子系统在需求时动态上电。

- 服务器级多核处理器:大量核心共享 Trace Funnel 和 ETB,要求在拓扑检测算法中考虑带宽分级与同步。

- 汽车电子:安全要求高,认证接口必须与安全启动链集成,保证量产后可关闭入侵调试。

9. 结语

CoreSight System Architecture 提供了一种统一、可扩展、自动发现的调试基础设施。

无论是移动设备还是高性能服务器,它都能在保证安全和功耗控制的前提下,实现

跨厂商、跨组件的调试与实时追踪。

浙公网安备 33010602011771号

浙公网安备 33010602011771号