ARM芯片架构之CoreSight Programmers‘ Model 深入解析 - 实践

2025-10-09 13:09 tlnshuju 阅读(39) 评论(0) 收藏 举报CoreSight Programmers’ Model 深入解析

本章聚焦 CoreSight Programmers’ Model,这是 ARM调试体系的基石。它经过统一的寄存器框架,为所有调试与追踪组件提供一致的可编程接口,使硬件设计者、调试器厂商可以跨平台工作。

1. Programmers’ Model 的设计哲学

- 统一性:无论组件类型(ETM、CTI、Funnel),管理寄存器均放在最高 4KB 地址窗口,调试器可无需硬编码快速发现。

- 可扩展性:允许组件扩展到多块 4KB空间,同时保留固定的发现寄存器区域。

- 健壮性:规定 RAZ/WI、RES0/RES1 等读写规则,确保未来向后兼容。

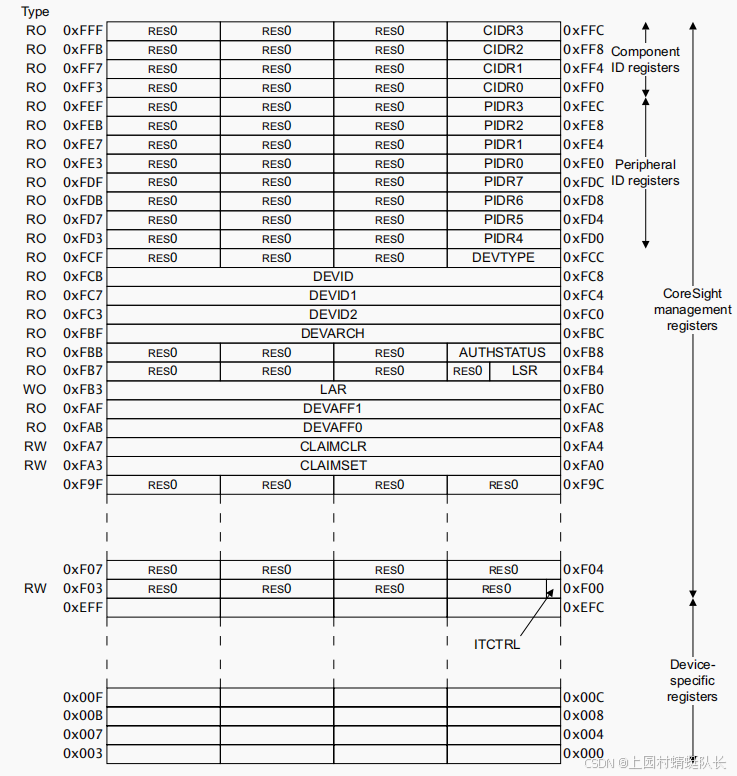

2. 地址空间与组件窗口

- 每个 CoreSight 组件必须映射至少4KB 地址空间。

- 若功能寄存器超过 4KB,可在低地址扩展,但0xF00–0xFFF区间必须保留标准管理寄存器。

2.1 多块组件支持

- 通过 SIZE 字段声明总空间块数。

- 最高块保留完整管理寄存器,调试器凭借 ROM Table 自动定位。

3. 通用管理寄存器

下表概述了所有 CoreSight 组件必须提供的关键寄存器:

| 偏移地址 | 寄存器 | 主要功能与说明 |

|---|---|---|

| 0xF00 | ITCTRL | 集成测试模式控制:进入/退出 Integration Mode,用于产测或系统级 Trace 路径验证,正常运行时应保持关闭。 |

| 0xFA0 | CLAIMSET | 声明调试器占用:设置相应位表示调试器正在使用该组件,用于多调试器协作避免访问冲突。 |

| 0xFA4 | CLAIMCLR | 释放调试器占用:清除对应位以释放资源。 |

| 0xFA8 | DEVAFF0 | 设备亲和性 0:标识该组件归属的 CPU 簇/NUMA 域,便于多核体系调试映射。 |

| 0xFAC | DEVAFF1 | 设备亲和性 1:与 DEVAFF0 配合,用于多簇/多核体系的组件归属识别。 |

| 0xFB0 | LAR | Lock 访问寄存器:写入特定解锁键值(如 0xC5ACCE55)以允许修改受保护寄存器。 |

| 0xFB4 | LSR | Lock 状态寄存器:只读,报告锁定状态及是否可写,用于安全访问控制。 |

| 0xFB8 | AUTHSTATUS | 安全认证状态:指示 Secure/Non-Secure 访问结果,结合 TrustZone 限制调试权限。 |

| 0xFBC | DEVARCH | 架构与厂商识别:提供架构版本、厂商 ID、设计版本号,驱动可据此选择兼容寄存器布局。 |

| 0xFC0~0xFC8 | DEVID* | 组件特性描述:说明该模块支持的 Trace 通道数、触发器数量等实现细节,不同 CoreSight 模块定义不同。 |

| 0xFCC | DEVTYPE | 设备类型:提供高层次的组件类别标识,与 DEVARCH 搭配快捷确定组件角色(Trace Source/Sink/Link)。 |

| 0xFD0~0xFEC | PIDR0–7 | 外设 ID:存储厂商、设计版本、修订号等信息,用于调试探测和芯片一致性验证。 |

| 0xFF0~0xFFC | CIDR0–3 | 组件 ID:识别组件是否符合 ARM CoreSight 规范,驱动据此判断寄存器块有效性。 |

在 CoreSight中,所有组件必须提供一组管理寄存器,位于其4KB地址窗口的最高0xF00–0xFFF 区间。下面详细解析关键寄存器及其设计要点。

3.1 集成测试与声明寄存器

- ITCTRL (0xF00):Integration Mode

Control,用于调试集成测试,支持在无完整框架时单独验证模块。 - CLAIMSET / CLAIMCLR (0xFA0 /

0xFA4):声明当前调试器已获取控制权,用于多调试器环境下的仲裁。

3.2 锁定机制

- LAR (0xFB0):Lock Access

Register,写入特定解锁键值(通常是0xC5ACCE55)后才能修改组件配置。 - LSR (0xFB4):Lock Status

Register,指示当前锁状态以及是否协助锁定作用。

> 设计建议:外部调试访问通常不受锁保护,但内部软件需在访问前解锁。

3.3 认证与安全

- AUTHSTATUS

(0xFB8):表现当前安全/非安全、侵入式/非侵入式调试的允许状态。- 位[7:6]:Secure Non-Invasive Debug (SNID)

- 位[5:4]:Secure Invasive Debug (SID)

- 位[3:2]:Non-secure Non-Invasive Debug (NSNID)

- 位[1:0]:Non-secure Invasive Debug (NSID)

3.4 设备架构与类型

- DEVARCH (0xFBC):提供架构 ID 与设计者 JEDEC 代码,如 ARM 为 0x23B。字段包括:

- ARCHITECT[31:21]:设计者 JEP106 编码

- PRESENT[20]:指示是否存在该寄存器

- REVISION[19:16]:架构版本

- ARCHID[15:0]:具体架构标识,如 ETMv4=0x4A13

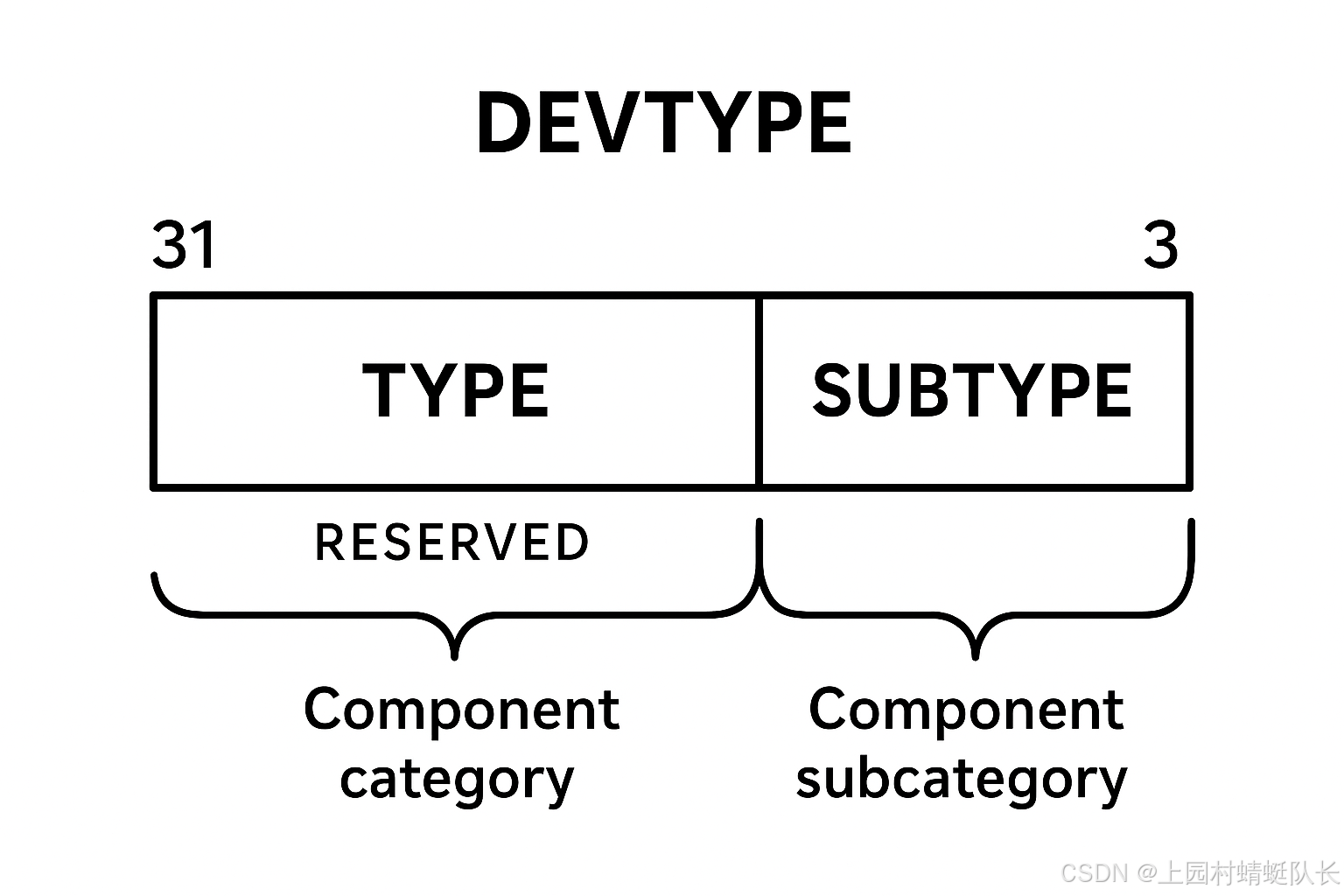

- DEVTYPE (0xFCC):区分模块效果类型。

- MAJOR[3:0]:主类型,如 Trace Sink(0x1)、Trace Link(0x2)、Trace Source(0x3)、Debug Control(0x4)。

- SUB[7:4]:子类型,如 TPIU=0x1、ETB=0x2。

3.5 设备配置与能力

- DEVID (0xFC8)、DEVID1 (0xFC4)、DEVID2 (0xFC0):厂商自定义寄存器,记录该组件的实现特性,例如缓冲深度、链路宽度等。

> 若组件可配置,这些寄存器应实时反映当前安装。

3.6 设备亲和性

- DEVAFF0 (0xFA8) 与 DEVAFF1 (0xFAC):用于描述与其它组件的唯一绑定关系,例如 ETM与处理器核心的对应。调试器行通过比较这些寄存器自动识别配对关系。

3.7 外设与组件识别

- PIDR0–PIDR7 (0xFE0–0xFDC):Peripheral ID Registers,提供 JEDEC厂商号、部件号、版本信息。

- CIDR0–CIDR3 (0xFF0–0xFFC):Component ID Registers,涵盖类别(CLASS) 和固定前导码,用于确认该模块属于 CoreSight架构并判断其类(如 0x9 代表 CoreSight 组件)。

4. 访问规则与安全机制

- RAZ/WI:未搭建位读零写忽略。

- RES0/RES1:保留位读出固定值,写入无效。

- 安全调试需配合 SoC 级 TrustZone 信号与 DAP 配置。

5. 组件类别与调试流程

- Class 0x1:ROM Table

- Class 0x9:CoreSight Component

- Class 0xF:PrimeCell/Legacy 组件

调试器借助 ROM Table 递归遍历组件树,利用 PIDR/CIDR自动发现所有可调试单元。

6. 硬件设计要点

- 电源域:管理寄存器应保持独立电源,确保在核心下电时仍可访问。

- 时钟域:为降低功耗,可单独为调试模块调整时钟门控。

- 版图布局:保证 ATB 链路的时序和信号完整性,避免高速 trace 丢包。

7. 与调试器的交互示例

- 调试器读取 ROM Table 获取组件基址。

- 读取 CIDR 确认组件类别。

- 读取 DEVARCH/DEVTYPE 确认具体能力。

- 根据 DEVAFF0/1 建立 CPU–ETM 配对。

- 借助 LAR 解锁并配置 Trace。

结语

Programmers’ Model以标准化寄存器框架为核心,使得跨厂商、跨平台的调试器得以在无需定制的情况下高效发现和运行

CoreSight 组件。理解这些寄存器及其访问规则,是硬件工程师构建可调试 SoC的基础。

浙公网安备 33010602011771号

浙公网安备 33010602011771号