FPGA时序逻辑电路设计实战:计数器原理与Vivado构建

2025-10-04 15:50 tlnshuju 阅读(130) 评论(0) 收藏 举报文章目录

概要

本文将通过一个LED闪烁控制实例,详细讲解FPGA中时序逻辑电路的设计方法,重点介绍计数器的原理、Verilog实现及Vivado编写流程。

整体架构流程

一、时序逻辑电路概述

时序逻辑电路与组合逻辑电路的根本区别在于:时序逻辑电路的输出不仅取决于当前输入,还与电路的前一状态相关。这种"记忆"功能使得时序逻辑能够实现计数器、状态机等艰难功能。

核心特点:

- 含有存储元件(触发器)

- 具有状态保持能力

- 输出与时钟信号同步

- 适用于需要记忆功能的应用

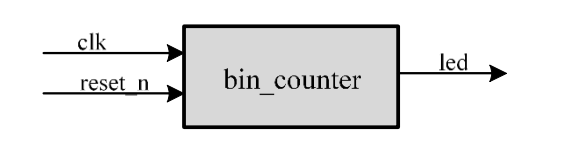

二、 项目需求分析

设计目标:实现一个计数器,控制LED每500ms翻转一次

硬件参数:

1、晶振频率:50MHz

2、时钟周期:20ns

3、LED控制:高电平点亮

设计一个计数器,使学习板上的 LED 状态每 500ms 翻转一次。学习板上晶振为 50MHz,也就是说时钟周期为 20ns,这样可以计算得出 500ms = 500_000_000ns /20ns = 25_000_000,即需要计数器计数 25_000_000 次,也就是需要一个至少 25 位的计数器(225>25_000_000>224)。且每当计数次数达到需要清零并重新计数。

具体计算:

500ms = 500,000,000ns

计数次数 = 500,000,000ns / 20ns = 25,000,000次

计数器位宽:25位(2^25 = 33,554,432 > 25,000,000)

三、 计数器工作原理

计数器是时序逻辑电路的典型代表,重要由以下部件构成:

3.1 核心组件

1、触发器:存储计数状态

2、加法器:实现计数功能

3、比较器:检测计数终值

4、选择器:控制计数清零

3.2 电路结构

计数器的核心元件是触发器,基本功能是对脉冲进行计数,其所能记忆脉冲最大的数目称为该计数器的模/值。计数器常用在分频、定时等处。计数器的种类很多,按照计数方式的不同许可分为二进制计数器、十进制计数器以及任意进制计数器,按照触发器的时钟脉冲信号来源可分为同步计数器与异步计数器。按照计数增减可分为加法计数器、减法计数器以及可逆计数器。

Verilog HDL 之所以被称为硬件电路描述语言,就是因为我们不是在类似 C一样进行普通的编程,而是在编写一个实际的硬件电路。下面将设计一个计数器,借助计数器控制一个 led 闪烁。上面提到计数器即为加法器、比较器、寄存器以及选择器构成,如下图所示。

下面是计数器控制 led 逻辑电路设计图:

ACZ702 EDA 扩展板 LED 硬件电路如下图所示,可以看出当控制端输出高

电平时 LED 亮。这里只需要每当计数器值记满后,翻转 LED 的控制端即可实现

LED 按照要求亮灭。

LED 电路原理图:

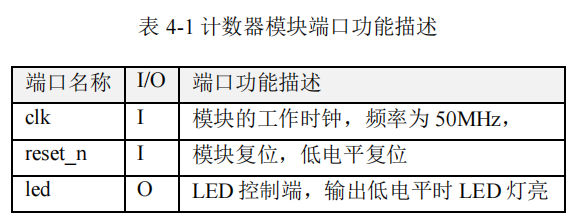

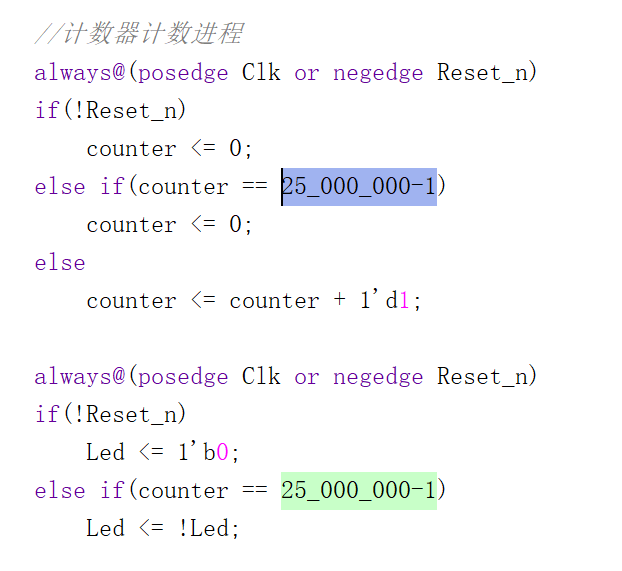

四、 Verilog代码实现

下面是Verilog代码:

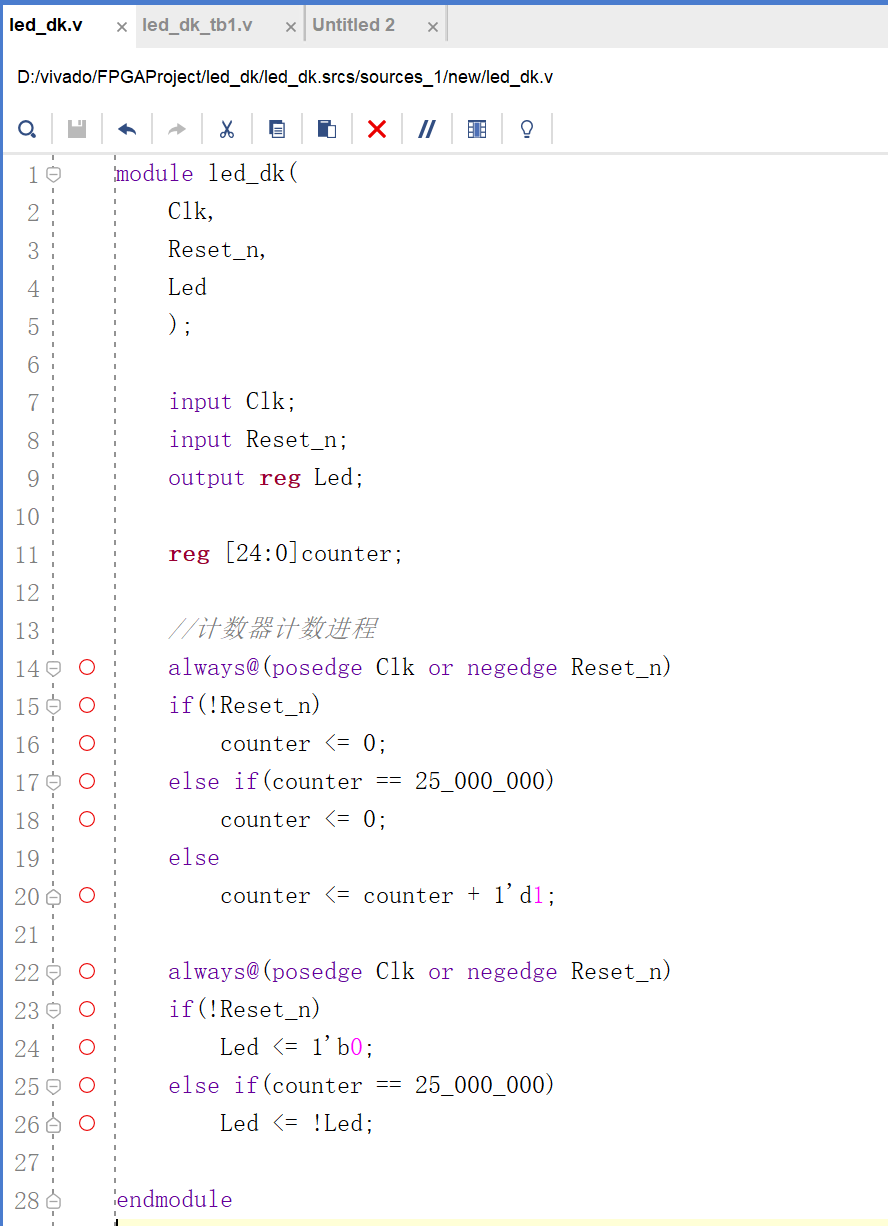

五、 仿真测试

5.1Verilog代码设计

5.2 激励仿真测试

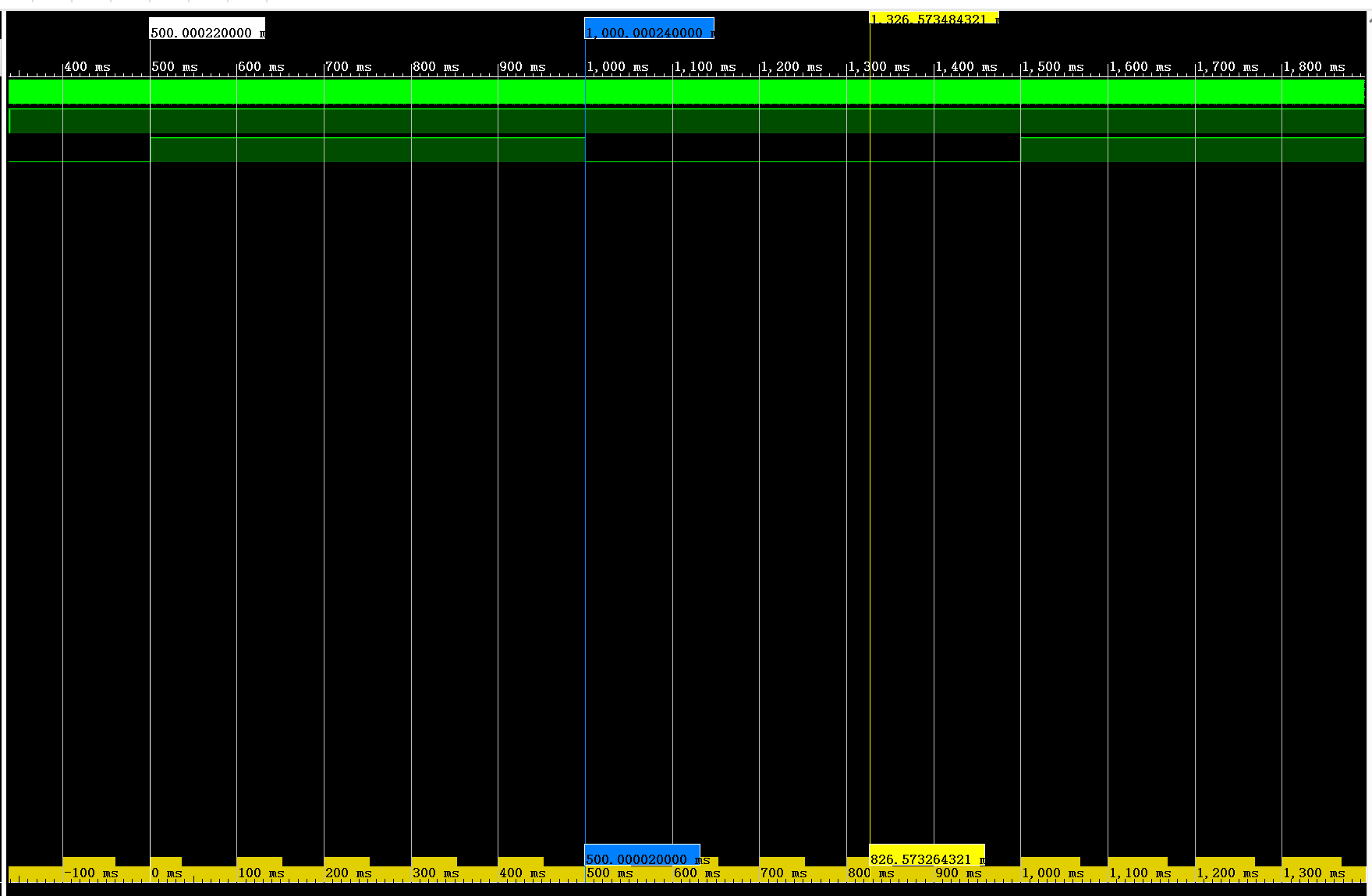

可以看到 如下图 所 示 的 波 形 。 可 以 看 出 高 低 电 平 变 化 的 时 间 是

500020000ns ,多了20ns,不符合既定的设计要求,要修改代码。

修改代码如下:

可以看到 如下图 所 示 的 波 形 。 可 以 看 出 高 低 电 平 变 化 的 时 间 均 是

500000000ns 也就是 500ms,符合既定的设计要求,至此能力仿真结束。

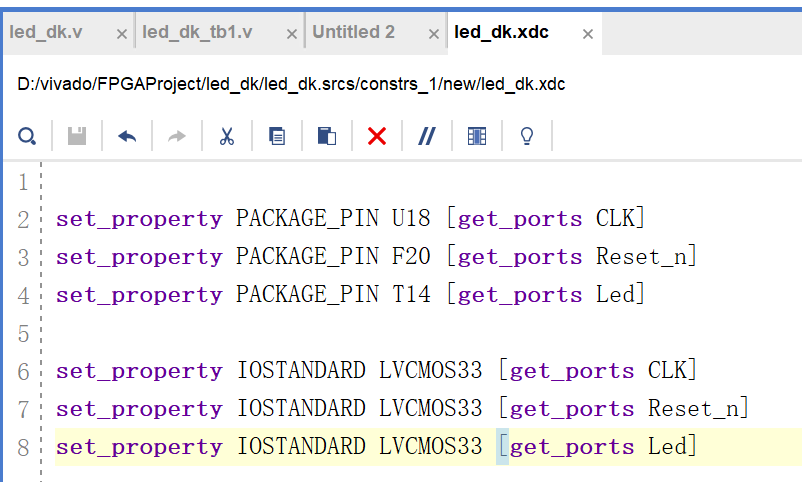

六、约束文件部署

6.1 管脚约束

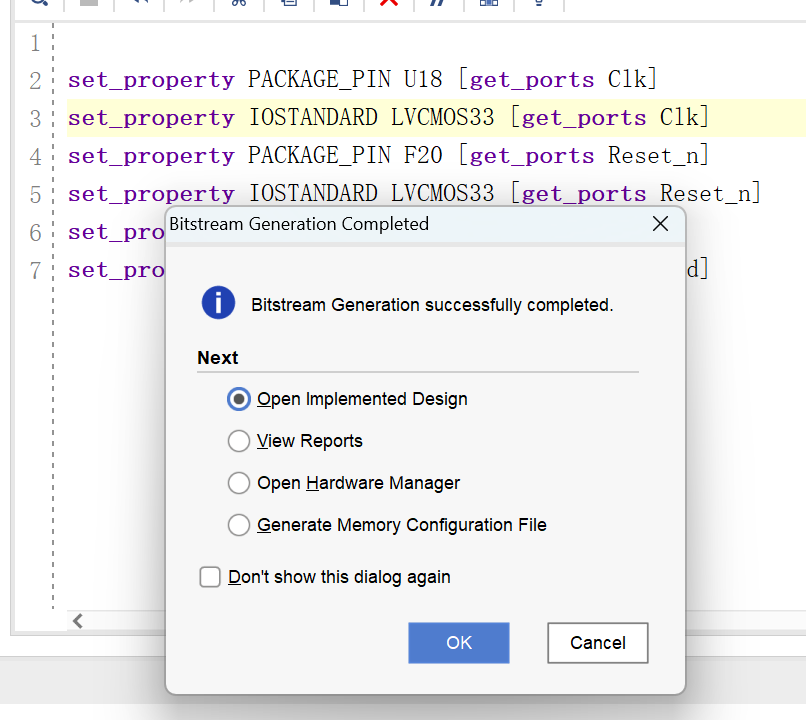

七、Bit 流生成

呈现这个图片,bit流生成成功。

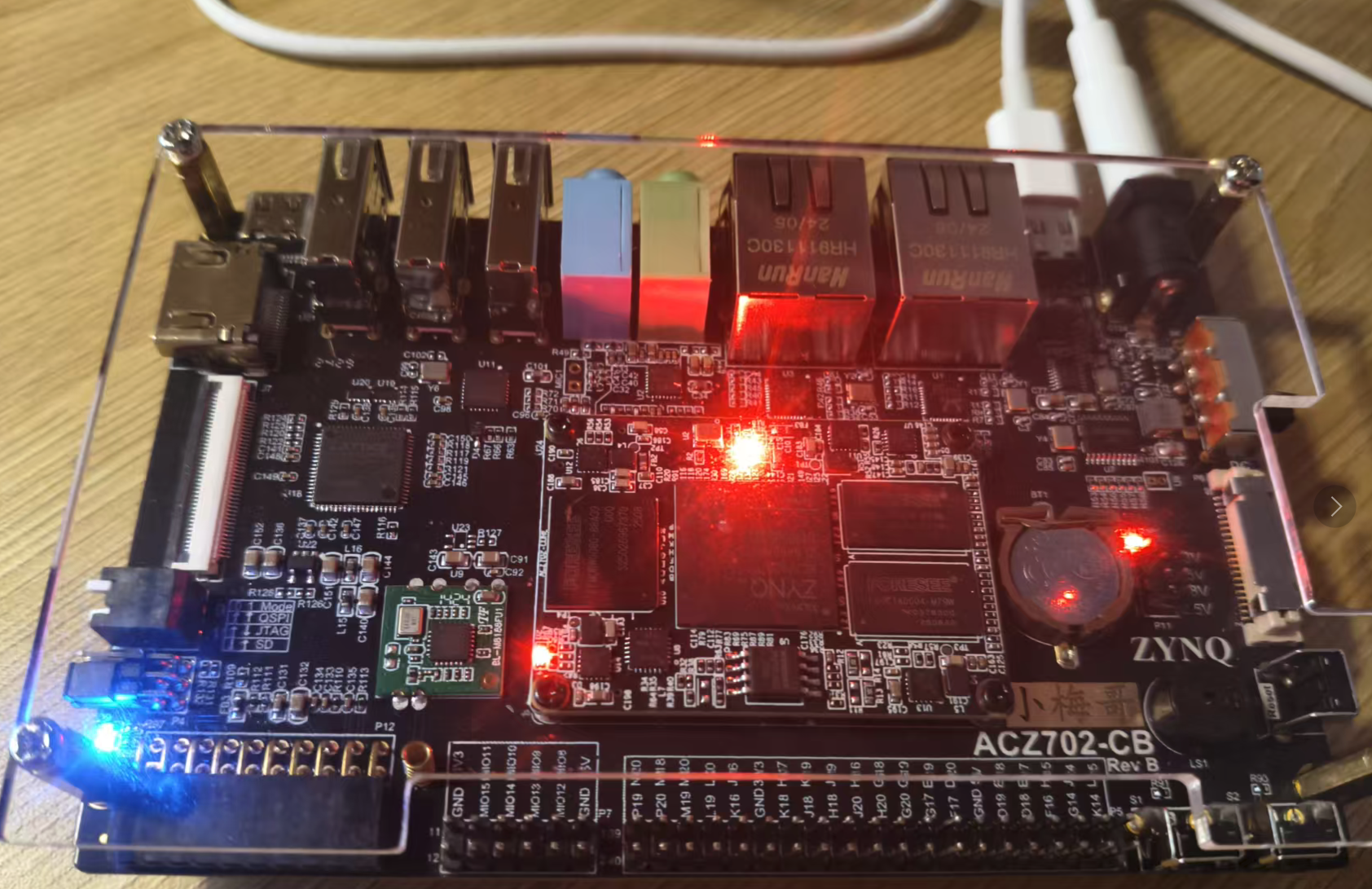

八、下载验证

Program 完成后,可以看到 LED0 每间隔 1s 亮灭翻转一次。实验证明,设

计达到预期。

浙公网安备 33010602011771号

浙公网安备 33010602011771号