lmk04828 使用记录

锁相环(PLL)原理

工作原理就是一个负反馈电路,鉴相器接收一个参考时钟(FREF)和 OSC 生成的时钟信号,比较两者的相位差,然后输出一个电压,经过一个滤波器,去控制OSC的生成频率,这样OSC生成的频率就会和FREF一样了。

用到鉴相器是因为如果频率相等则相位差恒定。

图片里的OSC可能不太准确,应该是VCO,即压控振荡器,可以通过电压调整输出频率。还有VCXO,VCTCXO,VC就是压控,TC就是温控,X代表石英晶体,O 就是(OSCillator) 振荡器。

lmk 04282x 几种模式

手册的9.4节: 9.4 Device Functional Modes

没有列完,只写了我看了的两个模式,看懂了怎么分析看其他的应该问题不大。

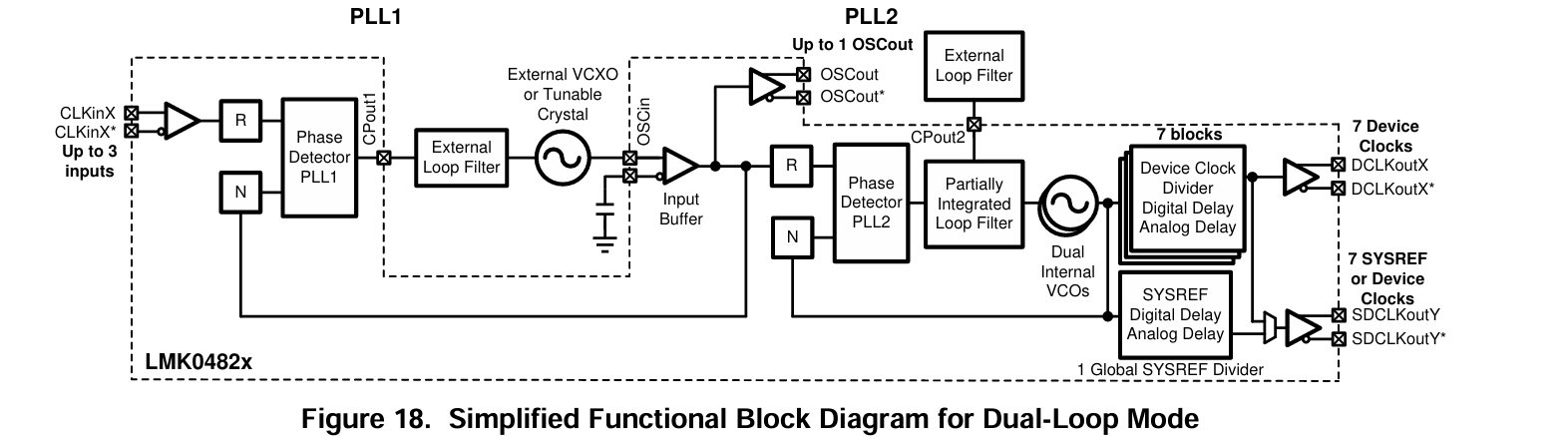

双环模式(Dual-loop)

PLL1 + PLL2 一起用,抖动最小。

这种模式下需要一个外部的VCXO,参考时钟输入给PLL1的鉴相器,鉴相器的输出到外部VCXO,同时VCXO的输出会反馈到PLL1鉴相器,也就是说外部VCXO加上鉴相器这些电路组成了PLL1,然后PLL1输出作为PLL2的参考时钟(输入到鉴相器的时钟)。

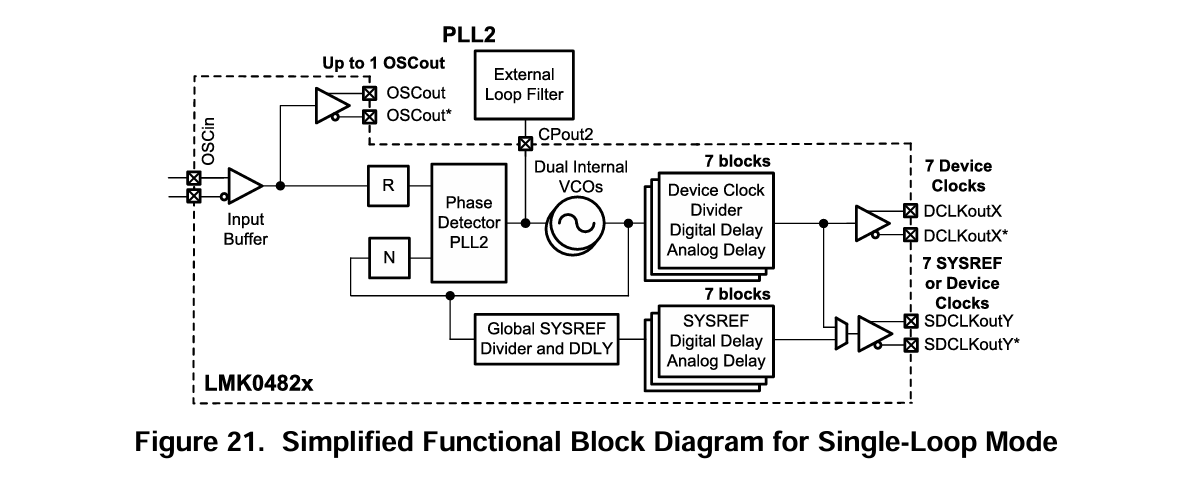

单环模式(Single-loop)

关闭 PLL1,只用 PLL2 当普通单 PLL 时钟发生器。

这个就很简单了,OSCin输入一个参考时钟给PLL2,内部VCO就能产生时钟信号了。就是一个PLL的结构。

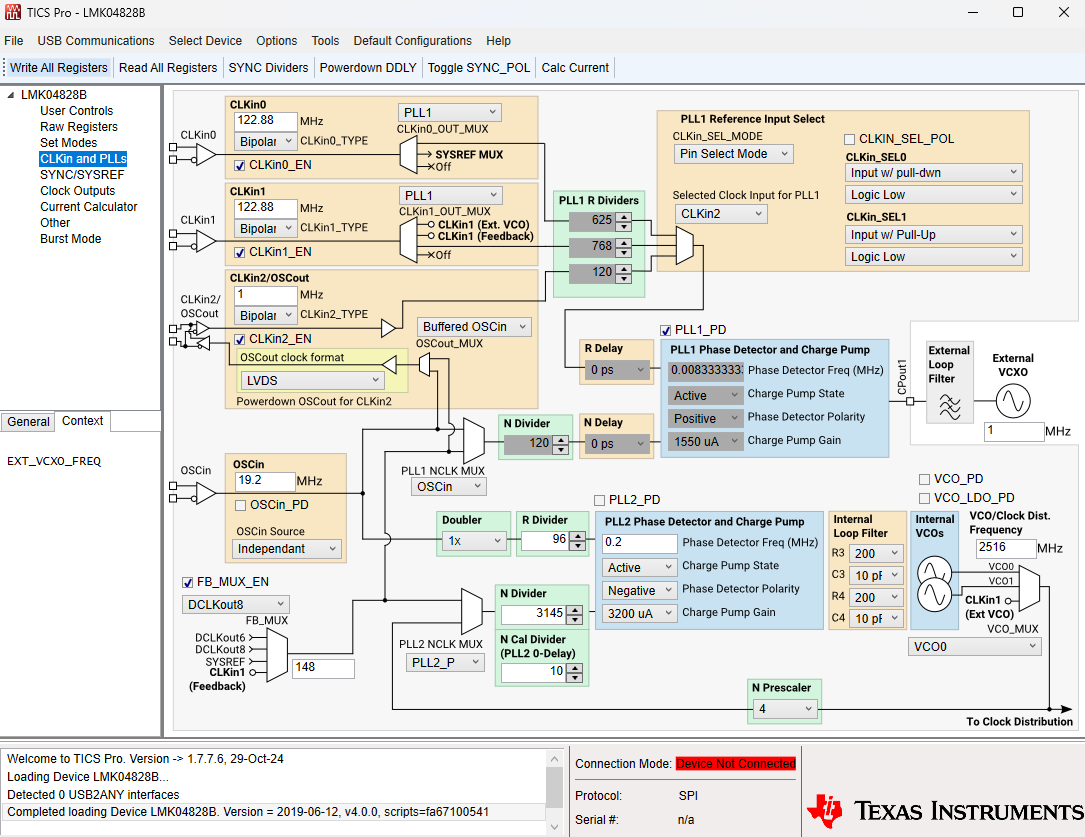

配置软件

上面的图能看到,有很多分频倍频器可以设置,然后得到我们想要的时钟。我们通过官方的配置软件可以完成配置,导出寄存器值表。

首先搞清楚用什么模式,左边有个 set modes 按钮,

然后设置clkin and plls, 配置输入时钟和PLL1和PLL2的输出。

然后设置Clock outputs,配置输出时钟,输出时钟都是 PLL2输出分频得到的。

其他的看需求去设置。

参考文件

LMK0482x Ultra Low-Noise JESD204B Compliant Clock Jitter Cleaner With Dual Loop PLLs

浙公网安备 33010602011771号

浙公网安备 33010602011771号