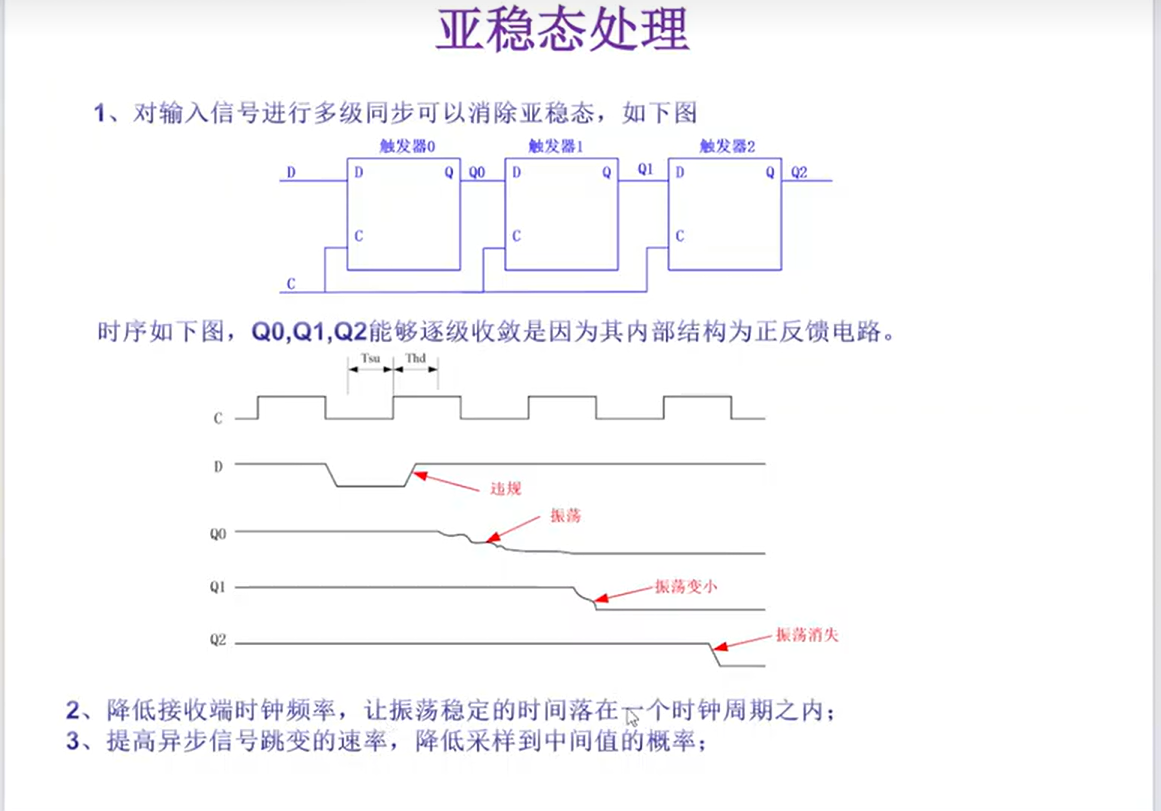

FPGA打拍消除亚稳态原理

先说结论

先介绍下亚稳态的概念: 信号不是一个标准电平(0或1),无法识别。

初次接触到打两拍这个方法的时候就不理解,第一个寄存器已经采到错误值了,第二个寄存器再采这个错误值怎么就对了呢?

其实上面这个想法有个误区:我误以为第一个采到亚稳态信号的寄存器会把亚稳态的信号直接误判为0或1。

实际上这也是要时间的,触发器的内部结构有一个正反馈震荡电路,采集到的亚稳态信号会逐渐收敛。 并且收敛时间是固定的。所以等一会儿亚稳态就消失了。

再来理解为什么打怕能消除亚稳态,众所周知,使用寄存器就会延迟一拍,所以打拍其实是等。

所以,打拍的原理和方法2的原理是一样的,就恩等。方法3就不说了,意思就是说信号质量越好越不容易出现亚稳态。

相关概念

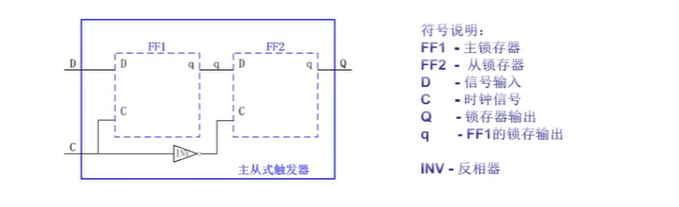

触发器结构

出发器由两个锁存器实现。

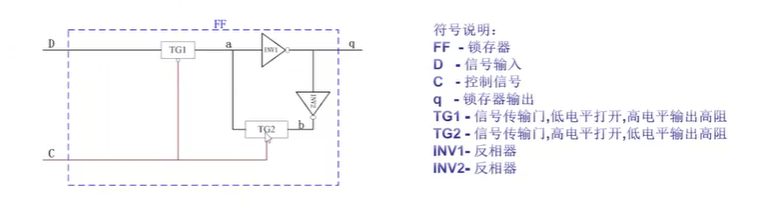

锁存器结构

建立时间

在上升沿来临之前,D传播到q需要的时间

保持时间

上升沿来到时,TG2先打开,再关闭TG1,这期间,q由D和b两个一起驱动,所以再TG1关闭隔绝D之前,D的波动会传播到q。

浙公网安备 33010602011771号

浙公网安备 33010602011771号