(笔记)Vivado操作之时序约束介绍

一、前言

任何一个FPGA工程都需要设置相关的时序约束,下面将介绍Vivado中如何进行时序约束操作以及各种约束的使用方法。

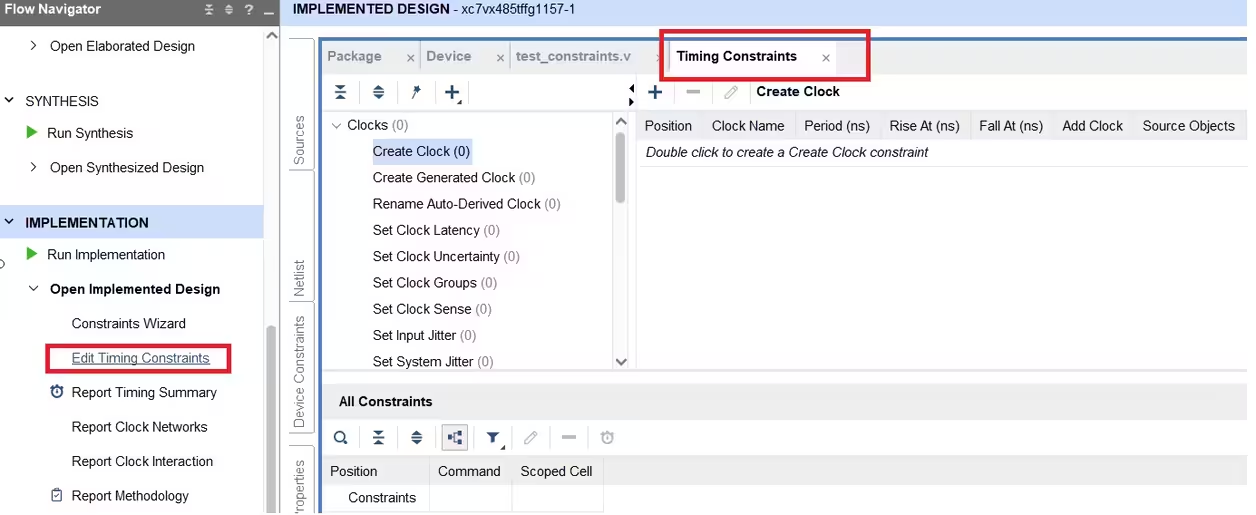

二、时序约束界面

在一个工程运行到IMPLEMENTATION后,进入到左侧的Flow Navigator窗口,点击IMPLEMENTION下的Edit Constraints,右侧会出现Timing Constraints窗口,即可添加时序约束

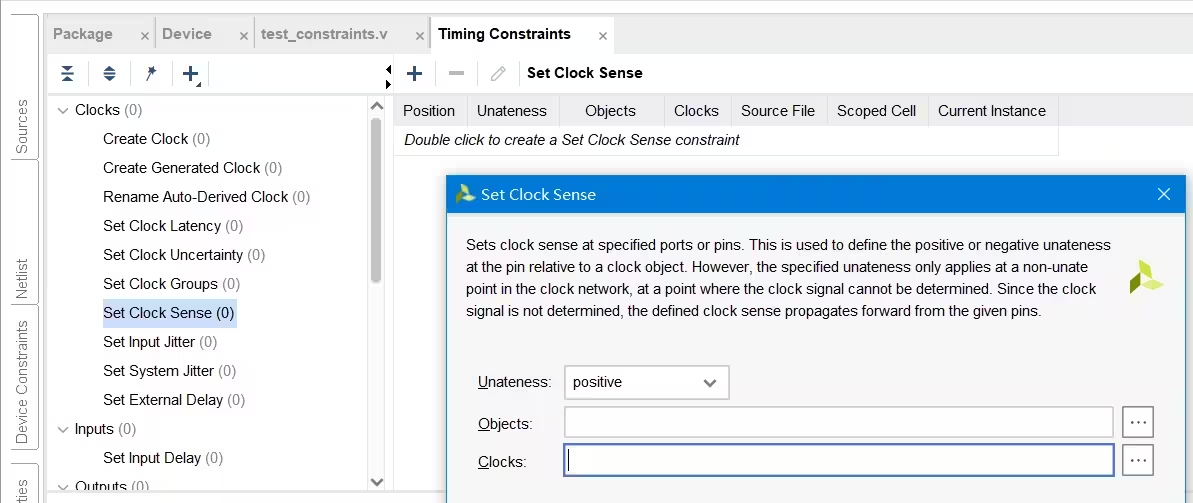

左侧Clocks目录下点击任意一个时钟类型进行选定,双击右侧空白处将弹出对应类型时钟约束设置界面,下图示例为Set Clock Sense的设置

也可使用Constraints Wizard,将弹出设置时序约束的引导窗口。

三、时序约束介绍

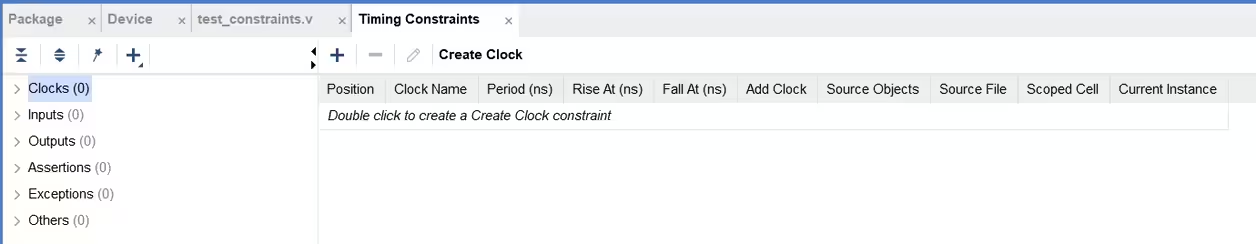

通过时序约束界面添加设置中可看到,时序约束可分为6大类:Clocks,Inputs,Outputs,Assertions,Exceptions,Others,本文主要介绍其中常用的时序约束

- Clocks:主要关于时钟源相关的约束;

- Inputs/Outputs:设置外部芯片到FPGA的时钟源输入延时,FPGA信号输出到外部芯片的输出延时

- Assertions:设置数据路径检查以及总线偏斜

- Exceptions:设置一些时序路径例外的约束

- Others:除上述几类之外的时钟约束

3.1 Clocks

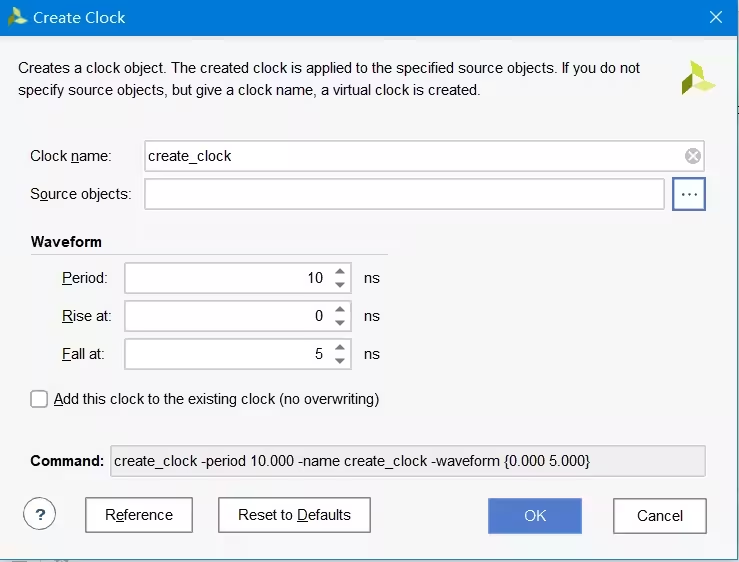

3.1.1 Create Clock

Create Clock约束为创建时钟源信号,即外部传入到FPGA的时钟信号,Clock name即为设置时钟名称,Waveform中Period为时钟周期,Rise at和Fall at为时钟上升沿,下降沿的时钟位置,Fall at减去Rise at即为时钟信号的占空比。

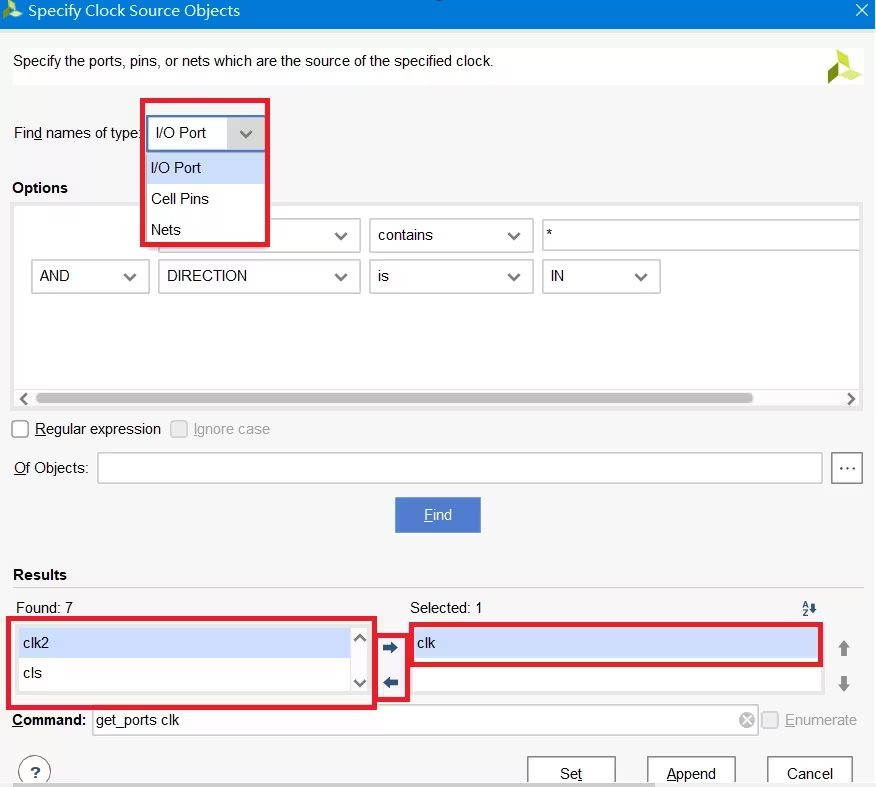

Source Objects是将该时钟信号约束的对象,可设置到I/O Port,Cell pins,Nets上,对于设置的对象,可在Options上输入搜查条件查找,Results中展示搜索结果,在Results中选定对象,点击右移图标即移入到Selected及时选定了约束对象

设定后同时在Create Clock窗口的Command将显示自动生成对应的约束命令,再保存生成的文件。

在Constraints中可以看到生成的约束文件time_constraints.xdc,文件内容为约束命令

3.1.2 Create Generated Clock(生成时钟)

生成时钟Generated Clock是在以Create Clock中的时钟为主时钟,生成新的时钟,优点是主时钟变化时,Generated Clock自动同步更新,一般是在时钟频率很低且扇出小时才建议使用生成时钟,原因是生成时钟一般由组合逻辑和时序逻辑生成,相对质量差。生成可以是主时钟的分频时钟或者倍频时钟,占空比可以设置。如下图

也可以通过时钟边沿来设置生成时钟,设置界面如下图

对应的命令为create_generated_clock -name gen_clk -source [get_pins clk_IBUF_BUFG_inst/O] -edges {1 3 4} -edge_shift {2.0 0.0 1.0} -add -master_clock [get_clocks "*"] [get_pins {shiftr_reg[13]/C}]

含义解释:-edge {1,3,4}即生成时钟的第1个上升沿位置,第1个下降沿位置,第2个上升沿位置分别对应源时钟的第1,3,4个变化边沿,-edge_shift的3个值为在源时钟基础上的偏移。假设源时钟clk周期为10ns,占空比为50%,从0时刻开始,统计了边沿变化的数目,-edge {1,3,4}如中间波形所示,对应了clk第1,3,4的边沿;Generate clk即为各个边沿的偏移值,分别是0+2,10+0,15+1,即为Generate clk的波形。

3.1.3 Set Clock Uncertainty

Set Clock Uncertainty可以设置时钟网络的Skew,Clock Skew为时钟偏斜,表示同一时钟或生成时钟到达不同触发器存在时差,Uncertainty applies to 可设置setup,hold,setup/hold;simple uncertainty可以设置到不同的Objects,设置Objects对象可以是Clocks,Cell pins,I/O Ports;Interclock uncertainty只能设置Clocks间的skew

设置格式如下图所示

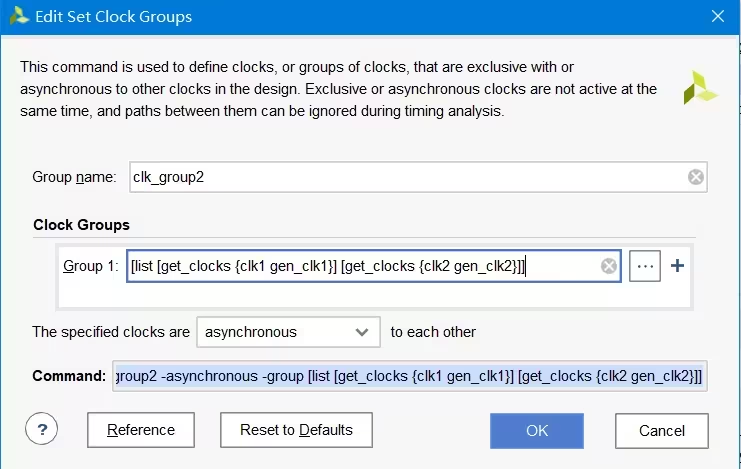

3.1.4 Set Clock Groups

Vivado在进行时序分析时,默认所有时钟都是同步的,工程实际使用中,会存在一些时钟为异步时钟,此时当做同步时钟进行分析导致结果不准确,通过设置时钟组可以让工具不进行时序分析,下图中设置{clk1 gen_clk1}和{clk2 gen_clk2}为异步时钟组,组间的任何两个时钟间都不会进行时序分析。

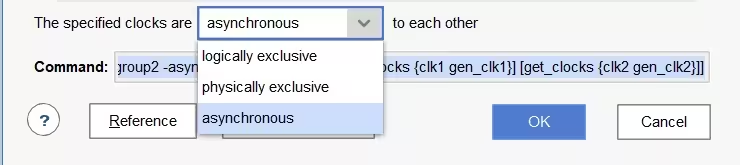

同时,除了选项asynchronous,也可以设置为logically exclusive和physically exclusive,

区别是如果两组时钟不能同时存在,则使用-physically exclusive,如果是两组时钟逻辑分析上不存在交互路径,则使用-logically exclusive

3.1.5 Set Input Delay/Set output Delay

设置端口或者pin上时钟的输入或输出时延值.

3.2 Exceptions

添加时序例外路径约束可减少编译时间,降低约束的调试难度以及阻止工具优化掉一些需要的信号,常用的时序例外约束Set minimum Delay/Set maximum Delay,Set Multicycle Path,Set False Path.

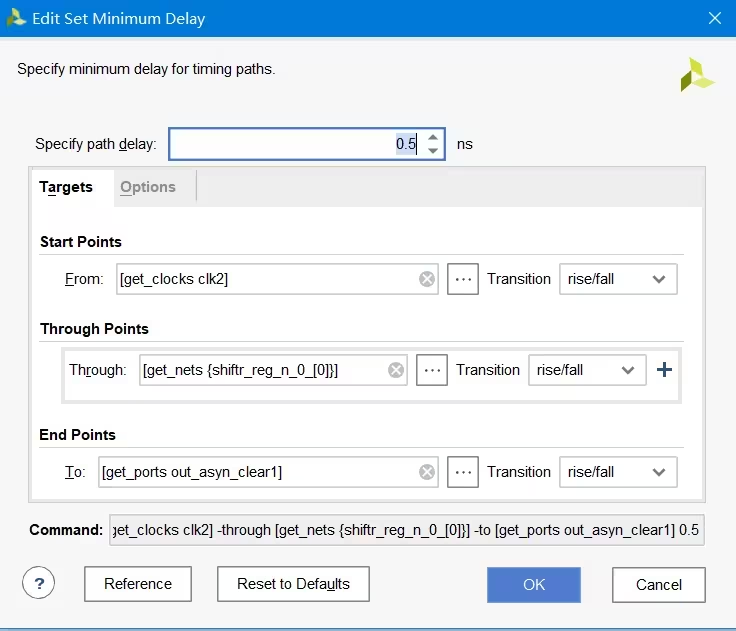

3.2.1 Set minimum Delay/Set maximum Delay

设置某些路径的最大时延或最小时延,对象可以是Cell pins,Cells,clocks,I/O port,通常使用场景如下:

1)对某些时序路径实施过约束

2)代替多周期路径约束

3)对异步跨时钟域进行set_max_

设定path delay值后,设置起点start points,中间路径Through points,终点End Points即可

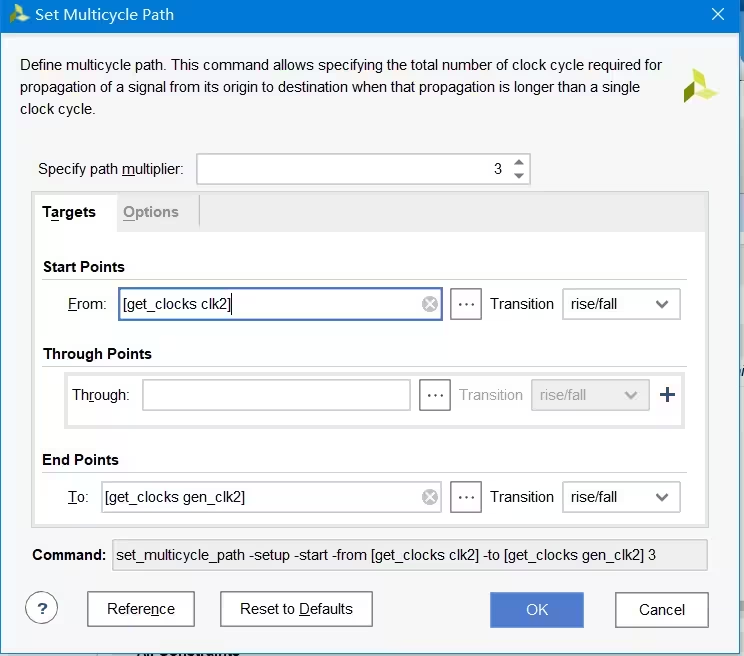

3.2.2 Set Multicycle Path

设计中存在一些发起沿到捕获沿的周期非单个周期,如果按单个周期进行分析,可能出现时序违例的情况,也不符合实际工程需求,Specify path multiplier设置周期数,然后再设置起点和终点

其他Options中参数含义,-setup表示建立时间需要的周期,-hold表示保持时间需要回调的时钟周期个数,-end表示已目的时钟作为基准周期,-start表示以源时钟作为基准周期

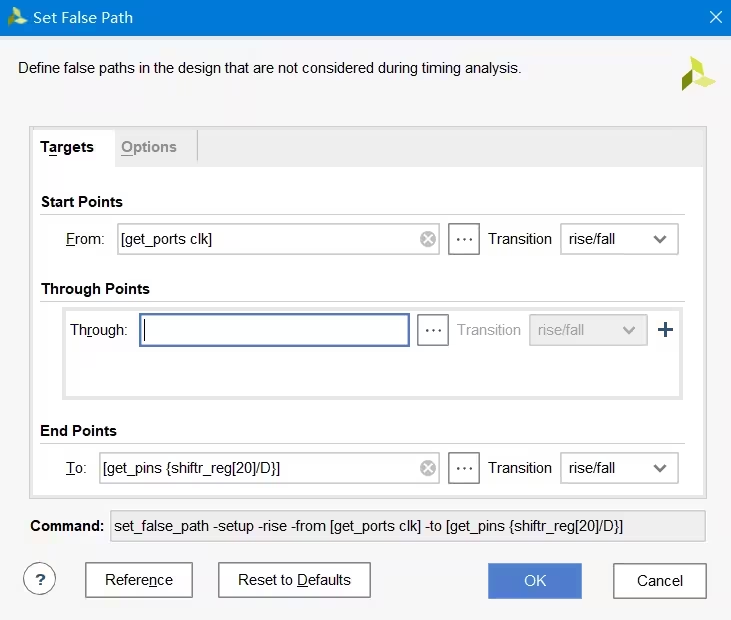

3.2.3 Set False Path

Set False Path的作用类似Set Clock Group,对于设置了该约束的路径不会进行时序分析,主要是针对一些路径的电路功能不会发生或者路径不需要时序约束;

常见的一些可设置False的路径:

1)通过双触发器同步的跨时钟域路径

2)只在上电时工作的寄存器对应的电路

3)异步复位电路

4)只在测试时使用的路径

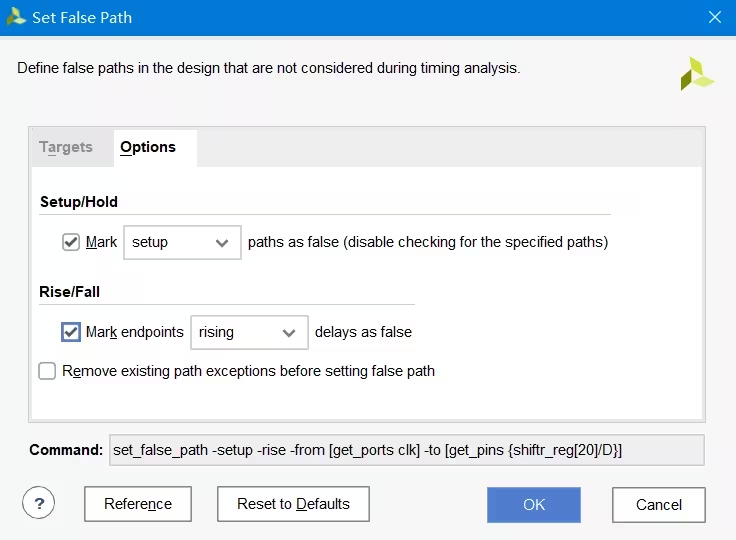

设置界面如下图,设定起点终点,也可添加中间路径,

Options中可设置Setup/Hold,Rise/Fall

四、参考

1、书籍《Vivado 从此开始》 高亚军

原文来源: https://www.bilibili.com/read/cv22861422/

posted on 2024-03-08 14:55 tdyizhen1314 阅读(5442) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号